數字邏輯設計的冗余與檢錯糾錯

李仲秋

(長沙航空職業技術學院,湖南 長沙 410124)

1 數字邏輯電路的特點

在數字邏輯中,不方便采用如同存儲器中使用的編解碼技術。原因之一是數據的位置分散,不方便統一的編碼,如最常用的線性分組碼,被編碼的位數越多,編碼的效率越高,但如果數據分散,不容易進行高效率統一編碼,而且使面積和功耗變得難以接受。如果強行提高被編碼的數據位數,可能涉及到對原邏輯電路的改變,至少是對其布局布線的改變,這就影響原設計性能。另一原因是數據使用不同步,不方便解碼(和檢錯),很可能在某一周期,只需要對一組寄存器中的某一個數據進行使用,(比如,[k+r, k]分組碼,這組k個寄存器一組被編碼,產生r個監督位),k位中其他的k-1位在這個周期并無使用價值,那么為了使用這一位數據,需要在這周期中對全部的k+r位進行校驗計算,這樣帶來的硬件性能降低就會到不可容忍的程度。

2 復雜時序邏輯電路檢錯的難點

1)輸入和輸出的映射關系不明確

在復雜的時序數字邏輯中,在某一時刻來看,總輸入和總輸出的映射關系不明確。數據在關鍵路徑上的傳播所經歷的空間跨度和時間跨度都可能很大,有可能當前的輸出,是由之前多個周期的輸入所決定的。這種不明確,使得檢錯需要的信息必須從中間的寄存器節點中去得到,加大了檢錯的成本。

2)邏輯關系交織

數據受到的干擾源不確定,錯誤產生后,往下傳播對后一級(結構上,邏輯上)電路造成的影響也難以確定。一般需要對于關鍵數據進行保護(比如狀態機的狀態標志,處理器中的指令單元和運算單元),但是這樣的保護,顯然是不夠的。例如,有限狀態機中的狀態跳轉是由現有的狀態和輸入信號共同決定的,如果周圍電路的輸入中有錯誤,僅僅保護了狀態機的標志位,狀態機的跳轉還是會發生錯誤。值得指出的是,有的電路有反饋邏輯,錯誤的影響更難以捉摸。

3 冗余與可靠性

數字邏輯設計可靠性的提高就是電路系統容錯能力的提高,各種類型的容錯設計方法都涉及到一定的冗余,根據冗余的類型可分為空間冗余、時間冗余、信息冗余等。

空間冗余(Space Redundancy),主要是硬件多模冗余。 三模冗余(TMR)、二模冗余(DMR),以及它們的改進版本,都屬于這個范疇。

TMR通過對多路冗余結果進行表決,實現檢糾錯。TMR的改進版本幾乎都是各種“局部三模冗余”(partial TMR),這些方法對電路中的某一部分進行TMR,在可接受的容錯能力范圍內盡量減少面積占用和電路功耗。局部三模冗余的關鍵,在于如何選取需要冗余涉及的子電路部分,有各種確定子電路是否進行冗余的優先級的方法,比如有的以信號的使用頻率作為選擇的準繩,使用頻率高的單元優先進行冗余;有的以電路的邏輯結構特點作為準繩,將存在反饋的子電路優先進行冗余(考慮到反饋電路可能造成錯誤的累積)。

DMR能夠偵錯,但不能糾錯,這是DMR的特點,但有些改進的DMR,局部融入TMR,能夠一定程度上實現糾錯時間冗余(Time Redundancy),這種方法的硬件占用相比于空間冗余較小,涉及到對于相關信號在多個時間點的采樣[1]。時間冗余因為需要新的采樣時鐘,甚至需要利用傳輸線的延時特性,所以實施起來難度較大,一般會對性能有負面影響[2]。

信息冗余(information redundancy)的范疇較為廣泛,凡是涉及到編碼技術的檢糾錯EDC( error detection and correction)技術,都屬于信息冗余[3]。

4 檢錯糾錯

如果將一個可靠性設計劃分為兩部分,可分為功能部分和檢糾錯部分。

“功能部分”是指實現一個應用本身需要的電路,在沒有SEU/SET情況下,功能部分能正常的完成所需的功能。

“檢糾錯部分”是指為了消除異常的翻轉,而進行的容錯設計部分。可以肯定地說,檢糾錯電路的輸入信號都來自功能部分。

根據功能部分和檢糾錯部分兩者的邏輯關系(結構關系),分為侵入方法和非侵入方法[4]。

“非侵入”的加固方法一般是僅對功能部分的輸入和輸出進行并行的數據分析,實現檢糾錯的目的。檢錯電路不干參與功能部分的關鍵路徑,因此原有的功能在性能上沒有負面影響。

“侵入”的方法將檢糾錯電路和原電路融合到一起,被加固的電路有時為了方便加入檢錯結構,甚至需要重新綜合(re-synthesizing),對于性能要求高的電路的加固,侵入的方法不適用(如cores, macrocells,handcrafted designs ,legacy designs)。

一般的應用場合都要求“在線檢糾錯/ 實時檢糾錯”,所以功能部分的信號必須實時的作為檢糾錯部分的輸入,檢糾錯電路需要不時的對關心的一些信號做檢查來確定是否有異常的情況。如此一來,檢錯帶來的額外的功耗就不可避免,檢錯電路本身成為硬件上的冗余,也不可避免。甚至可以說,沒有硬件和功耗上的冗余,就無法檢錯和糾錯。

5 一種改進的單元加固型容錯觸發器結構設計

從總體上看,可靠性的設計有兩個努力的方向,一個方向是努力減少翻轉的產生,另一個是在翻轉發生后控制它向下一級電路的傳播,使其不影響最終的功能實現。

如果將工藝改進和電磁兼容設計歸為一條路(防錯),容錯設計歸為另一條路(糾錯),那么還有一些在獨立的功能單元內部實施加固,實現抗干擾的單元,可以稱之為中間路線。

單元可以是指鎖存器、寄存器,也可以是復雜的加法單元、乘法單元,有的還是PLA邏輯陣列單元。這類容錯的方法是介于前面提到的兩個方向之間,但更接近前者的思路,將已發生的錯誤翻轉限制在單元的內部,相鄰的單元感覺不到異常的存在。

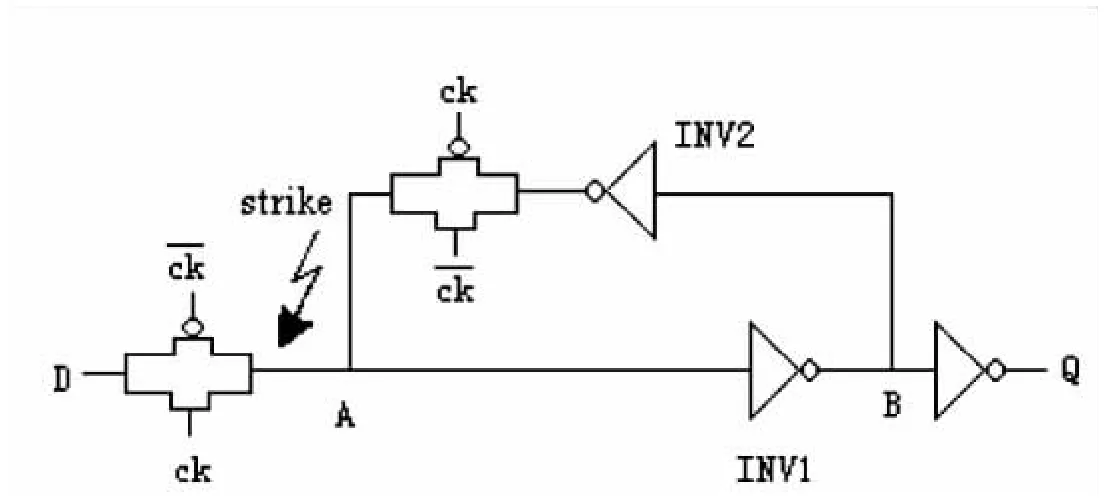

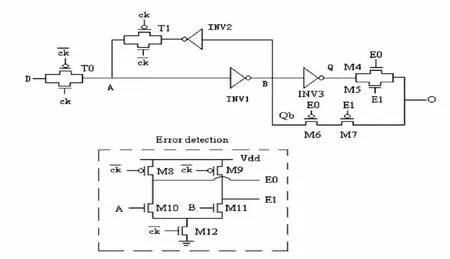

普通的觸發器結構如圖1所示,該結構未加固,容易受到外來粒子的干擾產生翻轉。改進的單元加固型觸發器結構如圖2所示。

圖2中提出的對普通的觸發器單元改進的設計,是一種抗干擾的觸發器設計[5]。這種觸發器在干擾下會發生翻轉,但這種錯誤在觸發器內部通過某些方法被屏蔽掉,其輸出是對的(至少在下一級電路的采樣時刻是對的)。

時鐘沿處發生的翻轉,默認為正常的翻轉,其他時刻的翻轉,被認為是異常的翻轉。在模擬設計中,這種檢測可以通過電壓,電流的檢測電路來實現。

不過這種思路也存在上面提到的問題,如果時鐘沿處有擾動,那么將被誤認為是一次正常翻轉。

圖1 普通的觸發器結構

圖2 改進的單元加固型觸發器結構

改進后的觸發器,在輸出端(B)加入M4、M5、 M6、M7,檢糾錯電路受到粒子撞擊,發生異常的翻轉的時候,產生M4、M5、 M6、M7的柵極電壓E0、E1。雖然A、B處的邏輯電平發生了錯誤,但是由于M4-M7四個管子的作用,能使得輸出端維持正確的輸出值。

[1] Michael Nicolaidis.“Time Redundancy Based Soft-Error Tolerance to Rescue Nanometer Technologies”[A]. 17th Proceedings. VLSI Test Symposium[C]. 1999 IEEE. 86-94.

[2] V. Prasanth, Virendra Singh, Rubin A. Parekhji:“Robust detection of soft errors using delayed capture methodology”[A]. 16th International On-Line Testing Symposium[C]. 2010 IEEE. 277-282.

[3] K.Nepal.“Using implications for online error detection”[A]. International test conference[C]. 2008 IEEE.

[4] Avijit.“Combinational logic circuit protection using customized error detecting and correcting codes”[A]. 9th international symposium on quality electronic design[C]. 2008 IEEE.

[5] Xiaoxuan She.“SEU tolerant latch based on error detection”[A]. IEEE transactions on nuclear science[C]. 2012.