一種應用于CAN 收發器的寬輸入范圍的遲滯比較器設計*

馮世勤,馮全源

(西南交通大學 微電子研究所,四川 成都 611756)

0 引言

CAN 總線作為一種現場總線,因為其可靠安全、實時通信和靈活控制的特點,在工程實踐中廣受工程師的歡迎[1]。CAN 總線整體由物理總線、收發器和控制單元三部分構成。CAN 收發器是負責MCU 或DSP 等CAN 控制單元和物理總線之間信號傳遞的結構[2]。CAN 總線上的信號CANH 和CANL 是擺幅為-12~12 V 的差分電壓信號,而CAN 控制單元僅識別數字信號,所以CAN 收發器中的比較器需要將共模范圍為-12~12 V 的模擬信號轉化為0~5 V 的串行數字信號。CAN 收發器中比較器的性能對整個網絡系統的安全性、可靠性和電磁兼容性起到了關鍵作用[3]。本文設計的比較器目的就是將總線信號CANH 和CANL 得到的差分信號VID 轉化為數字信號,比較器輸出的遲滯范圍約為108.9 mV。

1 傳統的遲滯比較器

模擬電路常見的結構中,遲滯比較器可以實現模擬信號到數字信號的轉換,還可以降低電源噪聲和外界干擾等因素對輸出的影響,使得電路可以在復雜的環境中使用[4]。傳統內部正反饋遲滯比較器如圖1 所示。

圖1 傳統內部正反饋遲滯比較器

以圖1(a)為例,內部正反饋遲滯比較器基本的工作原理為:電路中有兩條反饋通路,第一條通路是A 點信號由共源極接法的MP1 反向放大回到A 點,屬于串聯電流負反饋;第二條通路是A 點信號由MP2、MP3 兩級放大回到A 點,屬于并聯電壓正反饋。設計時要保證正反饋系數大于負反饋系數,電路整體保持正反饋,這樣電壓傳輸曲線就會呈現出遲滯的特性[5]。

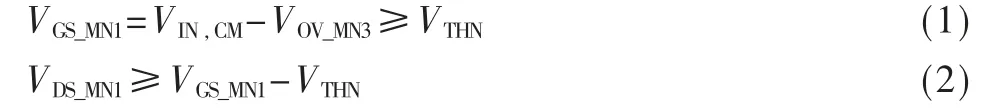

如圖1(a)所示的使用NMOS 作為輸入管的遲滯比較器,使MN1 處在飽和區有:

得到輸入共模范圍為:

由式(3)可知,輸入電壓最低為一個NMOS 過驅動電壓和一個閾值電壓,約為0.9 V。寬長比設置合理的話,輸入共模范圍最高可高于VDD。

但是即使使用PMOS 作為輸入管,如圖1(b)所示,輸入共模范圍為:

由式(4)可知,輸入電平最低可以是負電壓。

文獻[6,7]同時使用NMOS 和PMOS 作為輸入管,當NMOS 輸入管截止的時候,PMOS 輸入管還可以工作,同理PMOS 輸入管截止的時候,NMOS 輸入管還可以工作。這樣可以使比較器獲得軌到軌的輸入共模范圍。

但是以上結構仍然不能處理超過電源范圍的電壓,因此本文采取的方法是將-12~12 V 先轉化為0~5 V 的電壓,再進行比較。

2 本文提出的比較器結構

2.1 比較器整體架構

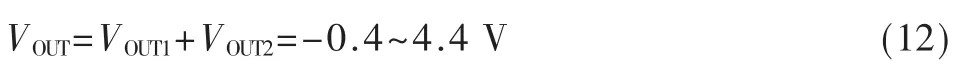

本文提出的比較器結構共分為三部分,如圖2 所示。先是利用電阻將輸入的差分電壓和電源電壓線性疊加,得到-0.4~4.4 V 的電壓;第二級利用全差分運放鉗位,穩定電壓,這樣就實現差模輸入到共模輸出的線性轉換;有R0=R1=R2=R3,理想運放虛斷,應用基爾霍夫電流定律可以得到:

圖2 本文提出的比較器的整體架構圖

因而穩定后的輸出電壓為:

又根據運放虛短的特性,Vi+=Vi-,因此:

從上式可知:差分信號VID并沒有變化,只是承載的電平變大,可以增強差分信號對外界干擾的抵抗能力,變得更加穩定[8]。

最后一級是對尾電流進行溫度補償的遲滯比較器,比較得出數字信號。

2.2 電平線性轉化

第一個模塊實現的功能是將總線上的差分信號從-12~12 V 的電平轉化到0~5 V 這一后級電路可以處理的電平范圍內。

如圖3 所示,采用電阻分壓的方法將電源電壓和輸入信號進行線性疊加得到-0.4~4.4 V 的電壓。在圖1中,將其他部分電路視為一個負載,加上后級負載,這個電壓可能會有微小的變化,但是負載變化對VH和VL影響一樣,差分信號VH-VL基本消除了負載的影響。

圖3 VIN 線性轉化

設計有R0=R2,R1=2R0,利用疊加定理計算,可以得到如下結果。

令VIN=0,有:

令VDD=0,有:

所以得出:

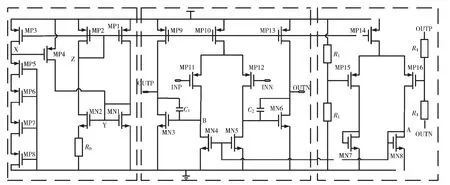

2.3 運放以及偏置電路

全差分運放相比單端輸出的運放,具有輸出擺幅大、共模抑制比好、能夠有效抑制偶次諧波的優點[9];再加上運放需要高增益以保證高精度,因此本文設計的運放為采用密勒補償的全差分兩級運放。第一級為電流源做負載的差分輸入級,采用PMOS 作為輸入管。而使用電流源做負載可以提高電路的PSRR,同時可以提高增益[10]。只考慮溝道長度調制效應,且為簡便計算,將NMOS 和PMOS 輸出阻抗簡化為rON和rOP,輸入級增益為:

第二級為電流源做負載的共源極,進一步增大了增益,第二級增益為:

運放總的直流增益為:

為解決兩級運放的穩定性問題,引入密勒補償。密勒補償不僅降低了所需的電容值,還帶來了“極點分裂”效應,就是使兩級間的極點向原點移動,使輸出極點向遠離原點的方向移動,提高了運放的相位裕度[11]。

全差分運放的共模輸出電壓不能通過差分信號的負反饋來控制,因此需要設計共模反饋電路保證共模點鉗位在電源電壓的一半即2.5 V。因為在高增益運算放大器中,頂部和底部電流源存在的隨機失配會導致共模電平顯著的變化,這種現象可能會導致運放的失效,因而需要采用共模反饋技術穩定運放的共模點[12]。先采用電阻分壓的方法得到電源電壓的一半即2.5 V 的參考電壓,再用電阻分壓的方法得到運放輸出共模電壓和參考電壓進行比較,輸出共模點大于2.5 V,MP16 所在支路電流減小,將二極管接法的MN8 視為恒定負載,負載上的壓降減小,A 點電壓減小,所以電流源MN4、MN5柵壓下降,各自電流減小,等效阻抗rON增大,B 點電壓增加,因為共源極增益為負,OUTP 和OUTN 電壓減小。輸出共模點小于2.5 V 的情況類似。這樣就實現了通過共模反饋調節輸出的共模電平,保證運放工作在線性區域[13]。

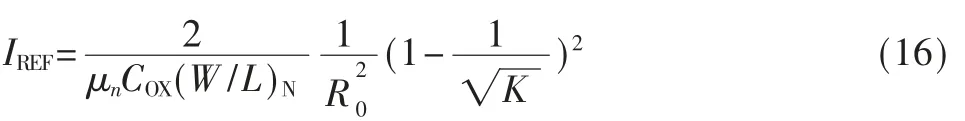

K為MN2與MN1寬長之比,(W/L)N是MN1的寬長比,與電源無關的偏置電流為:

啟動電路可以使偏置電路擺脫零偏置點,進入正常工作狀態[14]。本文的啟動電路的工作原理是:電路未上電時,MP3 未開啟,X 點為0,MP4 開啟,慢慢拉高Y 點電位,MN1、MN2 開啟,拉高了Z 點電位,從而開啟了MP1、MP2,進一步開啟了MP3,MP5~MP8 為二級管接法,因此X 點電位慢慢地拉高,將MP4 關斷,實現了降低功耗的目的。

圖4 本文采用運放的結構

2.4 簡單溫度補償的遲滯比較器

如圖5 所示,本文采用的遲滯比較器為兩級,第一級和圖1(a)所示輸入級一樣,使得電路整體呈現正反饋,第二級為電流源做負載的共源極放大電路的輸出級,提供合理的輸出擺幅和輸出阻抗。偏置電路和運放中的類似,區別在于做了簡單的溫度補償,采用R0、R1兩個溫度系數相反的電阻,減小了溫度對偏置電流的影響,使得遲滯比較器中MN4 提供的尾電流受溫度變化影響較小,從而補償了比較器的遲滯范圍。

圖5 本文采用遲滯比較器的結構

3 仿真結果及分析

基于VIS 0.4 μm BCD 工藝,使用Hspice 對電路性能進行了仿真驗證。

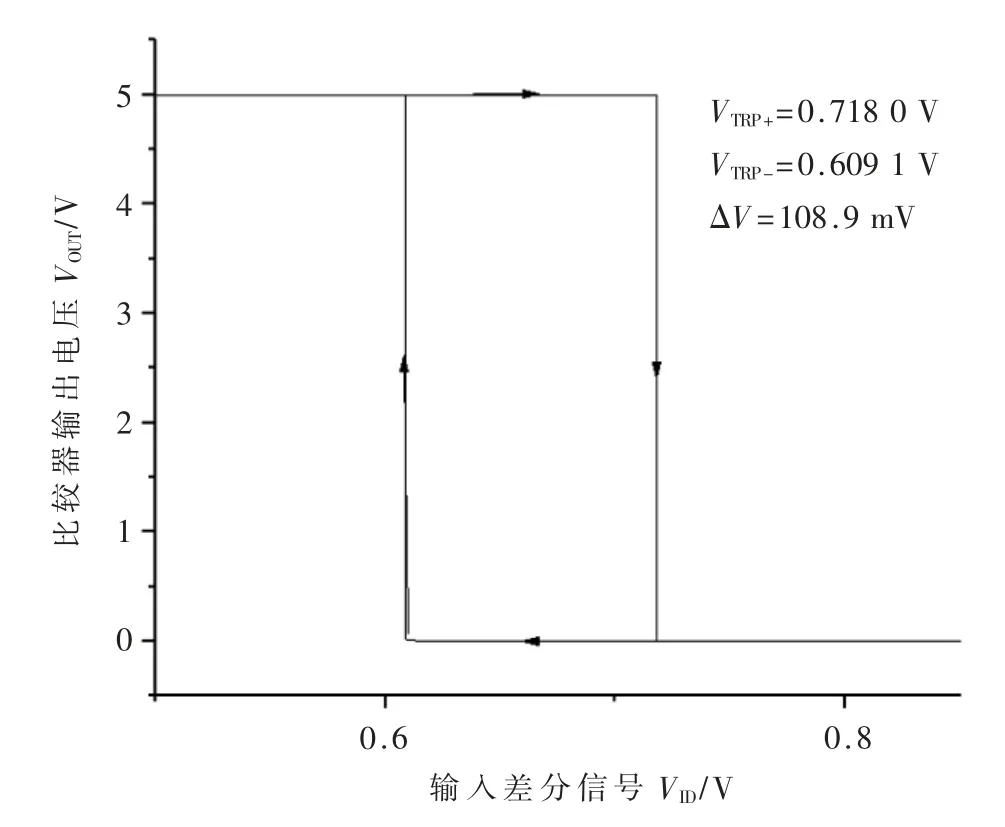

為了檢驗電路遲滯特性,首先通過直流仿真查看常溫(即25 ℃),TT 工藝角下的遲滯曲線,如圖6 所示,測量翻轉閾值電壓,可計算得到遲滯門限電壓為108.9 mV。

圖6 本文設計的比較器的遲滯特性曲線

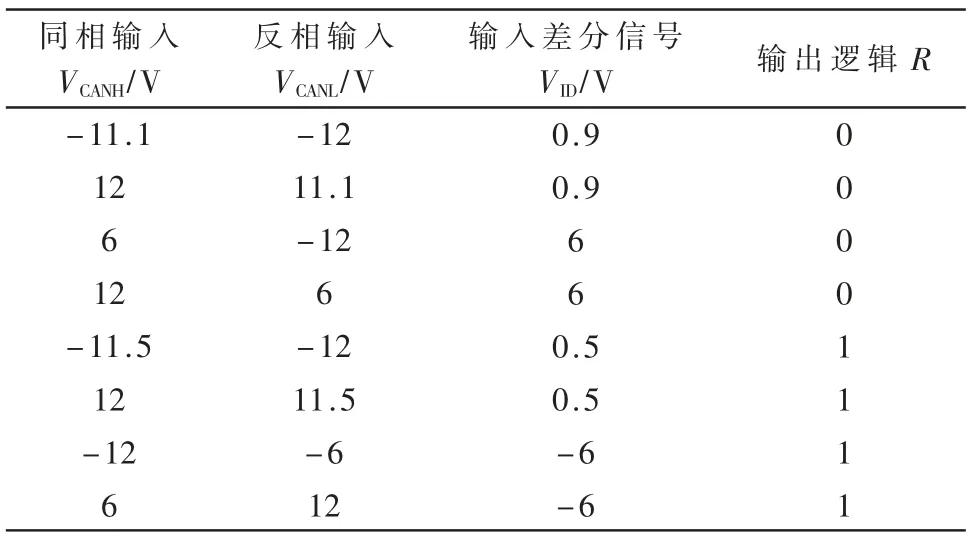

在電源電壓5 V,溫度為25 ℃下,進行瞬態仿真,表1展示了輸入輸出電壓,說明本文所設計的比較器正確地將差分信號轉化為數字信號。

表1 比較器邏輯功能仿真結果

TT 工藝角下,直流仿真-40 ℃~125 ℃內多個溫度節點下的遲滯電壓,擬合得到如圖7 所示的曲線。

圖7 遲滯門限電壓隨溫度的變化

文獻[15]設計的遲滯比較器的遲滯電壓在0~85 ℃范圍內溫度系數為0.11 mV/℃。本文設計的遲滯比較器的遲滯門限電壓在-40 ℃~125 ℃范圍內的變化最大為9.16 mV,溫度系數為0.055 5 mV/℃。說明本文對遲滯比較器尾電流的溫度補償有效。

4 結論

本文提出了一款寬輸入范圍的全差分遲滯比較器。通過仿真驗證,電路能夠將-12~12 V 范圍內的差分輸入信號準確地轉化為數字信號。遲滯門限電壓溫度系數為0.055 5 mV/℃,滿足工業級應用。下一步將研究減小器件失配對遲滯門限電壓的影響。