軌道動靜結合快速檢測多源數據采集模塊設計

陳小宇 ,汪 歆 ,武瑞宏 ,任曉春 ,鄧 川

(1.華中師范大學 物理科學與技術學院,湖北 武漢 430079;2.中鐵第一勘察設計院集團有限公司,陜西 西安 710043)

0 引言

多源異構數據的高精度同步采集是軌道動靜結合檢測系統中的關鍵技術之一[1-3]。軌道動靜結合檢測系統是以慣性測量系統為核心測量單元,并輔以全站儀、GPS、軌距、傾角、里程計、軌枕識別等多類高精度傳感器,實現鐵路軌道幾何尺寸的快速檢測。隨著高鐵的迅猛發展,列車的速度不斷提高,在列車提速的同時,會對鐵軌造成更大的傷害,鐵路軌道會發生形變、磨耗等現象,而軌道結構的各個部件產生的形變都會直接或間接影響列車運營的平穩性和安全性[4-9]。由于軌道動靜結合快速檢測系統的動態測量模式,測量速率快,采樣頻率高,大量多源數據需要同步采集、處理與存儲,并實時上傳至控制中心,用于后續綜合解算,因此,對多源數據采集模塊提出了更高的性能需求[10]。針對上述問題,本文設計了一套軌道動靜結合快速檢測多源數據采集模塊,該模塊以FPGA 為主控芯片,利用高穩晶振、結合GPS 輸出的PPS 脈沖建立高精度時間基準,通過控制AD 采樣頻率實現位移傳感器、溫度傳感器、激光位移傳感器等多傳感器數據的高精度實時同步采集[11-12],將采集的數據通過USB 實時傳輸至Jetson TX2[13],進行融合處理后,實現鐵軌幾何尺寸、形變及磨損的快速檢測。

1 總體設計方案

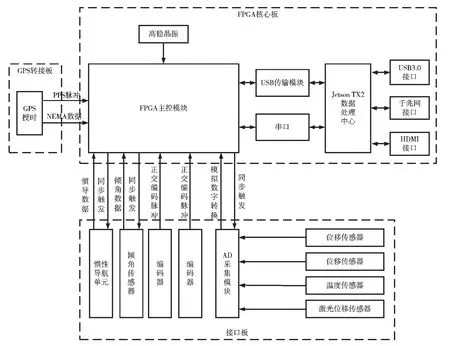

總體設計框圖如圖1 所示。為減小體積、便于安裝和維護,將整個系統分為FPGA 核心板、接口板、GPS 轉接板和電源板四個子模塊。FPGA 核心板采用Xilinx 公司的Artix-7 系列FPGA 為主控制芯片[14-15],通過高穩晶振和GPS 轉接板輸出的PPS 脈沖和NEMA 數據建立高精度時間基準,充分發揮FPGA 高速并行的優勢,實現對接口板上慣導、編碼器、位移傳感器、溫度傳感器、激光位移傳感器等多傳感器數據同步采集控制;并以NVIDIA 公司的Jetson TX2 作為數據處理融合中心,TX2通過千兆網接口可以與上位機通信,接收上位機發送的控制指令,通過串口與FPGA 核心板上的FPGA 芯片通信,FPGA 同步采集的各個傳感器數據通過USB 傳輸模塊上傳至TX2,進行數據的處理、融合和存儲;電源板上集成高效率的DC/DC 轉換模塊和電源轉換芯片,實現高效電源轉換,可以為各個模塊提供供電電源,為整個系統穩定運行提供保障。

圖1 系統總體設計框圖

2 系統硬件核心電路設計

2.1 FPGA 核心板設計

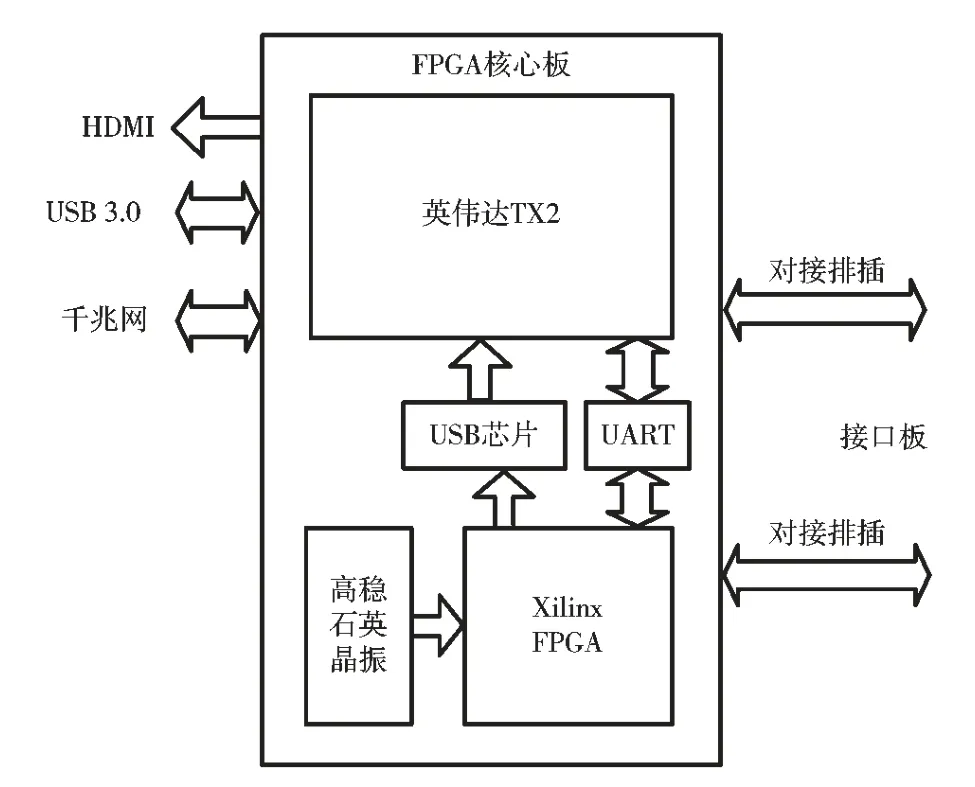

FPGA 核心板框圖如圖2 所示,作為整個軌道動靜結合快速檢測多源數據采集系統的核心部件,該子模塊主要完成千兆網、USB 3.0、HDMI 等高速信號接口的處理、A/D 轉換控制及數據傳輸、高精度時間基準建立、IMU 數據同步采集[16]、編碼器數據同步采集等核心任務,通過接插件與接口板對扣連接。

圖2 FPGA 核心板框圖

2.1.1 主控芯片的選型

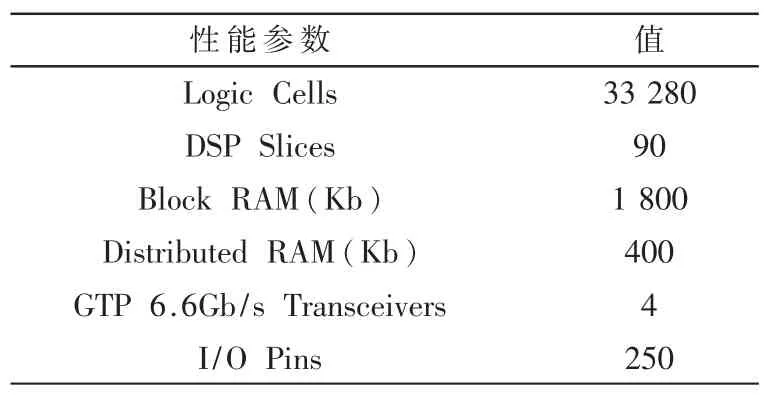

選擇Xilinx 公司的Artix-7 系列FPGA 作為主控芯片,該芯片提供了行業最低的系統成本和功耗,Artix-7 器件在單個成本優化的FPGA 中提供了最高性能功耗比結構、收發器線速、DSP 處理能力以及AMS 集成。綜合考慮邏輯數量、I/O 口數量、RAM 數量、乘法器數量、封裝、功耗要求以及供貨渠道與價格因素,選擇XC7A35T-1CSG324I 型號作為主控芯片,該型號在多種通用邏輯和DSP 應用中優化實現了最低成本和功耗,滿足設計要求。該芯片詳細參數如表1 所示。

表1 FPGA 性能參數信息表

2.1.2 時間基準的建立

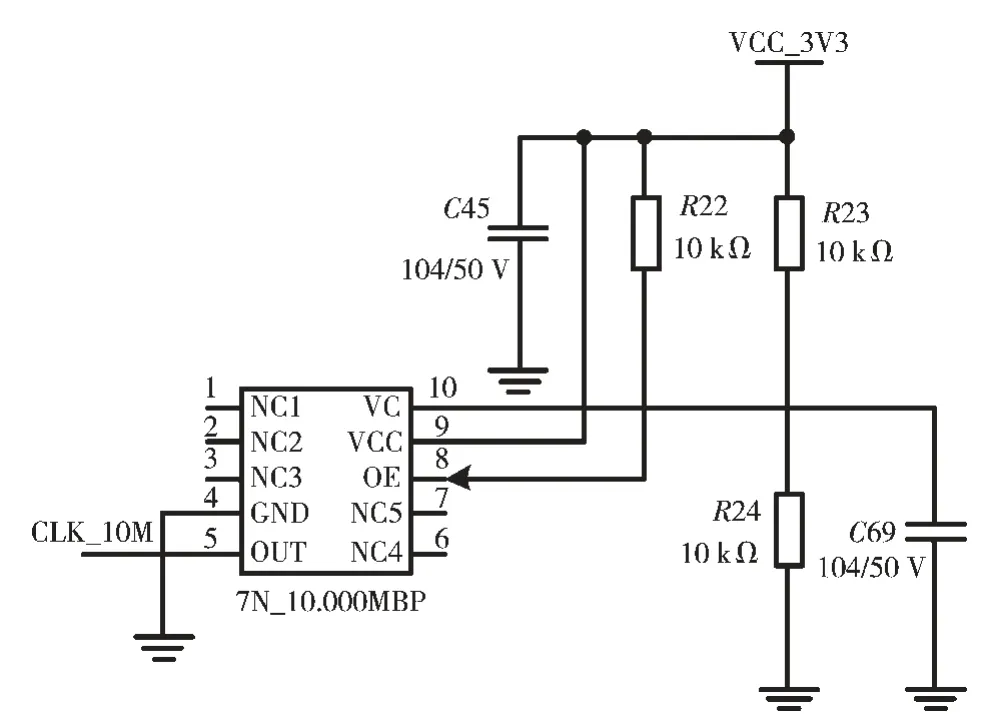

由于高穩晶振短期穩定性好,GPS 輸出的PPS 秒脈沖長期精度高,采用GPS 輸出的PPS 脈沖對高溫晶振進行馴化,建立高精度的時間基準。系統的晶振電路圖如圖3 所示。高穩石英晶振所選型號為7N-10.000MBP,頻率為10 MHz,其頻率穩定誤差20 年內穩定在±4.6 ppm。

圖3 晶振電路圖

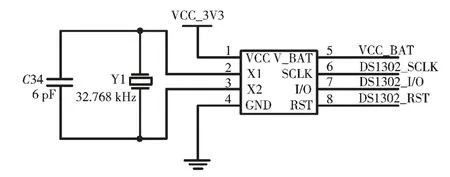

采用DS1302 為模塊提供初始時間,其電路如圖4所示。

圖4 計時芯片電路圖

啟動時,讀取DS1302 的時間作為系統初始時間,外部高穩石英晶振的輸出信號被FPGA 中的鎖相環捕捉,FPGA 將對信號進行累加作為系統的參考時鐘,同時抓取GPS 輸出的PPS 脈沖信號上升沿作為絕對整秒的開始,在連續檢測到兩個PPS 脈沖時,將上一PPS 對應時間加一秒進行授時,同時清零FPGA 內部累加計數器,這樣保證了FPGA 內部脈沖與GPS 的PPS 秒脈沖信號邊沿對齊,實現兩者的時間統一。在GPS 信號穩定時,FPGA 通過串口接收并解析GPS 的GPRMC 格式數據包,每隔半小時將解析出的時間信息寫入DS1302 中,確保下次系統啟動時初始時間的準確性。

2.2 接口板設計

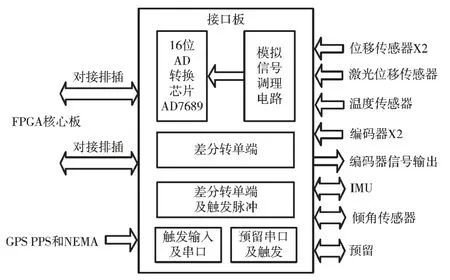

接口板如框圖5 所示,接口板作為FPGA 核心板和傳感器連接的中間部件,主要完成各傳感器數據信號調理、電平轉換、A/D 轉換等功能,并將轉換后的信號通過兩排排插連接至FPGA 核心板的FPGA 芯片,由FPGA 芯片根據設定的時間間隔,完成各傳感器數據的同步采集。

圖5 接口板框圖

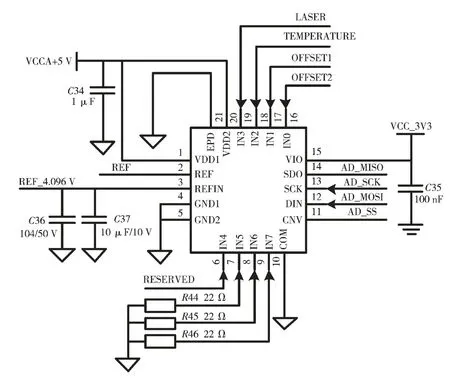

2.2.1 ADC 采集模塊

位移傳感器、激光位移傳感器和溫度傳感器的輸出信號經信號調理電路后送入AD7689,AD7689 是16 位4/8通道的電荷再分配逐次逼近寄存器型(SAR)模數轉換器,采用單電源VDD 供電,吞吐速率為250 kS/s。AD7689 使用SPI 接口實現配置寄存器的寫入和轉換結果的接收,SPI 接口使用單獨的電源VIO,它被設定為主機邏輯電平,其功耗與吞吐速率成正比。FPGA 通過該芯片采集位移傳感器、激光位移傳感器和溫度傳感器的數據。其電路設計如圖6 所示。

圖6 ADC 數據采集轉換電路

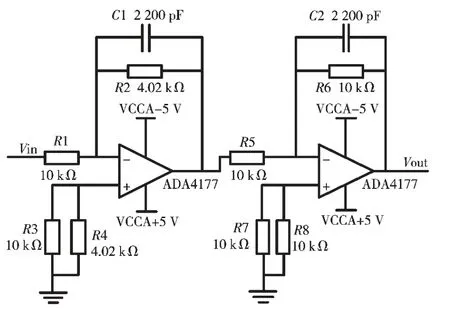

2.2.2 傳感器信號調理電路

由于位移傳感器、激光位移傳感器和溫度傳感器輸出模擬信號的幅值可能各不相同,而AD7689 可接受輸入的電壓范圍為0~4.096 V,因此上述傳感器輸出的模擬信號不能直接輸入至A/D 轉換芯片,需要將這些模擬信號通過信號調理電路調理為A/D 可接受的模擬信號輸入并保證這些模擬信號幅值的統一。圖7 所示為某一路位移傳感器的信號調理電路。

圖7 位移傳感器信號調理電路

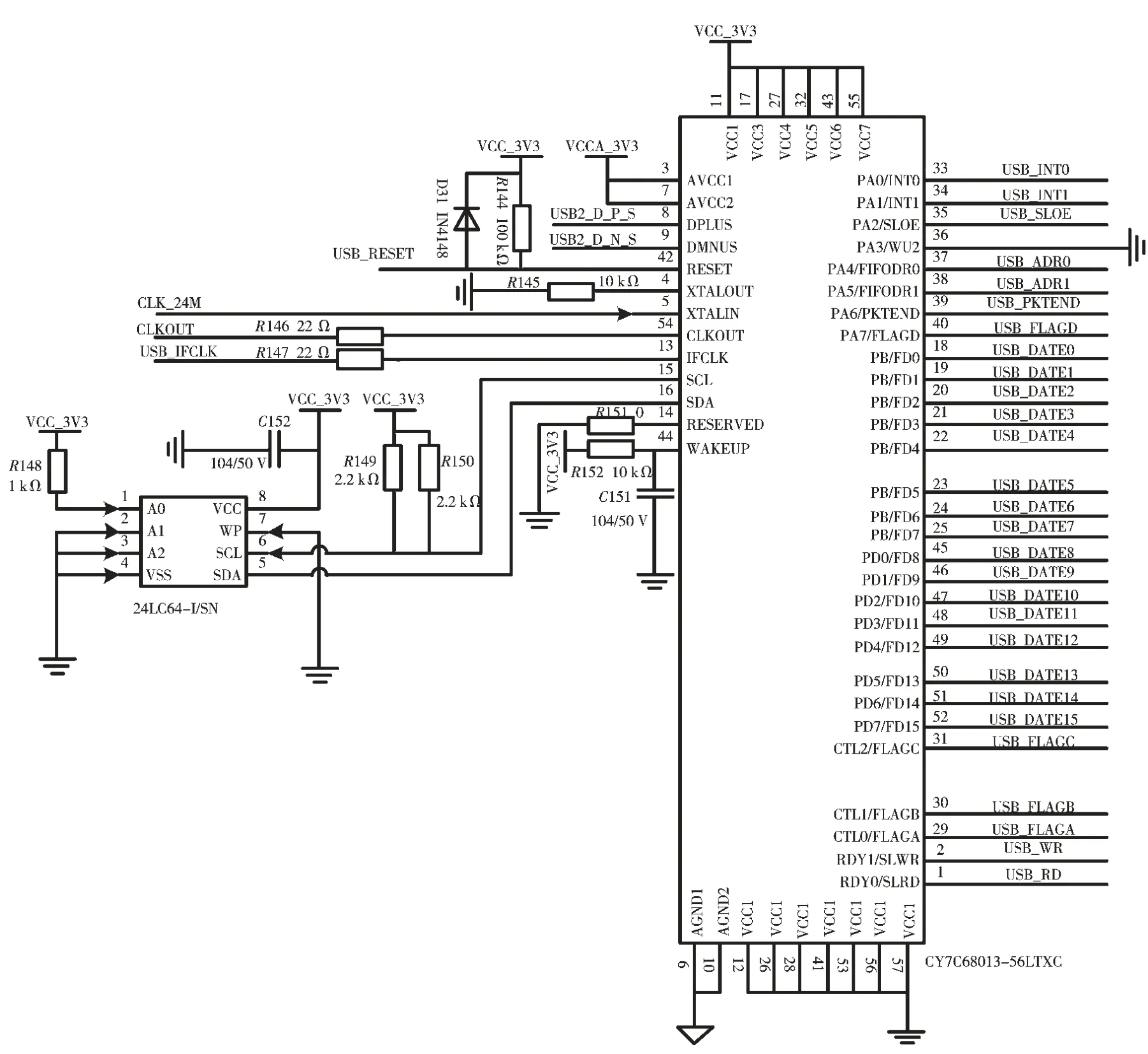

2.2.3 USB 電路設計

采用CY7C68013 芯片作為USB 傳輸控制芯片,FPGA 通過16 位并行接口與該芯片連接,將采集的多傳感器同步數據轉成USB 協議后,傳輸至TX2。電路如圖8 所示。

圖8 USB 電路設計原理圖

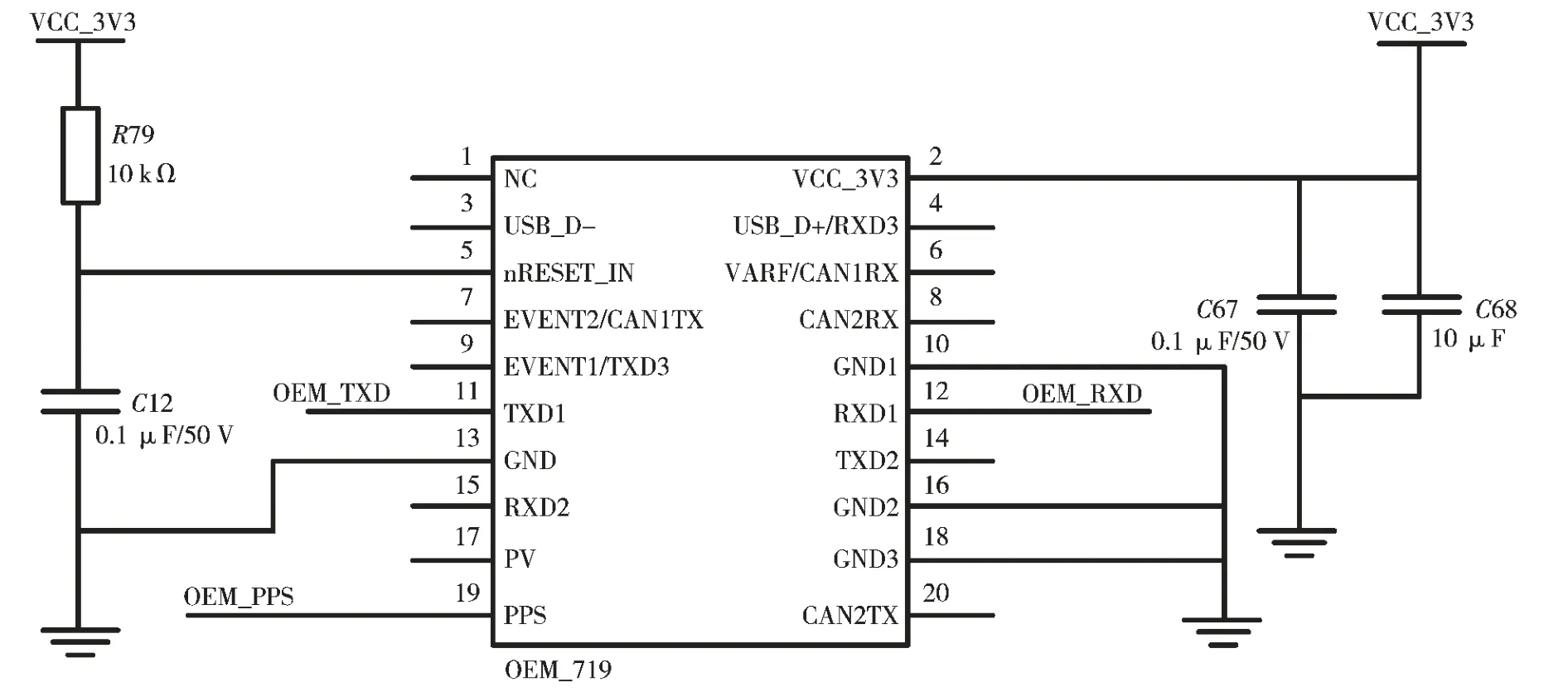

2.3 GPS 轉接板設計

GPS 板卡電路設計如圖9 所示。

圖9 GPS 板卡電路圖

其功能是將GPS模塊安裝在該電路板上,并且完成GPS模塊輸出的PPS 信號和NEMA 信號的電平轉換,FPGA 通過接口板與PPS 和UART 口連接,讀取GPS 的NEMA 數據,結合PPS 信號和高穩石英晶振,在FPGA 內部建立高精度的時間基準。

2.4 電源板設計

電源板框圖如圖10 所示,其功能是接收+12 V電源輸入,通過電源轉換模塊和電源轉換芯片,變換出多路+24 V、+12 V、+5 V 電源,為各子模塊和傳感器提供可靠的供電電源。

圖10 電源板框圖

3 FPGA 軟件設計

3.1 FPGA 主控制模塊程序設計

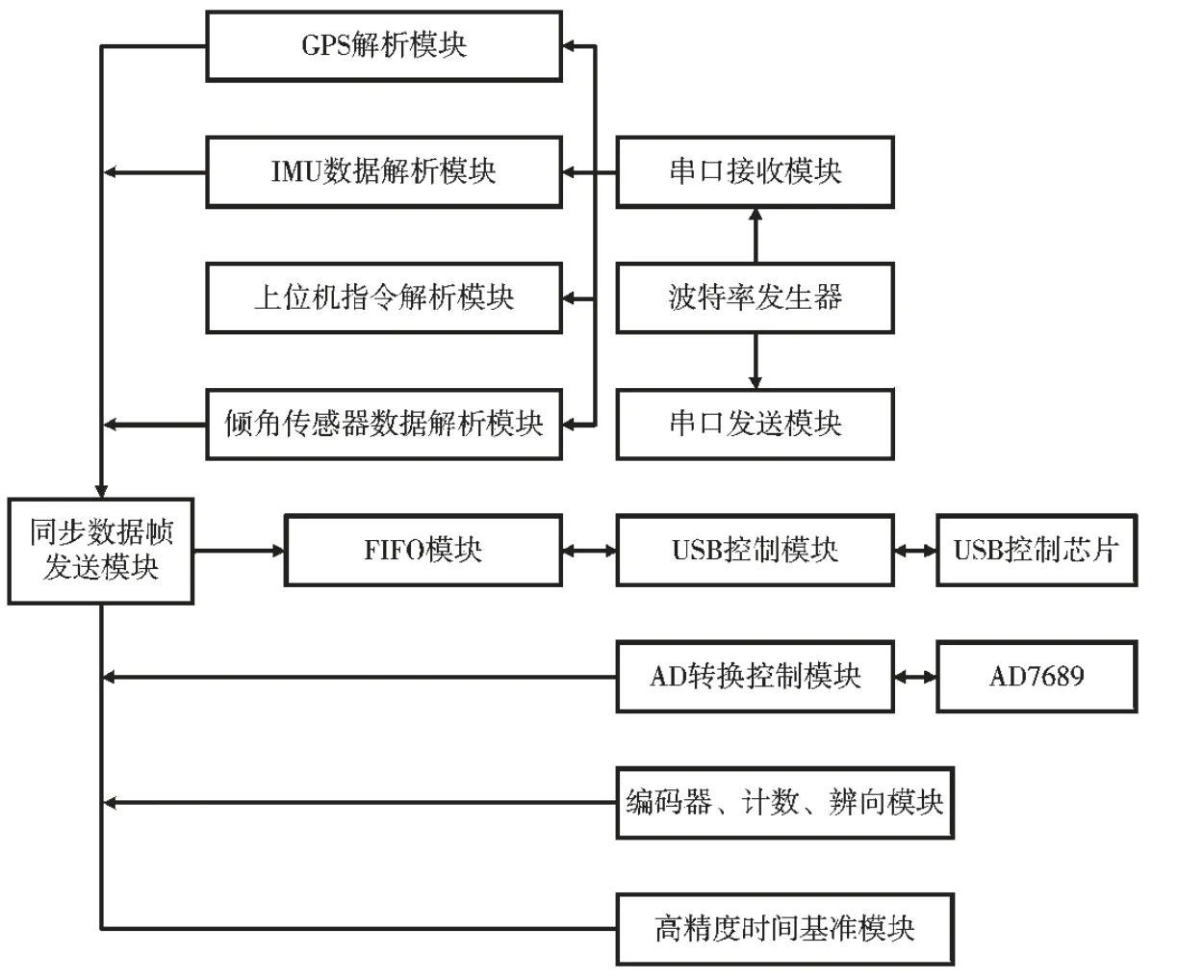

FPGA 采用Xilinx 公司的Artix-7 系列芯片XC7A35T-1CSG324I,開發環境為Xilinx 的Vivado,FPGA 程序框圖如圖11 所示。整個程序采用Verilog HDL 語言開發,采用模塊化設計。

圖11 多傳感器數據采集同步控制流程圖

FPGA 主控制模塊程序設計主要包括高精度時間基準建立模塊、A/D 轉換控制、串口收發模塊、編碼器計數及辨向模塊和FIFO 及USB 控制模塊。FPGA 通過SPI 接口控制16 位AD7689 轉換芯片,啟動A/D 轉換,讀取轉換后的位移傳感器、傾角傳感器和溫度傳感器的數據以及對應的采樣時刻;串口收發模塊實現FPGA 和串口的數據接收和發送。系統使用多個串口,串口1 實現FPGA和TX2 的數據交互,FPGA 通過該串口接收TX2 發送的指令,啟動系統工作或停止,反饋查詢結果;FPGA 通過串口2 接收慣導的數據;串口3 實現FPGA 和GPS 之間的數據接收和發送,接收GPS 發出的NEMA 數據;編碼器計數及辨向模塊對兩路編碼器發出的脈沖進行正反計數,實現兩路編碼器位置的實時計數;FIFO 及USB 控制模塊是對Cypress 公司USB 轉換芯片CY68013 進行控制,將采集到的多傳感器數據打包后,寫入到FIFO 緩存,USB 控制模塊控制FIFO 中的數據,向CY68013 寫入,從而實現多傳感器同步后的數據從FPGA 到TX2 的上傳。

3.2 A/D 采集模塊程序設計

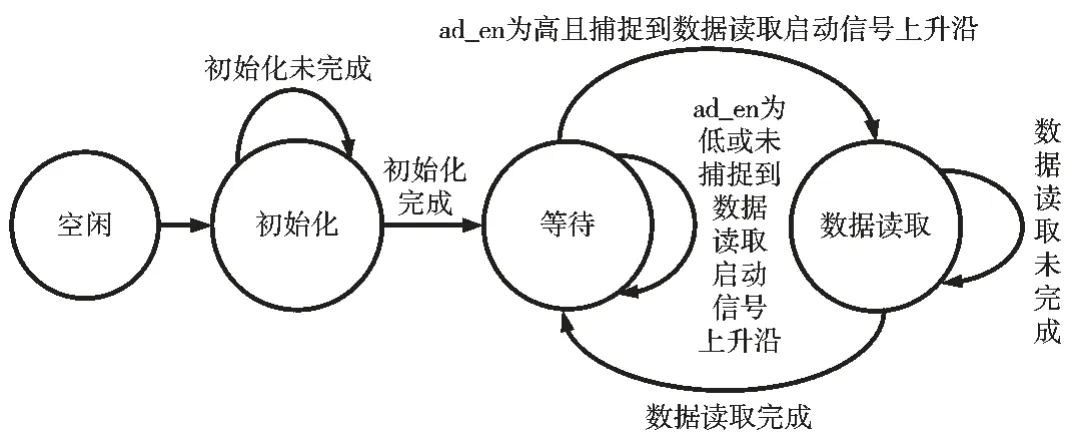

A/D 采集模塊在FPGA 程序設計上,使用三段式狀態機,設置空閑、初始化、等待、數據讀取4 個狀態。ad_en為使能信號,ad_done 為掃描結束的標志位,采集頻率freq 是由一個分頻模塊輸出固定頻率的脈沖實現,將freq 信號延遲2.5 μs 后輸出作為轉換數據讀取的啟動時鐘。當工控機發送系統開始工作指令后,將ad_en 置為高電平,A/D 進行數據采集,直到工控機發送系統停止工作指令后,將ad_en 置為低電平,A/D 停止數據采集;當讀取的通道編號為最后一個通道時,置高ad_done 標志位,啟動一次A/D 同步數據的FIFO 寫入操作,即將年月日、時分秒微秒、5 個通道數據按照協議設計寫入FIFO 緩沖器。AD 狀態轉換圖如圖12 所示,各模塊邏輯接口示意圖如圖13 所示。

圖12 A/D 狀態轉換圖

圖13 A/D 邏輯接口示意圖

4 主要性能測試

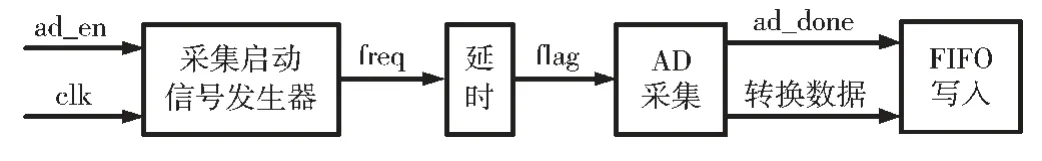

軌道動靜結合快速檢測多源數據采集模塊核心板和接口板如圖14 所示。經反復測試驗證,目前電路板硬件運行良好,FPGA 控制程序穩定,能夠按照設定的時間間隔,完成慣性測量系統、GPS、里程編碼器、位移傳感器、激光位移傳感器、溫度傳感器等多種傳感器的同步控制及數據采集,TX2 上的采集軟件工作正常,上位機能夠通過網絡接口向TX2 下發控制指令,讀取TX2 采集存儲的多傳感器數據,為后續研究工作的開展奠定了堅實的基礎。

圖14 電路板實物圖

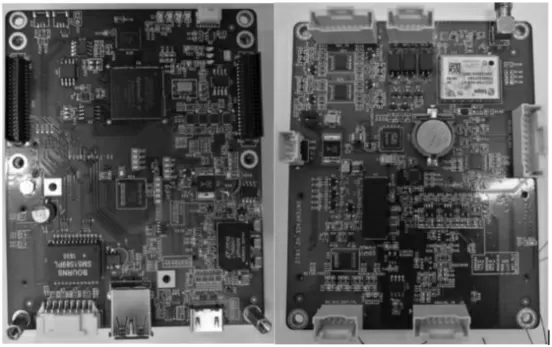

4.1 調理電路仿真分析

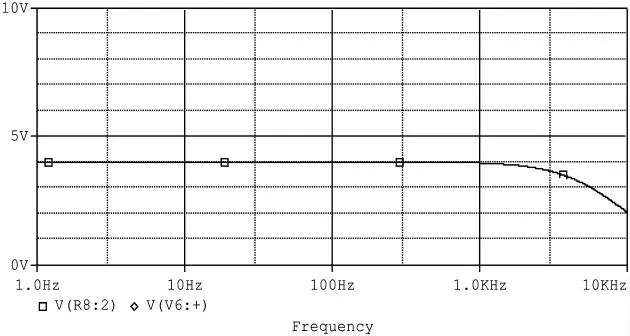

位移傳感器、激光位移傳感器和溫度傳感器輸出的模擬信號經過信號調理放大電路輸入至A/D 可以接受的信號幅值,圖15 為某一路位移傳感器信號調理仿真圖,圖16 為信號帶寬圖。

圖15 某一路位移傳感器信號放大圖

圖16 某一路位移傳感器信號帶寬圖

從仿真結果可以看出,當位移傳感器輸入的模擬信號幅值由0 V 增大到10 V 時,經過信號調理之后輸出的幅值為0 V 到4 V,在A/D 可接受幅值范圍內,其截止帶寬頻率大約為6 kHz,可有效濾除噪聲。

4.2 傳感器數據采集

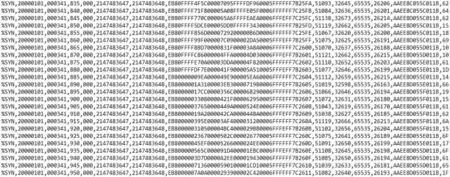

慣導輸出為RS422 接口,在接口板上轉換為3.3 V 電平信號后,輸入至FPGA,由FPGA 讀取慣導的數據。兩路編碼器均輸出為RS422 接口,在接口板上轉換為3.3 V電平信號后,輸入至FPGA,由FPGA 通過計數器記錄編碼器數據。傾角傳感器輸出為RS232 接口,在接口板上轉換為3.3 V 電平信號后,輸入至FPGA,由FPGA 讀取傾角傳感器的數據。FPGA 通過AD7689 采集位移傳感器、激光位移傳感器和溫度傳感器的數據。FPGA 將采集到的IMU、編碼器和傾角傳感器的數據以及FPGA 讀取AD 采集到的數據一起打包后通過USB 傳輸模塊傳輸至TX2 數據處理單元,其中TX2 采集并存儲同步板傳輸過來的原始數據,如圖17 所示。

圖17 TX2 采集并存儲的多傳感器原始數據圖

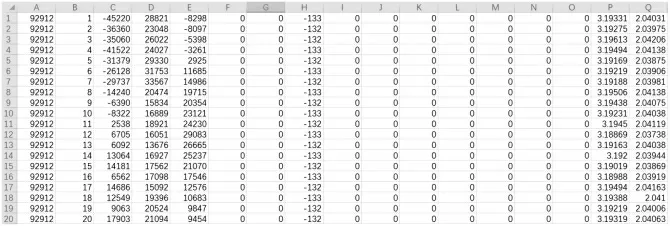

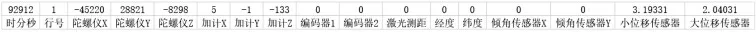

TX2 通過上層軟件把采集到的多傳感器原始數據按照既定的格式解析出來,得到的解析后的數據如圖18所示,其中每一列的數據所代表的含義如圖19 所示。根據陀螺和加速度的零偏、標度因素等參數即可解算出精確的實際數據。

圖18 TX2 解析原始數據后的數據圖

圖19 解析后的數據格式圖

4.3 慣導傳感器數據采集分析

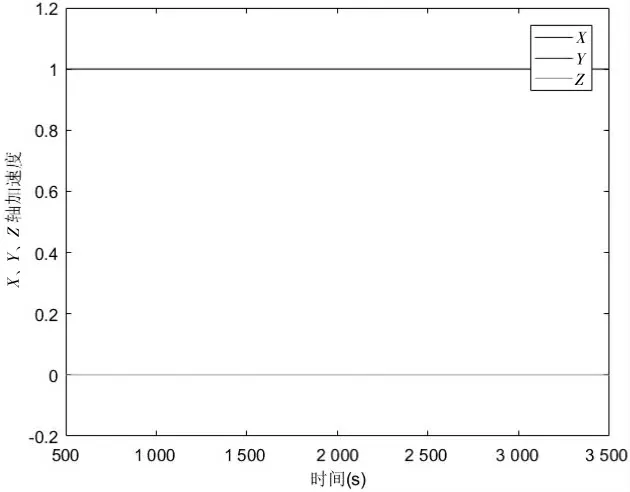

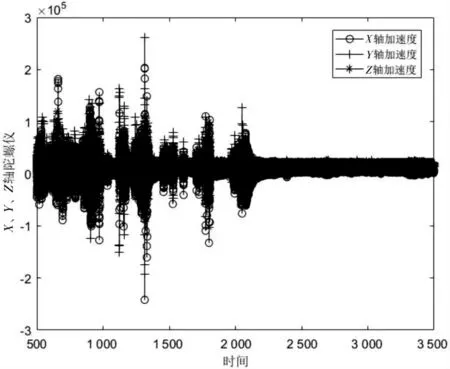

慣性測量單元是根據三個方向的加速度計和陀螺儀組成,通過對加速度及和陀螺儀的測量值進行積分解算來得到當前位置的姿態信息。圖20 為一段時間獲取的加速度計數據圖,圖21 為陀螺儀數據圖。

圖20 慣導加速度計數據圖

圖21 慣導陀螺儀數據圖

從測試結果分析,在系統初始靜止的時候,IMU 的加速度計X、Y 軸的加速度在0 附近,Z 軸的加速度則在重力加速度g 左右。

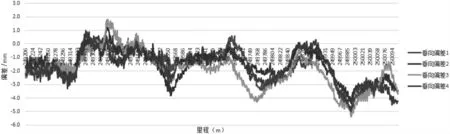

4.4 檢測偏差重復性分析

結合軌道線路的名稱、檢測設備、日期范圍、里程范圍和線路的速度等級,以此來確定檢測偏差的重復次數,如果檢測偏差重復次數較多,可以判定為該區域屬于質量薄弱的路段,需要對該路段及時進行改良。圖22為軌道橫向偏差重復性波形圖,圖23 為軌道垂向偏差重復性波形圖。

圖22 軌道橫向偏差重復性波形圖

通過分析橫向和垂向偏差重復性波形圖可知,橫向偏差范圍在4 mm 以內,垂向偏差范圍在7 mm 以內,由此可知該路段鐵軌質量良好,在其允許誤差范圍內。

5 結論

本文設計了一套軌道動靜結合快速檢測多源數據采集模塊,以FPGA 為主控芯片,以TX2 為處理單元,利用高穩晶振結合GPS 輸出的PPS 脈沖建立高精度的時間基準,通過FPGA 控制AD 轉換芯片的采樣時間,實現位移傳感器、激光位移傳感器、溫度傳感器等傳感器數據的同步采集,并將對應時刻的慣性導航單元、GPS、編碼器、傾角傳感器等傳感器的數據打包,通過USB 傳輸模塊上傳至TX2 進行數據解析、融合處理及存儲。測試結果表明,軌道動靜結合快速檢測多源數據采集模塊的時間同步精度達微秒級,并具有體積小、安裝方便、功耗低等一系列的優點,很好地滿足了軌道動靜結合快速檢測系統的要求。

圖23 軌道垂向偏差重復性波形圖