一種靶網(wǎng)自適應(yīng)的多通道測(cè)速系統(tǒng)設(shè)計(jì)

賈鵬程,王代華,范少波,馬竹新

(1.中北大學(xué)儀器科學(xué)與動(dòng)態(tài)測(cè)試教育部重點(diǎn)實(shí)驗(yàn)室,太原 030051;2.中北大學(xué)電子測(cè)試技術(shù)國(guó)家重點(diǎn)實(shí)驗(yàn)室,太原 030051)

在炮口彈丸初速、破片測(cè)速的測(cè)試手段中,靶網(wǎng)測(cè)速是較為成熟的手段[1]。靶網(wǎng)又根據(jù)原理不同分通靶與斷靶。通常而言,通靶相較斷靶容易制作,但僅可觸發(fā)一次,常用于彈丸測(cè)速項(xiàng)目;斷靶根據(jù)著靶點(diǎn)不同可進(jìn)行多次觸發(fā),更適用于破片測(cè)速場(chǎng)合中。但現(xiàn)有靶網(wǎng)測(cè)試常有以下缺陷:

1)針對(duì)兩種靶網(wǎng)需設(shè)計(jì)不同的測(cè)速儀器,現(xiàn)有破片測(cè)速系統(tǒng)和炮口測(cè)速系統(tǒng)各行其是,且受爆炸產(chǎn)生的電磁干擾影響[2];

2)目前主要采用220 V交流供電,還需配置油機(jī)和掩體,移動(dòng)不便,現(xiàn)場(chǎng)試驗(yàn)工作效率低[3]。

針對(duì)以上靶網(wǎng)測(cè)試法存在的不足,設(shè)計(jì)了一種通/斷靶皆可觸發(fā)的多通道便攜式測(cè)速系統(tǒng)。該系統(tǒng)以FPGA為控制核心,采用單片高速AD轉(zhuǎn)換器,以NAND FLASH作為最終存儲(chǔ)單元,結(jié)構(gòu)小巧,操作簡(jiǎn)單,可提高現(xiàn)場(chǎng)靶場(chǎng)測(cè)試的靈活性以及測(cè)速數(shù)據(jù)的可靠性。

1 系統(tǒng)原理設(shè)計(jì)

該測(cè)速系統(tǒng)在綜合考慮便攜性和系統(tǒng)可靠性的基礎(chǔ)上,采用存儲(chǔ)測(cè)試原理設(shè)計(jì)[4],即系統(tǒng)對(duì)破片或彈丸過(guò)靶產(chǎn)生的信號(hào)進(jìn)行調(diào)理并存儲(chǔ),在實(shí)驗(yàn)結(jié)束后進(jìn)行回讀分析的測(cè)試方法。系統(tǒng)設(shè)計(jì)原理如圖1所示,其設(shè)計(jì)思路如下:

1)測(cè)速系統(tǒng)共分8通道,每通道通過(guò)引線接靶,系統(tǒng)上電后,信號(hào)自適應(yīng)調(diào)理電路可迅速識(shí)別靶類別并調(diào)整觸發(fā)模式。系統(tǒng)觸發(fā)后,信號(hào)自適應(yīng)電路僅輸出對(duì)應(yīng)調(diào)理后的靶線通或靶線斷信號(hào)。

2)該系統(tǒng)脫離現(xiàn)有多通道存儲(chǔ)式測(cè)速系統(tǒng)的多控制器+多AD轉(zhuǎn)換器+多片存儲(chǔ)器的架構(gòu),以高速AD轉(zhuǎn)換器+多路復(fù)用器架構(gòu)實(shí)現(xiàn)信號(hào)采集[5-6],采用FPGA為控制核心。此架構(gòu)可在信號(hào)完整度以及采樣精度得以保證的前提下較大程度地減小系統(tǒng)體積,降低功耗。

圖1 系統(tǒng)設(shè)計(jì)原理框圖

系統(tǒng)工作過(guò)程:試驗(yàn)前,根據(jù)爆炸當(dāng)量和各測(cè)點(diǎn)相對(duì)于爆心的距離對(duì)測(cè)試系統(tǒng)進(jìn)行相關(guān)工作參數(shù)的設(shè)定,包括存儲(chǔ)長(zhǎng)度、負(fù)延時(shí)長(zhǎng)度等,系統(tǒng)對(duì)設(shè)定好的工作參數(shù)具有記憶功能。系統(tǒng)上電后進(jìn)入循環(huán)采樣階段,戰(zhàn)斗部起爆后,觸靶信號(hào)使系統(tǒng)觸發(fā),各通道信號(hào)在同一時(shí)基下開(kāi)始記錄,將有效數(shù)據(jù)保存到存儲(chǔ)器中;存儲(chǔ)完成后通過(guò)USB接口進(jìn)行數(shù)據(jù)讀取,利用上位機(jī)對(duì)測(cè)試數(shù)據(jù)進(jìn)行顯示處理。

2 關(guān)鍵技術(shù)研究

2.1 通/斷靶自適應(yīng)調(diào)理電路設(shè)計(jì)

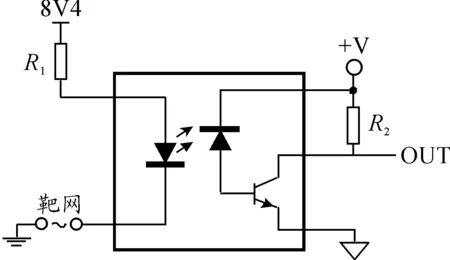

2.1.1基于高速邏輯光耦的信號(hào)轉(zhuǎn)換電路

在爆炸威力實(shí)驗(yàn)中,爆炸產(chǎn)物高速飛散并與周圍空氣介質(zhì)發(fā)生劇烈摩擦和碰撞,最終會(huì)在周圍空氣中形成等離子體。這些帶電離子會(huì)通過(guò)觸發(fā)線以及梳狀靶耦合進(jìn)測(cè)速儀,引起強(qiáng)烈的電磁干擾。在以往的測(cè)試實(shí)踐中,采集的數(shù)據(jù)可以反映出這一現(xiàn)象的存在。如果不采取信號(hào)隔離和抗干擾措施,雜亂的干擾信號(hào)輕則影響有效信號(hào)的分析,強(qiáng)電磁干擾甚至?xí)?dǎo)致系統(tǒng)瞬間崩潰。針對(duì)以上問(wèn)題,本系統(tǒng)采用高速邏輯光耦實(shí)現(xiàn)對(duì)過(guò)靶信號(hào)的隔離,使信號(hào)的輸入端和采集端沒(méi)有電氣連接[7],且在隔離兩端采用不同的接地點(diǎn),切斷“地”干擾的傳播途徑,徹底實(shí)現(xiàn)了兩端信號(hào)的電氣隔離。高速邏輯光耦抑制干擾信號(hào)的同時(shí)還可將靶網(wǎng)的通斷信號(hào)轉(zhuǎn)換成對(duì)應(yīng)的極性信號(hào)。其轉(zhuǎn)換電路圖如圖2。

圖2 靶網(wǎng)信號(hào)轉(zhuǎn)換電路圖

當(dāng)靶網(wǎng)的靶線導(dǎo)通時(shí),光耦內(nèi)部發(fā)光二極管發(fā)光,反向偏置的光敏二極管受光照后導(dǎo)通,經(jīng)輸出三極管反向后光耦輸出低電平;當(dāng)靶線斷開(kāi)時(shí),三極管輸入電流小于觸發(fā)閾值,光耦輸出高電平。即光耦輸出可實(shí)時(shí)反映出當(dāng)前靶線狀態(tài),在對(duì)于給定的某類型靶(通靶或者斷靶),彈丸或者破片過(guò)靶前后產(chǎn)生的信號(hào)極性是不同的。這個(gè)信號(hào)本身是需要記錄的對(duì)象,同時(shí)也可以作為靶類型識(shí)別的依據(jù)。

2.1.2自適應(yīng)信號(hào)發(fā)生調(diào)理電路

為準(zhǔn)確識(shí)別當(dāng)前靶類別、屏蔽非當(dāng)前靶的信號(hào)且將有效信號(hào)調(diào)理至合適的范圍以便后續(xù)電路處理,系統(tǒng)采用簡(jiǎn)單邏輯器件如D觸發(fā)器、單穩(wěn)態(tài)觸發(fā)器等完成對(duì)光耦輸出信號(hào)的硬件識(shí)別、屏蔽、調(diào)幅,并將彈丸/破片過(guò)靶的邊沿信號(hào)轉(zhuǎn)換成脈寬較小的脈沖信號(hào)。自適應(yīng)信號(hào)發(fā)生調(diào)理電路如圖3所示。

圖3 自適應(yīng)信號(hào)發(fā)生調(diào)理電路圖

當(dāng)外部引線接好靶網(wǎng)后,系統(tǒng)上電,D觸發(fā)器經(jīng)RC電路高復(fù)位識(shí)別未觸發(fā)的靶信號(hào)。若當(dāng)前靶網(wǎng)為通靶,調(diào)理電路僅輸出靶線被打斷的對(duì)應(yīng)脈沖;同理,若當(dāng)前靶為斷靶,調(diào)理電路僅輸出靶線導(dǎo)通的對(duì)應(yīng)脈沖。在該電路中,單穩(wěn)態(tài)觸發(fā)器在輸入信號(hào)極性發(fā)生變化時(shí)產(chǎn)生并輸出脈沖,D觸發(fā)器、邏輯與門和或門則根據(jù)靶網(wǎng)初始狀態(tài)對(duì)該脈沖選通輸出。

另一方面或門輸出的脈沖信號(hào)需要經(jīng)過(guò)基線調(diào)整和信號(hào)縮比電路才可以由ADC采樣,同時(shí)該脈沖信號(hào)經(jīng)觸發(fā)器輸出系統(tǒng)內(nèi)觸發(fā)信號(hào),使測(cè)速系統(tǒng)各通道的數(shù)據(jù)開(kāi)始記錄。

2.2 基于FPGA的采集存儲(chǔ)邏輯設(shè)計(jì)

FPGA是現(xiàn)場(chǎng)可編輯門陣列,相較其他處理器,F(xiàn)PGA具有并行處理數(shù)據(jù)的優(yōu)勢(shì),更適用于多通道、數(shù)據(jù)吞吐量高的場(chǎng)合中[8]。本系統(tǒng)采用FPGA作為主控單元,主要實(shí)現(xiàn)各通道數(shù)據(jù)的采集、編幀打包、緩沖、存儲(chǔ)等功能。基于FPGA的采集存儲(chǔ)邏輯框圖如圖4。

圖4 FPGA控制邏輯框圖

2.2.1多路模擬開(kāi)關(guān)+單片AD架構(gòu)邏輯設(shè)計(jì)

多路模擬開(kāi)關(guān)的選取主要考慮以下指標(biāo):通道數(shù)量、導(dǎo)通電阻、切換速度和芯片電源電壓范圍等[9]。系統(tǒng)選用ADI公司的8選1高速模擬開(kāi)關(guān)ADG708,其導(dǎo)通電阻為3,電阻平坦度為0.5,切換速度達(dá)14 ns,電源電壓范圍為1.8~5.5 V,滿足設(shè)計(jì)要求。FPGA邏輯電平的上升和下降時(shí)間都很短,可實(shí)現(xiàn)時(shí)序邏輯的精準(zhǔn)控制[10],ADG708可在FPGA控制下實(shí)現(xiàn)8路通道的快速切換。其中每一路都唯一對(duì)應(yīng)模擬開(kāi)關(guān)的一個(gè)通道,通過(guò)控制ADG708的通道地址“A0-A3”即可選通8路模擬通道的某一個(gè)。

根據(jù)靶網(wǎng)產(chǎn)生的脈沖信號(hào)的采樣需求,各通道采樣率需達(dá)到1 MHz,所以8路總采樣率為8 MHz,本系統(tǒng)選用ADI公司的高性能12位模數(shù)轉(zhuǎn)換器AD9220,其最高采樣率達(dá)10 Msps。它采用特有的四級(jí)流水結(jié)構(gòu)和錯(cuò)誤修正,可保證在整個(gè)工作溫度內(nèi)沒(méi)有誤碼,適合常規(guī)靶場(chǎng)爆炸包括炮口測(cè)速的高溫惡劣環(huán)境。

為方便時(shí)序邏輯的設(shè)計(jì)和對(duì)信號(hào)采樣率的控制,將采樣的數(shù)據(jù)幀設(shè)置為固定格式,數(shù)據(jù)幀結(jié)構(gòu)如表1所示。因各通道采樣率均需滿足1MHz,故每個(gè)采樣點(diǎn)采樣頻率取1 MHz。在幀尾增加幀結(jié)束標(biāo)志55、AA,便于上位機(jī)回讀數(shù)據(jù)時(shí)對(duì)數(shù)據(jù)是否發(fā)生丟幀和誤幀進(jìn)行檢測(cè)。該幀結(jié)構(gòu)保證各采樣點(diǎn)均勻采樣,使多路數(shù)據(jù)有序?qū)懭氪鎯?chǔ)器,且在上位機(jī)讀取數(shù)據(jù)后便于區(qū)分各路模擬信號(hào)的量化數(shù)據(jù)。

表1 數(shù)據(jù)幀結(jié)構(gòu)

2.2.2存儲(chǔ)邏輯設(shè)計(jì)

與其他存儲(chǔ)介質(zhì)相比,NAND FLASH以其容量大、體積小、掉電數(shù)據(jù)不丟失且功耗低的特點(diǎn),成為當(dāng)今存儲(chǔ)元件的首選。存儲(chǔ)式記錄儀不可避免會(huì)需要有效記錄波前信號(hào),即負(fù)延時(shí)功能。但是NAND FLASH自身的存儲(chǔ)結(jié)構(gòu)決定了存儲(chǔ)數(shù)據(jù)之前需要花費(fèi)ms級(jí)的擦除時(shí)間,且測(cè)試數(shù)據(jù)也不能連續(xù)寫入,降低了FLASH總體寫入速度,并不適用于瞬態(tài)信號(hào)的快速存儲(chǔ)。若采用多片F(xiàn)LASH進(jìn)行流水操作來(lái)填補(bǔ)擦除時(shí)間的數(shù)據(jù),則造成FLASH資源浪費(fèi)和增加編程難度,因此選用SRAM+FLASH陣列來(lái)實(shí)現(xiàn)系統(tǒng)存儲(chǔ)邏輯[11]。整個(gè)數(shù)據(jù)處理和存儲(chǔ)流程如圖5所示,其中采用SRAM作為負(fù)延時(shí)緩存單元;采用FPGA內(nèi)部IP核例化FIFO作為觸發(fā)后數(shù)據(jù)的緩存單元;采用了兩片F(xiàn)LASH作為最終存儲(chǔ)單元。

圖5 存儲(chǔ)邏輯設(shè)計(jì)流程框圖

存儲(chǔ)流程共分四步:第一步,未觸發(fā)時(shí),F(xiàn)PGA根據(jù)需要設(shè)定負(fù)延時(shí)長(zhǎng)度并在FLASH內(nèi)部留出同等的地址空間。此時(shí)FPGA可快速的將數(shù)據(jù)寫入SRAM,進(jìn)行負(fù)延時(shí)操作;第二步,觸發(fā)信號(hào)到來(lái)后,在SRAM寫入16 Byte負(fù)延時(shí)標(biāo)識(shí)信號(hào),并將接下來(lái)AD采集的數(shù)據(jù)通過(guò)FPGA內(nèi)部FIFO緩存;第三步將FIFO數(shù)據(jù)取出,寫入FLASH單元;第四步采集完成后,將SRAM中數(shù)據(jù)取出,寫進(jìn)預(yù)留的FLASH空間。如此操作,就可將全部的數(shù)據(jù)寫入最終存儲(chǔ)單元FLASH中。其中SRAM僅作為負(fù)延時(shí)緩存單元,觸發(fā)后的數(shù)據(jù)則由FIFO緩存,避免采集期間同時(shí)對(duì)SRAM和FLASH進(jìn)行控制,操作較為簡(jiǎn)潔,且利用FIFO有助于提高代碼穩(wěn)定性和效率。

本系統(tǒng)總采樣率8 MHz,分辨率為12位,理論數(shù)據(jù)寫入速率為14 MB/s。存儲(chǔ)介質(zhì)選取鎂光公司的MT29F8G08ABA,其頁(yè)編程時(shí)間tPROG為200~600 μs,頁(yè)容量4 096 Byte。按照?qǐng)D5邏輯,若用單片F(xiàn)LASH的交替雙平面操作模式,數(shù)據(jù)寫入速率在9.9~19.8 MB/s之間。為保證數(shù)據(jù)可靠性,最終采用雙片F(xiàn)LASH片內(nèi)交叉片外流水操作[12]。雙片F(xiàn)LASH流水線操作如圖6所示。

圖6 雙片F(xiàn)LASH流水操作示意圖

雙片F(xiàn)LASH流水存儲(chǔ)本質(zhì)為循環(huán)利用第二片F(xiàn)LASH的加載時(shí)間填補(bǔ)當(dāng)前FLASH的頁(yè)編程繁忙時(shí)間,其理論寫入速率為15.84~26.2 MB/s,滿足設(shè)計(jì)需要。

3 同步性測(cè)試和實(shí)驗(yàn)驗(yàn)證

3.1 多通道同步性測(cè)試

多通道同步性測(cè)試是為了測(cè)試在同一時(shí)基下各通道的同步性誤差,同時(shí)也是對(duì)系統(tǒng)原理以及PCB等設(shè)計(jì)的綜合考量。在同步性測(cè)試中,用系統(tǒng)8通道同時(shí)采集同一斷靶信號(hào),圖7為8通道過(guò)靶波形,圖8為波形放大之后的起始時(shí)刻,可知:多通道同步性誤差僅為1 μs,這在使用靶網(wǎng)的實(shí)驗(yàn)場(chǎng)合中對(duì)數(shù)據(jù)的影響可忽略不計(jì)。

圖7 多通道過(guò)靶波形

圖8 多通道同步性波形(放大)

3.2 系統(tǒng)性能試驗(yàn)驗(yàn)證

本系統(tǒng)已在多次靶場(chǎng)彈丸破片測(cè)速現(xiàn)場(chǎng)試驗(yàn)中得到成功應(yīng)用,驗(yàn)證了其可靠性和便捷性。在某次炮口初速測(cè)試試驗(yàn)中,通靶安裝在離炮口50 m的彈道支架上,靶距4 m,測(cè)速系統(tǒng)通過(guò)長(zhǎng)引線接靶,并有高精度光幕測(cè)速儀記錄彈丸瞬態(tài)速度。圖9為彈丸過(guò)靶后的測(cè)速現(xiàn)場(chǎng)。

圖9 某型炮彈丸初速測(cè)試現(xiàn)場(chǎng)

多次試驗(yàn)測(cè)量數(shù)據(jù)如表2所示,從表中可以看出本系統(tǒng)與高精度光幕測(cè)速儀測(cè)速的結(jié)果基本一致。

實(shí)驗(yàn)證明,按上述原理設(shè)計(jì)的測(cè)速裝置和測(cè)試方法行之有效,多通道測(cè)速系統(tǒng)在野外環(huán)境下操作簡(jiǎn)單靈活、數(shù)據(jù)穩(wěn)定可靠,可滿足常規(guī)靶場(chǎng)的測(cè)速需求。

表2 某型炮多發(fā)試驗(yàn)測(cè)量數(shù)據(jù)

4 結(jié)論

本系統(tǒng)采用記錄破片過(guò)靶波形的方法,能夠清晰再現(xiàn)破片穿靶過(guò)程,極大地提高了破片識(shí)別的正確率;信號(hào)極性可自動(dòng)識(shí)別,不需人員干預(yù),實(shí)現(xiàn)了一機(jī)兩用,使用方式靈活便攜;測(cè)試人員可根據(jù)具體測(cè)試任務(wù)進(jìn)行通道數(shù)的靈活選擇和系統(tǒng)工作參數(shù)的可編程設(shè)置,上位機(jī)選取特征點(diǎn)簡(jiǎn)單,數(shù)據(jù)處理準(zhǔn)確高效,滿足對(duì)不同彈丸破片的測(cè)試需求,為各類彈丸破片及破片速度評(píng)估提供了一種有效可靠的測(cè)試手段。