基于W5300的高速數據傳輸系統設計與實現

杜志美,文 豐,張凱華

(中北大學 儀器與電子學院電子測試技術國家重點實驗室,太原 030051)

如今信息技術發展突飛猛進,通信方式向著數據需求量大、實時性高、易于組網等方向發展[1]。集成有TCP/IP協議的以太網芯片W5300以其成本低、數據傳輸距離遠、易于移植且簡單快捷的實現高性能數據通信等優勢得到了廣泛應用[2]。開發者只需要對W5300應用層進行操作,就可以實現不同網絡平臺間的數據交互。傳統的以太網系統存在數據傳輸不穩定,成本較高等缺點,且在實際應用中,其傳輸速率很難突破50Mbps[3-4]。

本研究所提出的系統設計采用“FPGA+W5300”組合模式,不僅實現了數據快速、穩定傳輸,而且極大地降低了開發難度、提高了數據傳輸的實時性。

1 系統硬件結構與設計

本系統需要設計一個客戶端和一個服務器,并在兩個相對獨立的系統之間建立連接完成數據傳輸,傳輸速度要求達到80 Mbps,并且數據穩定可靠。

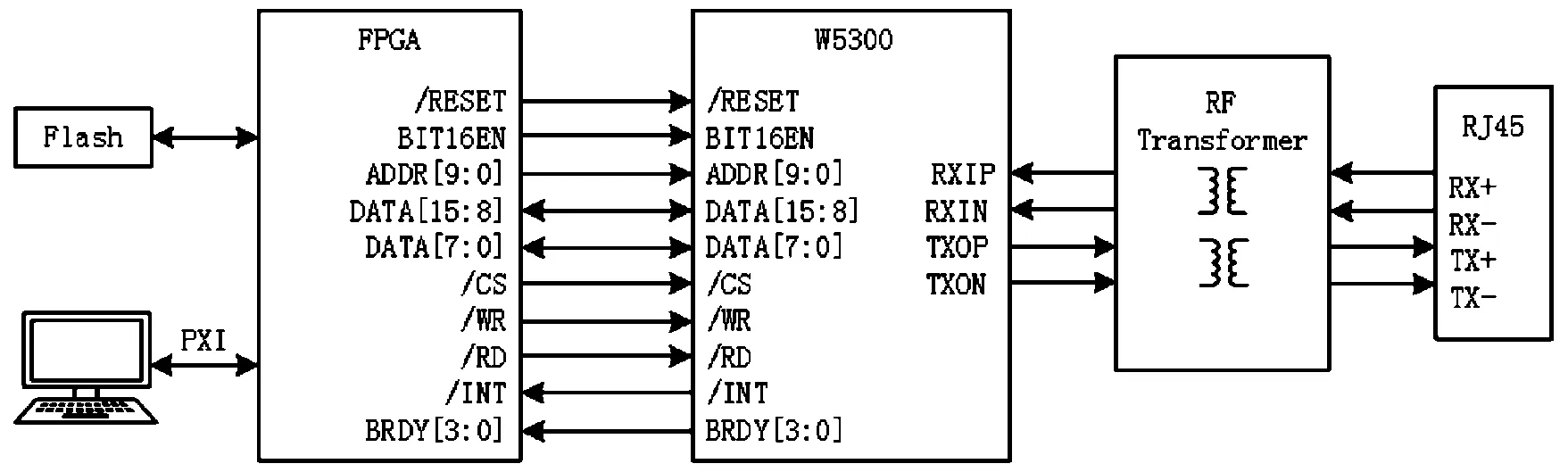

相比于DSP等控制類芯片,FPGA特有的并行處理能力、高速接口設計、豐富的I/O接口資源等優勢,使其在高速數據處理和邏輯控制等方面具有很高的實時性,采用FPGA作為主控芯片,可以使不同網絡系統中數據更高速傳輸。為滿足數據傳輸速度要求,系統采用“FPGA+W5300”組合模式。系統硬件結構如圖1所示。

圖1 以太網系統硬件結構框圖

FPGA可以根據W5300地址總線對寄存器尋址,按照W5300寄存器讀寫時序,通過數據總線配置和讀取相應寄存器的值。本系統采用16位數據總線模式,所以BIT16EN接高電平,數據總線低8位和高8位都需要與FPGA I/O口連接,接收的數據通過FPGA存入Flash。W5300差分輸入和輸出信號對與外部接口之間增加對稱變壓器,保證芯片與外界的隔離與數據傳輸過程中系統的可靠性。

W5300硬件接口類型與功能描述如表1所示。W5300擁有8個獨立并行端口,內部集成10BasseT/100BasseT以太網物理層[5],支持直接和間接地址模式。FPGA通過直接訪問每個端口的FIFO寄存器,控制端口TX/RX存儲器數據讀取和寫入,從而避免了以往采用FPGA直接處理TCP/IP協議時的負荷,極大簡化了程序的編寫,使系統對數據的傳輸和處理能力得到極大改善。

表1 W5300接口類型和功能表

2 W5300軟件設計

本系統通過FPGA直接操作W5300內部寄存器。FPGA代碼在ISE14.7編譯環境下采用硬件描述語言VHDL編寫。并根據W5300復位時序、寄存器讀和寫時序完成FPGA對W5300的控制。軟件設計流程分為W5300初始化、端口連接、數據發送和接收3個模塊。

2.1 W5300初始化

W5300初始化包括外部接口配置、網絡參數和超時設置和端口TX/RX存儲器分配[6]。

W5300采用/RESET硬件復位,復位信號在保持低電平大于2 μs后保持高電平時間大于10 ms,執行復位。其內部鎖相環將外部25 MHz時鐘源倍頻后產生150 MHz工作時鐘,在復位有效后鎖相環鎖定時鐘頻率[7]。

2.1.1外部接口設置

W5300接口設置包括模式寄存器配置和中斷配置。

采用直接地址模式(IND=0),可將模式寄存器、通用寄存器和端口寄存器映射到內部存儲空間,控制器通過訪問對應映射地址來直接訪問相關寄存器[8],間接地址模式則相反。FPGA在訪問W5300內部寄存器時,寄存器地址從系統基地址開始以2字節遞增方式連續映射在內部存儲器空間。寄存器地址采用大端模式,即寄存器地址的低字節存儲在實際物理地址的高字節。W5300寄存器實際物理地址為“存儲器空間基地址+寄存器偏移量”,其中W5300寄存器的物理基地址為0x08000。

與W5300中斷相關的寄存器包括中斷寄存器(IR)和中斷屏蔽寄存器。中斷寄存器數據位表示當前中斷類型,產生中斷時相應數據位置1,如果中斷屏蔽寄存器(IMR)相應位也為1,則中斷請求輸出引腳/INT置0,向FPGA發出中斷請求,控制器通過查詢中斷寄存器數據位判斷中斷類型并處理中斷。

2.1.2網絡參數和超時設置

為實現數據在多個網絡系統之間傳輸而不會造成數據傳輸混亂,需要對W5300進行網絡參數配置,包括硬件地址寄存器、網關IP 地址寄存器、子網掩碼寄存器和本機IP 地址寄存器。本系統各參數如表2所示。

表2 網絡系統參數配置

TCP是一種可靠數據傳輸控制協議。TCP協議在數據通信中經過三次握手驗證,保證數據傳輸的準確性。為避免驗證過程中長時間等待,需要進行超時設置,超時設置相關寄存器包括重復發送超時寄存器(RTR)和重復發送計數寄存器(RCR)。W5300超時分為ARP發送超時和TCP發送超時兩種。以客戶端向服務器發送ARP請求為例,流程如圖2所示。

圖2 ARP請求流程圖

同樣客戶端向服務器發送TCP數據包后,等待服務器回應ACK響應,若客戶端在RTR設置的時間后連續發送RCR+1次還未收到ACK響應,W5300端口狀態寄存器(Sn_SSR)將變為SOCKET_CLOSED,并且數據發送端口中斷寄存器(Sn_IR)相應位置1,發出中斷請求。

2.1.3端口TX/RX存儲器分配

W5300擴展了128K通信數據存儲器,由16個8K字節存儲單元組成[9-10]。這些存儲單元可以由存儲器單元類型配置寄存器以8K的倍數配置為發送和接收單元,再由存儲器大小配置寄存器分配給每個端口TX存儲器和RX存儲器。

2.2 W5300端口連接

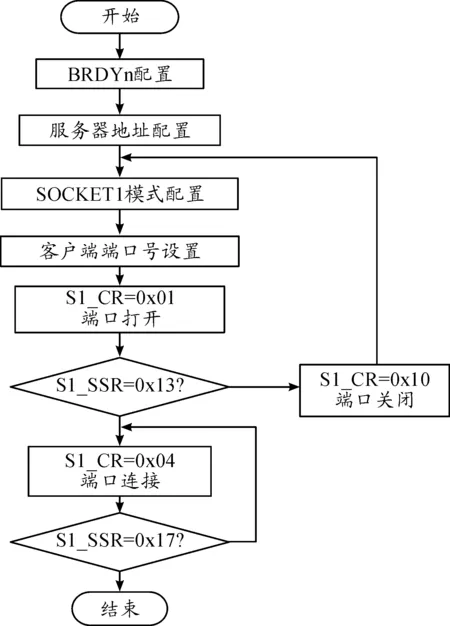

W5300初始化完成后,需要依據設計要求對端口進行配置并連接。W5300具有8個獨立端口,可同時進行數據通信。以客戶端SOCKET1為例,端口配置和連接流程如圖3所示。

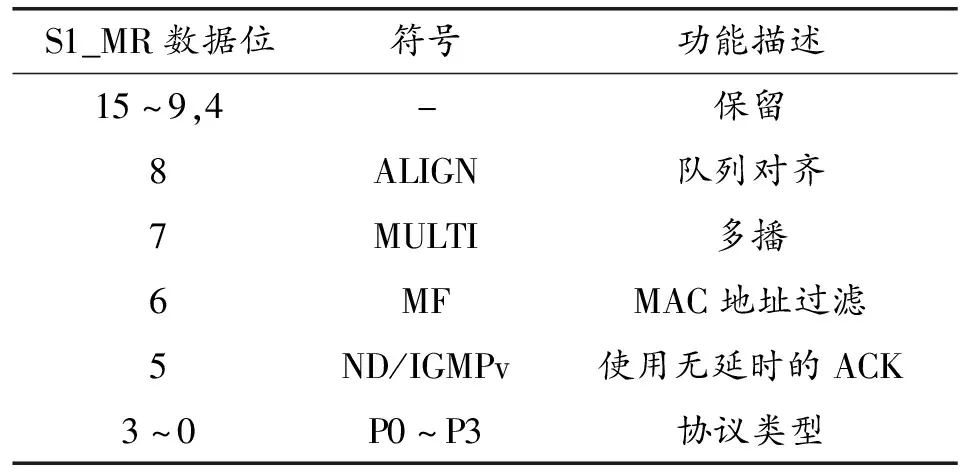

W5300有4個緩沖區監視外接引腳BRDY[3:0],用于實時監測SOCKETn數據收發狀態。本系統配置了BRDY0和BRDY1分別對SOCKET1 TX/RX存儲器監測。在TCP客戶端模式下,客戶端必須在執行連接命令之前配置目標地址。而服務器則在端口建立連接后,S1_DIPR和S1_PORTR自動設置為TCP客戶端IP地址和端口號。端口模式寄存器S1_MR決定了端口通信方式,S1_MR功能描述如表3所示。

在TCP模式下,收到的數據包字節數為偶數時隊列對齊數據位“ALIGN=1”,此時刪除數據包中的PACKET-INFO,可以極大提高數據讀取速度。為了使W5300只接收指定網絡數據包,需要將MF位置1。而ND/IGMPv置1時,端口在收到對端發送的數據包后立刻發送ACK數據包響應,可以提高TCP通信性能。P0~P3即配置端口通信協議(TCP、UDP、IPRAW等)或PPPoE SOCKET與PPPoE服務器之間的操作,開發者可根據項目需求自行選擇。

圖3 端口連接流程圖

表3 S1_MR功能表

2.3 W5300數據發送和接收

在對以太網協議芯片W5300初始化和端口設置并連接成功后,便可以進行數據傳輸。首先客戶端主動發送連接請求數據包SYN;服務器則執行偵聽命令,等待客戶端連接。圖4以本系統中SOCKET1為例介紹W5300數據發送和接收流程。

在TCP模式下,當ALIGN=1時,RX接收到的數據包內只含有有效數據,主機可以從S1_RX_RSR寄存器直接獲取RX的數據包長度;否則數據包由2Bytes的PACKET-INFO和有效數據組成,數據包信息包含在PACKET-INFO內,數據包長度保存在S1_RX_FIFOR寄存器中讀取[11]。數據以包為單位讀取,數據包長度作為數據讀取循環控制量。當數據包字節長度為奇數時,數據最后一個字節為啞字節,需要直接丟棄。

當數據發送完成后,端口中斷寄存器S1_IR(4)自動置1,并需要通過FPGA向W5300S1_IR(4)寫1以清除中斷標志位。

圖4 W5300數據發送和接收流程

3 實驗驗證

本設計中,采用了TCP/IP通信協議,實現了客戶端和服務器兩個網絡系統之間的數據傳輸。端口連接成功后,首先由客戶端向服務器發送打包后的遞增數,服務器收到數據后保存到Flash,再由測試臺通過PXI總線傳輸到電腦保存,并通過上位機軟件分解校驗。接收數據時序圖如圖5,本系統控制器采用60 M時鐘頻率,11個時鐘周期接收2 Byte數據,理論傳輸速度為87.27 Mbps。數據和校驗結果如圖6所示,結果無誤碼,無丟幀。

圖5 接收數據時序圖

圖6 上位機軟件報告和數據

此次測試共發送 5 150 437個數據包,其中1KB數據為一包。根據網絡數據開始發送和數據發送停止時間可以算出以太網數據傳輸速度。在進行多次大量測試后,均無誤碼和丟幀現象出現,以太網數據實際傳輸速度可以達到85.79 Mbps,與設計指標相符。

4 結論

提出了采用“主控制器FPGA+網絡協議芯片W5300”組成的網路數據傳輸系統,重點描述了W5300的寄存器配置流程。實踐證明系統軟件編寫容易、結構簡單、實用性強。經過大量實驗驗證,能夠實現不同設備之間零誤碼傳輸,且速度達80 Mbps以上。該系統已經在高速數據圖像傳輸工程中得到應用。