淺析PLC中定時器與計數器的設計與應用

丁國明

摘? 要:該文在對PLC定時器和計數器進行功能需求分析后,對定時器、計數器和高速計數器的控制模塊整體結構進行設計,并對其與中央控制器之間進行通信的接口與讀寫時序進行設計。最終的時序仿真結果表明,該文所研究的PLC定時器和計數器模塊工作正常,并充分利用了FPGA的并行執行特點,改進了PLC的定時器和計數器執行效率。

關鍵詞:PLC? 定時器? 計數器? 高速計數器

中圖分類號:TM571.61 ? ?文獻標識碼:A 文章編號:1672-3791(2019)09(a)-0042-03

定時器與計數器是PLC(Programmable Logic Controller,可編程邏輯控制器)中最重要的資源之一。PLC內部有眾多定時器和計數器資源,而在具體應用過程中,僅有一部分定時器和計數器資源被利用到,造成資源的浪費。為此,該文以西門子PLC S7-30為例,對PLC的定時器和計數器模塊進行重構,充分利用FPGA的并行執行特點,將PLC內的定時器和計數器資源劃分為多個并行執行的模塊,以改進PLC的定時器和計數器執行效率。

1? 總體結構設計

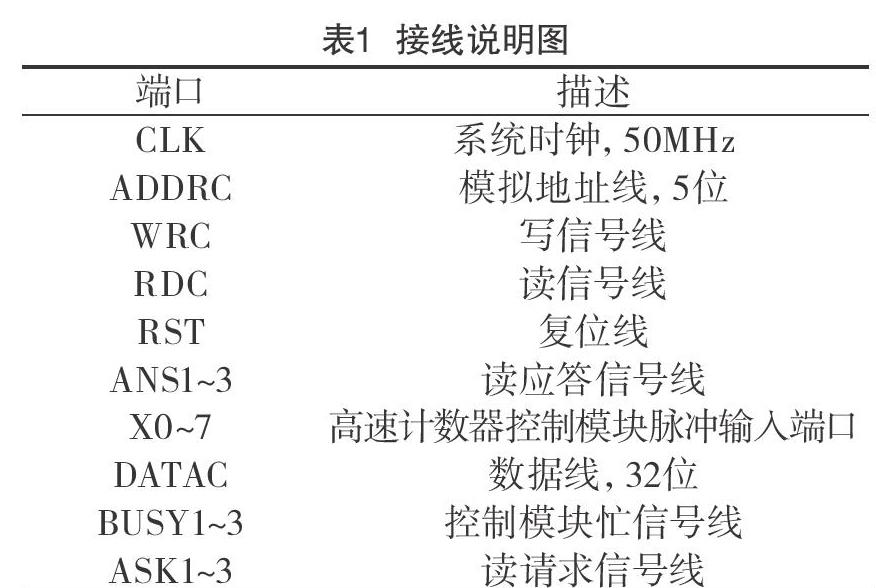

定時器和計數器控制模塊的總體結構設計如圖1所示。

其中,定時器模塊包括1ms、10ms、100ms這3種定時器,計數器分為內部信號計數器(簡稱計數器)和高速計數器兩種。按照斷電數據的保持情況,計數器分為斷電保持型計數器和通用型計數器兩種,高速計數器用于對外部高速脈沖信號進行技術,按照中斷方式工作,不受PLC掃描周期影響。

定時器、計數器和高速計數器控制模塊并行工作,通過總線和結構、功能相同的端口讀寫控制器與中央控制器進行的數據交互。

2? 控制模塊設計

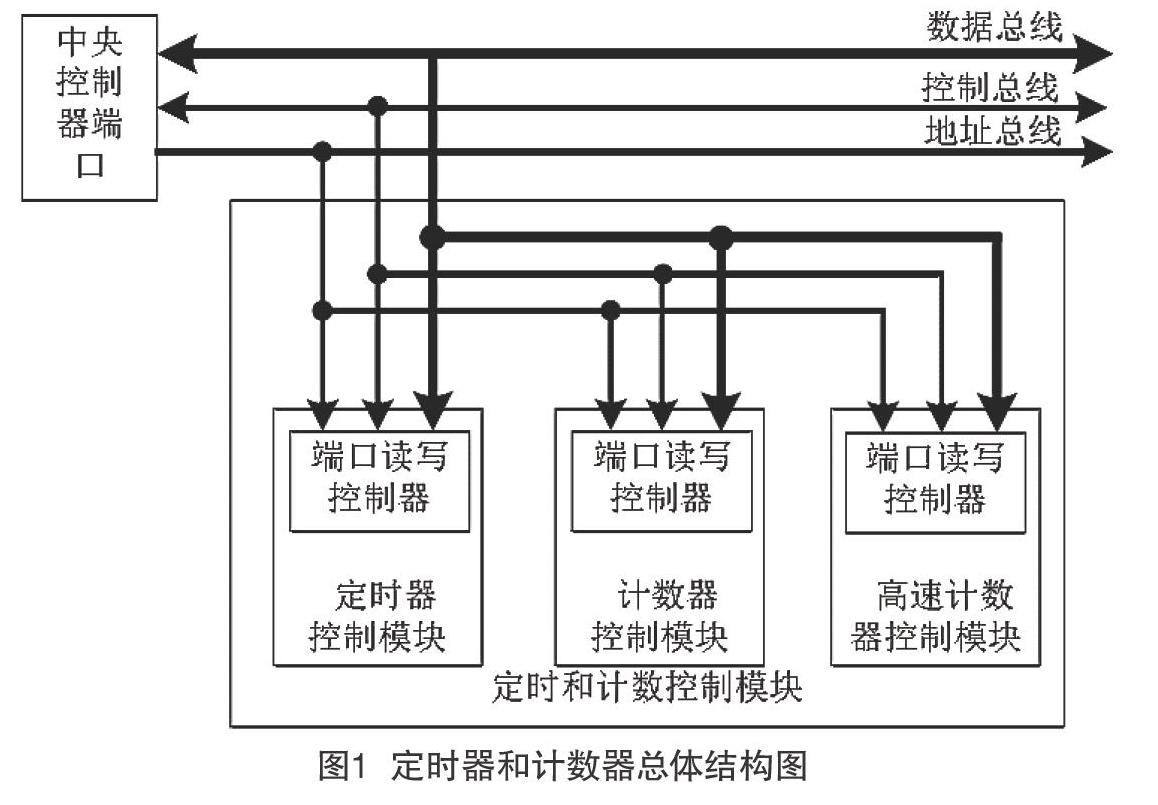

定時器與計數器控制模塊的封裝如圖2所示。

圖2的定時器與計數器控制模塊接線說明如表1所示。

其中,CLK、ADDRC、WRC、RDC、RST、DATAC端口為定時器、計數器和高速計數器共用的端口,而BUSY1/2/3、ANS1/2/3、ASK1/2/3分別為定時器、計數器和高速計數器控制模塊使用的單獨使用的忙信號線、中央控制器度應道信號線、讀請求信號線。

3? 端口讀寫控制器設計

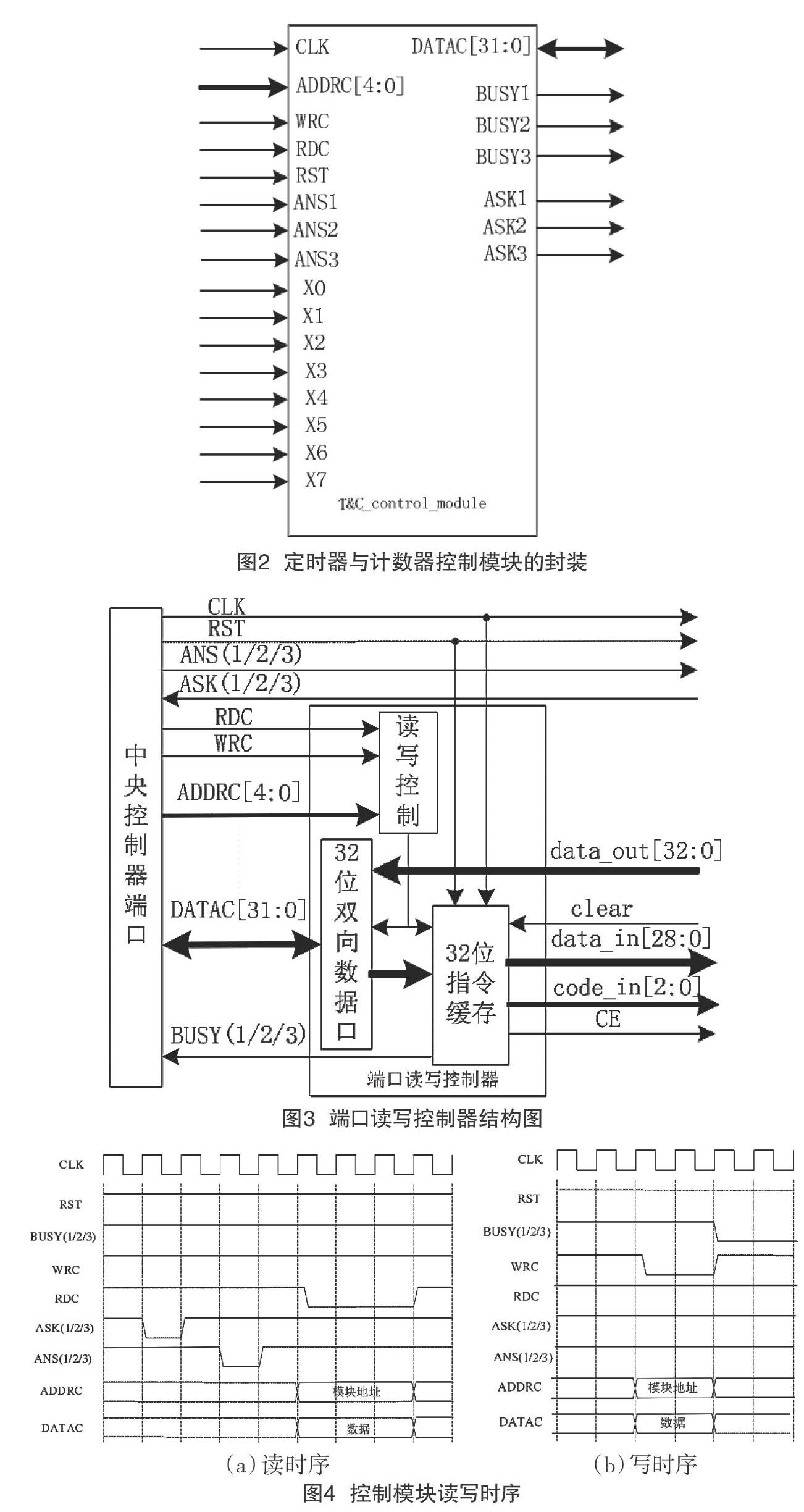

如圖1所示,定時器、計數器和高速計數器通過端口讀寫控制器實現與中央控制器的接口。定時器、計數器和高速計數器的端口讀寫控制器結構、功能均相同,其結構如圖3所示。

若RST復位線的低電平保持時間超過40ns,則觸發RST復位,RDC讀信號線、WRC寫信號線、ASK讀請求信號線、讀應答信號線均為低電平使能。CE指令執行標志線,當CE、BUSY線為低電平時,實現數據存儲。由RDC、WRC和ADDRC狀態,控制組合邏輯三態門構成的I/O口,決定讀寫控制器狀態,和數據的輸入輸出控制。端口讀寫控制器的指令由3位code_in線輸出的D29~D31指令類型,和29位data_in線輸出的D0~D28指令數據組成32位指令。若clear線接收到來自指令執行線發送的指令執行結束信息時,設置BUSY線和CE線為高電平,并清除32位指令數據。

控制模塊的讀寫時序設計如圖4所示。

如圖4所示,當中央控制器檢測到BUSY忙信號輸出線的電平狀態為高電平時,可實現定時器(或計數器,或高速計數器)的寫操作,DATAC、ADDRC和WRC的低電平保持30ns以上(時鐘周期為20ns)。中央控制器對定時器和計數器控制模塊進行讀寫操作控制時,首先通過ASK發送20ns的請求脈沖,然后讀ANS上讀來自中央控制器的20ns的應答脈沖,最終通過設置RDC低電平,后可從DATAC線中讀取60ns的數據。

參考文獻

[1] 徐曉宇,李克儉,蔡啟仲,等.基于FPGA的PLC并行執行定時器/計數器的設計[J].計算機測量與控制,2016(1):182-186.

[2] 侯肖霞.關于利用PLC定時器和計數器進行長計時功能的探討[J].電氣技術,2014(2):105-107.

[3] 喬橋.由淺入深學習PLC定時器及計數器的應用[J].中國科教創新導刊,2011(28):205.

[4] 郝敏釵.PLC中定時器和計數器的配合應用[J].科技資訊,2011(12):99.

[5] 李英輝,曲昀卿,郝敏釵,等.PLC中定時器/計數器的拓展應用[J].石家莊職業技術學院學報,2010,22(4):19-21.

[6] 游珍珍.西門子S7-200PLC定時器的實際應用[J].湖南科技學院學報,2017(6):28-29.

[7] 吳國偉.S7-200 PLC定時器的實際應用[J].裝備制造技術,2016(5):165-167.

[8] 甄天作.淺談PLC中定時器的用法及其精度的影響[J].中國高新技術企業,2016(6):76-77.

[9] 陸雪影.基于PLC技術的并行定時器設計研究[J].科技與企業,2016(4):99.