一種浮地磁控憶阻模擬器設計與特性分析

(常州大學信息科學與工程學院,江蘇常州213164)

二十世紀七十年代,根據電路變量組合完備性的原理,蔡少棠教授預測了直接關聯電荷和磁通兩個變量的電路元件— “憶阻器”的存在性[1],并建立了憶阻器件與系統理論[2]。近十年前,惠普實驗室Strukov等[3]在 《自然》上首次報道了憶阻器的物理實現,從而迅速激發了憶阻器及其應用電路的研究熱潮。但是因為憶阻采用的納米技術,在具體實現和制作上存在著巨大的困難,目前還未作為一個實際的元件走向市場。因此設計一種憶阻等效電路并用其替代實際憶阻器進行實驗和應用研究具有重要意義。

文獻[1]中最早提出了憶阻模擬器概念及其設計方法,其后出現了多種采用已有的模擬分立元器件實現憶阻的等效電路,如基于HP TiO2憶阻[3+4]、二次和三次非線性磁控憶阻[5-7]等數學模型的等效實現電路,以及利用模數混合電路和超大規模數字電路實現的電路[8]。上述等效電路都是以輸出端“接地”方式工作的,不能任意接入電路,在應用時會受到一定的限制。因而,文獻 [9-12]提出了“浮地”方式的等效電路。文獻 [9]中基于通用電路元器件提出了一種浮地憶阻等效模擬電路,使用運算放大器和乘法器以及電阻、電容實現,但是該等效電路輸出端電流io實際上是由外圍電路決定的,而不是輸入端流進的電流i,意味著自身不能確保兩端的輸入和輸出電流相等,該憶阻等效電路不支持用于模擬規范式憶阻元件。文獻 [10]基于文獻 [9]的電路,采用兩個電流傳輸器AD844作為電流鏡,解決了電流不相等的問題。文獻 [11]基于電流傳輸器,與乘法器AD633、接地電容以及部分電阻設計了一種新的浮地電路模擬器,并進行了硬件電路實現。文獻 [12]采用四個AD844組合成了第二代電流傳輸器,實現了另一種新的浮地憶阻模擬器。因此采用電流傳輸器作為電流鏡是實現浮地憶阻模擬器較為可靠的方案。

本文基于憶阻的定義提出了一種新的磁控憶阻模型,采用通用模擬集成電路芯片完成了該憶阻浮地電路模擬器的設計。該憶阻模型由線性電阻和隨時間變化的非線性電阻兩部分構成,本文定義一個非線性電阻參數對其頻率特性進行分析,闡述憶阻伏安特性中 “8”字型緊磁滯回線變化的機理,并通過Multisim仿真軟件和硬件電路測試研究驗證其基本的電特性。

1 磁控憶阻的浮地電路模擬器設計

對于一個憶阻元件的定義是:如果一個二端元件,在任一時刻的磁通量φ(t)和電荷量q(t)之間存在代數關系

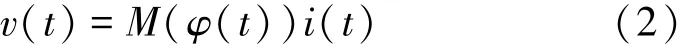

這一關系可以由φ-q或q-φ平面上的一條曲線所確定,則此二端元件稱為憶阻元件。當式(1)由電荷的單值函數表示時,即φ(t)=φ(q(t)),稱其為電荷控制型憶阻;相應地,當式(1)由磁通的單值函數表示時,即q(t)=q(φ(t)),稱其為磁通控制型憶阻。因此,磁通控制型憶阻(簡稱磁控憶阻)流過電流i(t)和兩端電壓v(t)之間的伏安關系可表示為

其中,M(φ(t))=1/W(φ(t));

W(φ(t))=dq(φ(t))/dφ(t)。

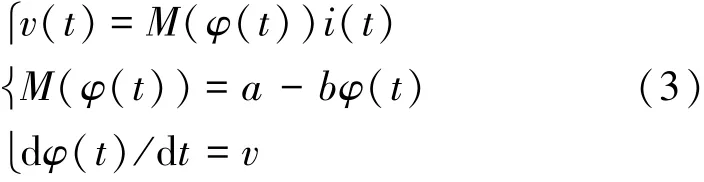

式中:W(φ(t))是磁控憶阻的憶導;M(φ(t))則為憶阻。由此,本文新提出的一種磁控憶阻模型可描述為

式中:a、b是正常數。

由式(3)可知,對于憶阻M(φ(t)),有

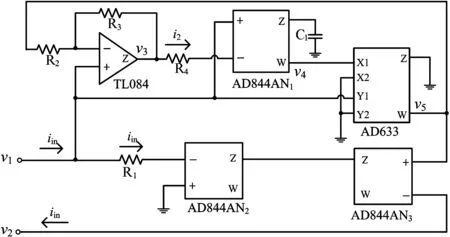

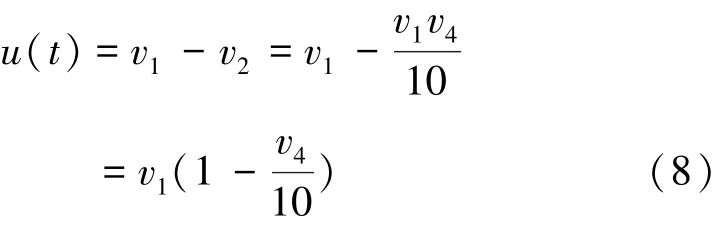

所以電路模擬器設計包括三部分工作:一是電壓積分電路的設計,實現磁通φ的功能;二是控制電路設計,實現式(4)的功能;三是電流產生電路以及電流鏡像電路的設計,實現浮地功能。其中,主要涉及到電流積分以及乘法運算等,上述運算關系可采用通用運算放大器、乘法器等模擬集成芯片實現。為使所設計的憶阻模擬器可以方便地任意接入電路使用,需要考慮其二端口的浮地設計。具體實現電路如圖1所示,這里,模擬器端口電壓為u(t)=v1-v2,端口電流為iin。

圖1 有源浮地磁控憶阻電路模擬器Fig.1 A flux-controlled floating memristor emulator

圖1中,AD844AN為電流傳輸器,具有以下特點:v+=v-,vw=vz,i+=0,i-=iz。 AD844AN2與AD844AN3構成電流鏡像電路,由于AD844AN的負端電流跟隨 Z腳電流,所以輸入電流iin從AD844AN2負端傳輸到AD844AN3負端進行輸出,實現浮地的功能,其中,輸入、輸出電流iin=v1/R1,電壓v2=v5。

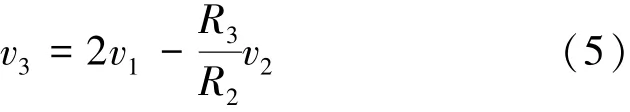

運算放大器TL084與電阻R2、R3實現減法運算,v3電壓為

當R3=R2時, 有v3=2v2-v1。

AD844AN1與R4電阻以及電容C1構成了積分運算電路,v4為電容C1上的積分電壓,則

對于磁通φ有φ(t)=∫udt,所以,式(6)可寫為

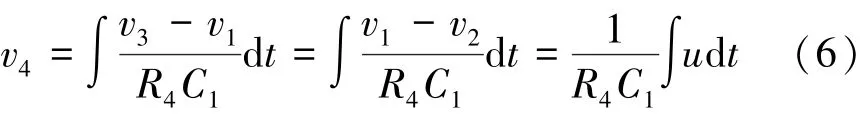

對于四輸入乘法器AD633芯片,主要完成積分電壓v4與輸入端電壓v1之間的乘法運算,W端口為輸出電壓v5,根據乘法器AD633的工作原理,輸出電壓v5=v2=v1v4/10。所以由上述分析可得圖1所示憶阻電路模擬器的二端口電壓為

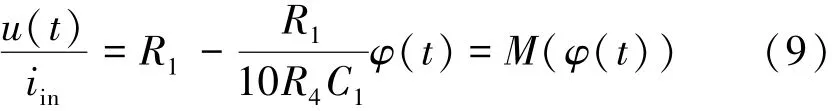

將v1=R1iin代入式(8),可得

將式(9)與式(4)比較可知,當a=R1,b=R1/(10R4C1),圖1所示電路實現了本文所提出的磁控憶阻模型。本文所設計的磁控憶阻電路模擬器參數為:R1=R2=R3=R4=20 kΩ,C1=1 μF。

2 浮地憶阻模擬器的基本電特性分析

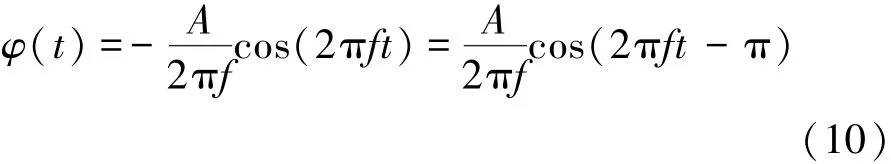

對于圖1提出的磁控憶阻模擬器,假設輸入電壓u(t)=Asin(2πft),其中,A為幅值、f為頻率,則

將上式代入式(4),可得

可見,該憶阻由線性電阻和隨時間變化的非線性電阻兩部分構成,而非線性電阻隨著信號頻率的增大逐步減小到零。定義一個非線性電阻參數k為

可以看到,參數k取決于輸入信號的幅值A和頻率f。當頻率增加或者幅值減小時,k減小;反之,k增大。同時還應注意到,R4電阻和電容C1構成的時間常數也會影響k值,信號頻率要與時間常數相適應。具體可分為以下三種類型:

1)當k趨近于0,即輸入信號頻率無窮大時,憶阻非線性特性消失,表現為線性電阻;

2)當k趨近于1,即時,憶阻的緊磁滯回線將達到最大;

3)當k遠遠大于1,即f?20πR4C1/AR1,輸入信號的周期大于模擬器電路的時間常數時,憶阻的磁滯回線消失。

在圖1所示電路參數設置下,在憶阻模擬器端口施加不同的交變激勵電壓,采用Multisim軟件研究本文所設計的憶阻模擬器的基本電特性。在圖1的端口施加正弦電壓u(t)=Asin(2πft),選取A=4 V和f=100 Hz,測試輸入電壓u(t)和輸入電流i(t),可得結果如圖2所示,其中,(a)為正弦電壓激勵下憶阻模擬器的電壓和電流時域波形,(b)為正弦電壓激勵下磁控憶阻模擬器在電流-電壓平面上的I-V回線。從圖中可看出端電壓和電流具有相同的零點,但流經憶阻的電流峰值超前于憶阻兩端的電壓峰值,即表現出 “記憶”特性,同時其伏安關系曲線具有 “8”字型緊磁滯回線特性。

進一步地,基于Multisim仿真平臺,在圖1所示電路的端口施加正弦激勵電壓u(t)=Asin(2πft),分別改變電壓的幅值A和頻率f,觀察憶阻的電流與電壓之間的曲線。為了比較不同頻率及不同幅值變化時憶阻的電流-電壓關系曲線的變化情況,畫出不同正弦電壓信號激勵下,本文所設計的磁控憶阻模擬器的電流-電壓關系曲線如圖3所示,其中,(a)為固定幅值4 V,取不同的頻率;(b)為固定頻率20 Hz,取不同的幅值。由圖3可見,當在圖1所示電路端口施加正弦交變電壓時,其電流與電壓同時過零點,電流-電壓關系曲線呈現緊磁滯回線。當固定激勵信號的幅值時,隨著頻率的逐漸增大,I-V回線逐漸向內收縮,直至退化為一條直線。結果說明,當激勵信號頻率很高時,憶阻將退化為線性電阻,而失去其記憶性;當固定激勵信號的頻率時,隨著電壓幅值的逐漸減小,I-V回線逐漸向內收縮,直至退化為線性函數。仿真結果顯示憶阻模擬器輸入端口的關系曲線不僅與輸入電壓的頻率有關,而且與輸入電壓的幅值有關,這與上文中非線性電阻參數k分析的結論是一致的。

圖2 正弦電壓激勵下憶阻模擬器的伏安特性Fig.2 Current-voltage characteristics of memristor emulator with sinusoidal voltage stimulus

3 硬件電路實現及性能測試

圖1所示的硬件電路實現的實物圖照片如圖4所示。其中,U2、U3、U4選取電流傳輸器AD844N芯片,U1選取運算放大器TL084芯片,U5選取乘法器AD633JN芯片,并在積分電容上并聯一個電阻Rm,以避免積分器U2的DC電壓積分漂移。

圖3 不同正弦電壓激勵下的緊磁滯回線Fig.3 Pinched hysteresis loops under different sinusoidal voltage stimuli

圖4 磁控憶阻器的硬件電路Fig.4 Hardware circuit of the flux-controlled memristor

在v1、v2端加入正弦激勵電壓,分別改變電壓的頻率和幅值,測量本文所設計的憶阻模擬器的端口特性,其測量結果如圖5所示。其中,橫坐標代表端口電壓,縱坐標代表端口電流;圖(a)中固定輸入正弦信號激勵幅值為4 V,頻率分別取20,40,1 kHz,測得不同頻率下磁控憶阻模擬器的伏安特性曲線;圖(b)為固定輸入正弦信號激勵頻率為20 Hz,幅值分別取4,3,2 V,測得不同幅值下磁控憶阻模擬器的伏安特性曲線。

圖5 不同正弦電壓激勵下的I-V回線Fig.5 Pinched I-V loops under different sinusoidal voltage stimuli

可以看出,低頻時設計的磁控憶阻模擬器的伏安特性曲線在第一、三象限中呈斜 “8”字形狀,隨著頻率的逐漸增大,斜 “8”字I-V回線逐漸變窄,最終退化為一條直線;當激勵信號幅值減小時,I-V回線單調縮小,最終變成一個線性函數,這與電路仿真結果相吻合。

4 結論

憶阻具有廣泛的應用前景,然而實際的憶阻器僅存在于實驗環境中,其商品化還需要一個漫長的過程,根據其電學特性構建其等效電路模型來進行研究具有重要意義。本文通過分析憶阻的定義,提出了一種新型磁控憶阻模型,并基于電流傳輸器AD844等通用電路元器件構建了可任意接入電路使用的浮地憶阻電路模擬器。該憶阻值由線性電阻和隨時間變化的非線性電阻兩部分構成,由非線性電阻參數分析了該憶阻模型的頻率特性,結論表明非線性電阻受輸入信號的幅值和頻率以及電路中R4電阻和電容C1構成的時間常數的影響。基于Multisim軟件,對不同交變電壓信號以及不同參數設置下的電流-電壓關系進行了仿真,完成了硬件電路的搭建與測試。實驗結果表明:所設計的磁控憶阻模擬器具有斜體“8”字緊磁滯回線特性,與理論上的憶阻模型特性相吻合。同時,通過修改本文電路的控制電路模塊,如增加乘法器等,還可實現二次、三次等磁控憶阻電路模擬器。本文研究結果進一步充實了憶阻理論成果以及實驗手段,為憶阻在電子學領域的應用提供了一種器件模擬實體。