VDMOS 橫向變摻雜終端的優化與設計

(西南交通大學微電子研究所,四川成都 611756)

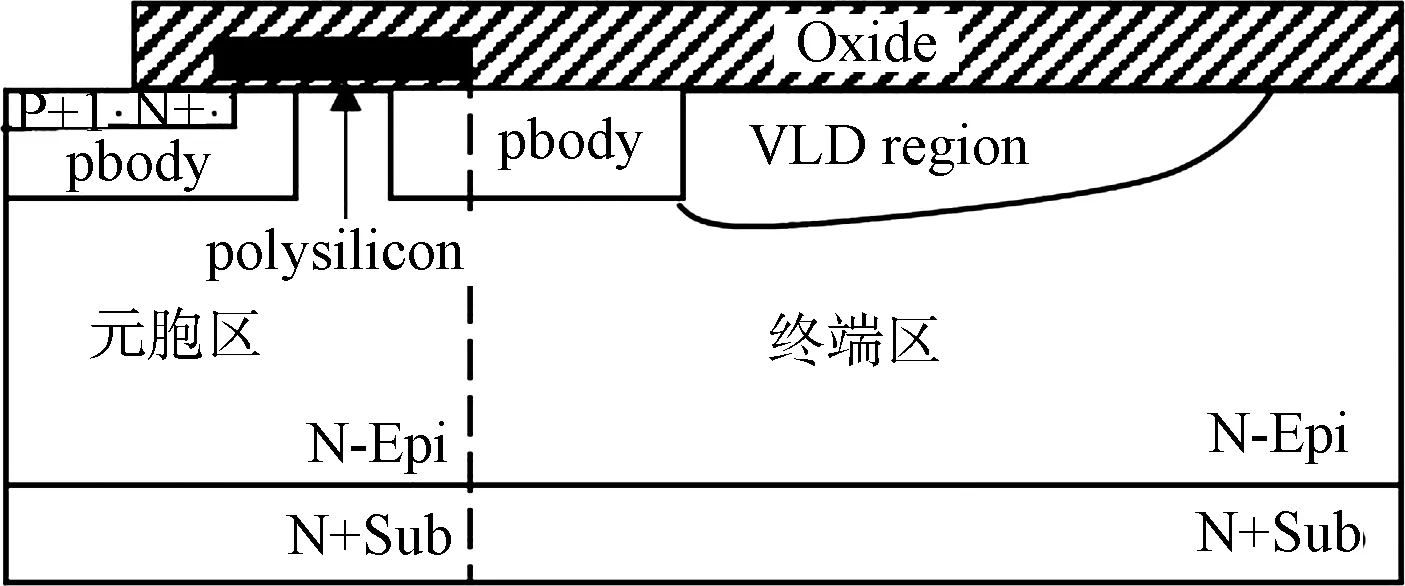

功率半導體器件中VDMOS(Vertical Double Diffusion Power Metal-Oxide-Semiconductor)是一種常見的器件,VDMOS器件的結構由元胞區和終端區兩部分組成,VDMOS器件的主要參數是擊穿電壓、閾值電壓、導通電阻;而元胞區決定器件的閾值電壓和導通電阻,終端區決定了器件的反向擊穿電壓。

目前VDMOS在工業中經常使用的終端有以下幾種:場板(Filed Plate,FR)、場限環(Filed Limiting Ring,FLR)、結終端擴展(Junction TerminationExtension,JTE)、橫向變摻雜(Variation of Lateral Doping,VLD)[1]。

其中,橫向變摻雜技術通過改變器件終端摻雜區的開窗實現降低表面電場的作用,在反向偏置下使整個VLD區完全耗盡,PN結耗盡層會向終端外側擴展使耗盡區的邊界曲率半徑變大,從而有效地提高反向擊穿電壓。本文介紹了關于VLD注入開窗和掩膜間距調整的方法,借助Sentaurus TCAD仿真軟件進行驗證,在終端能夠有效地形成VLD區,且提高了反向擊穿電壓。

1 結終端的簡單理論

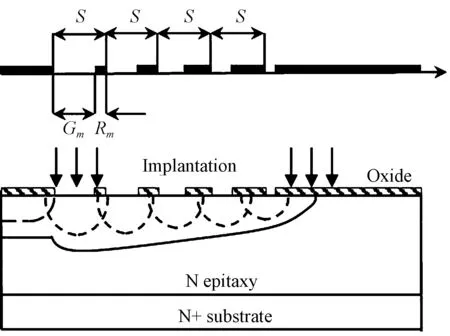

VDMOS器件的內部結構如圖1所示,其中耐壓能力是由終端結構決定,橫向變摻雜結構對提高VDMOS的擊穿電壓是非常有效的,對于橫向變摻雜結構嚴格來說只有一個PN結,就是對主結的一個延生來實現耐壓。耗盡區不能有效地擴展,將會產生電力線的聚集和節電場的匯聚,使終端的耐壓很低[2]。在以上理論條件下,直接把電荷引入來擴展耗盡區,將N區指向P區的電場抵消一部分,就會有效地緩解電場集中的現象,得到近似矩形的表面電場分布,從而提高終端的反向擊穿電壓。

圖1 VDMOS器件結構圖Fig.1 Schematic diagram of the VDMOS device structure

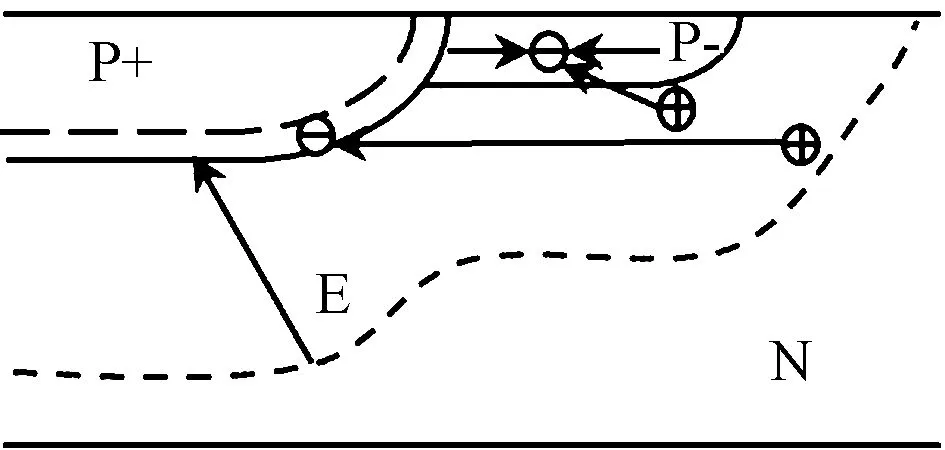

圖2為引入電荷緩解電場集中的結構示意圖,這種結構是在主結邊緣處注入一個輕摻雜的P區。

圖2 結終端延生結構Fig.2 Schematic diagram of the junction termination extension structure

當PN結工作在反向偏置時,摻雜濃度較低的P區將會全部耗盡并填滿負電荷,負電荷產生的電場線會抵消部分N型耗盡區正電荷產生的電場線,使電場的分布更加均勻,擊穿電壓得到有效的提高[3-4]。

P型輕摻雜區的注入劑量非常重要,如果P型輕摻雜區的注入劑量太大,則PN結在反向偏壓下,P型輕摻雜區就不能完全耗盡,導致電場線集中,提前在主結發生擊穿。若P型輕摻雜區注入劑量過小,主結也不能得到有效的保護,同樣會導致擊穿電壓偏低。只有適當地控制P型雜質劑量才能得到相對理想的擊穿電壓。

如圖2所示的結構對于高電壓大功率器件而言,受到一定的限制,于是提出了多演變結構。橫向變摻雜結構是越靠近主結的地方注入劑量較大,而遠離主結的地方注入量較小,通過雜質的橫向擴散,使注入的雜質連在一起,形成一個有規則的圖形[5]。如圖3所示。

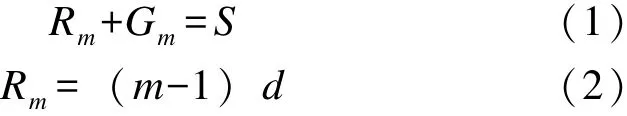

雜質的注入窗口和掩膜的阻擋窗口要求為:

式中:Rm為掩膜板阻擋窗口的寬度;Gm為注入窗口的寬度;S為掩膜板阻擋窗口和注入窗口總間距;d為注入窗口的序列號;m=1,2,3,…,n[6-8]。

圖3 橫向變摻雜結構Fig.3 Schematic diagram of the variable lateral doping structure

2 仿真結果分析

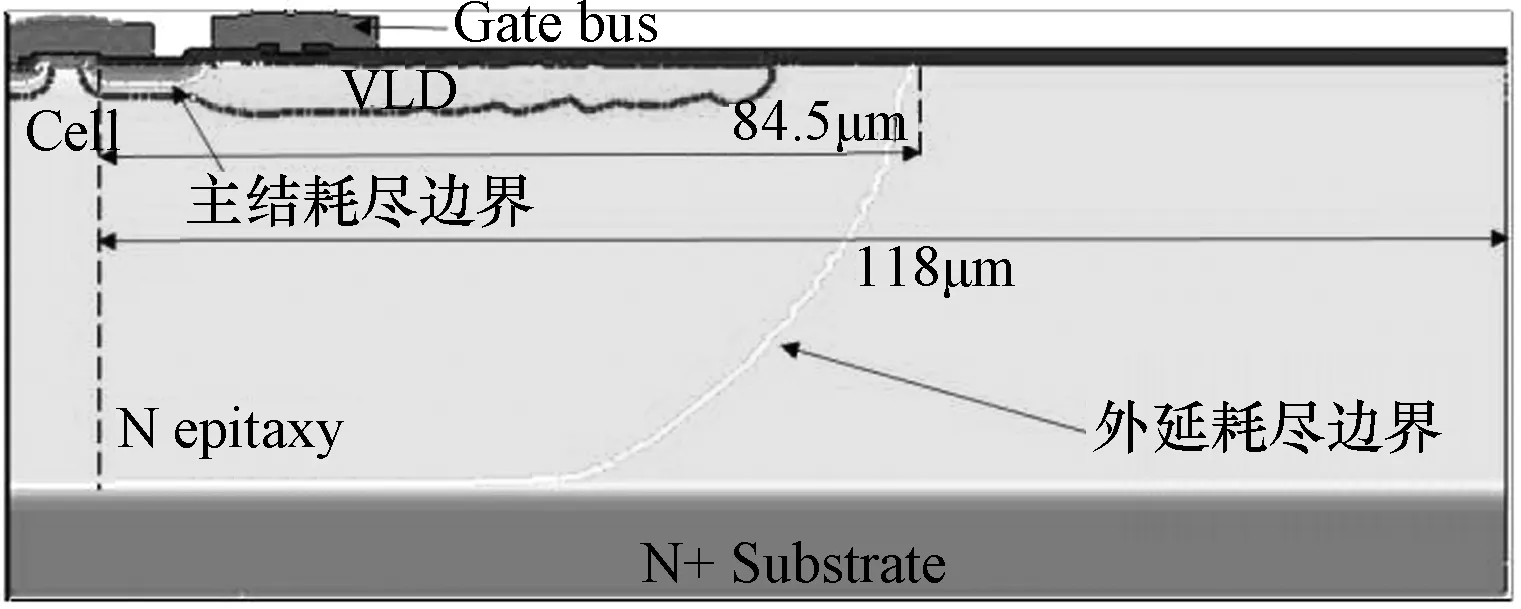

根據以上理論設計一種650 V的VDMOS終端結構,外延濃度為2.44×1014cm-3,外延厚度為56 μm,VLD 注入劑量為 2.0×1012cm-2、S=8 μm,VLD的最大結深為5.8 μm。利用Sentaurus TCAD仿真工具對橫向變摻雜終端結構進行仿真,摻雜模型如圖4所示。當工作在反向偏壓時VLD區幾乎完全耗盡,P型耗盡邊界在主結處,主結耗盡邊界到外延耗盡邊界的最大橫向距離為84.5 μm,終端區總寬度為118 μm。

圖4 終端結構模型Fig.4 Model of the termination structure

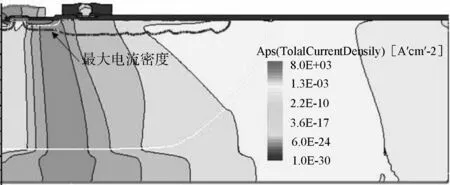

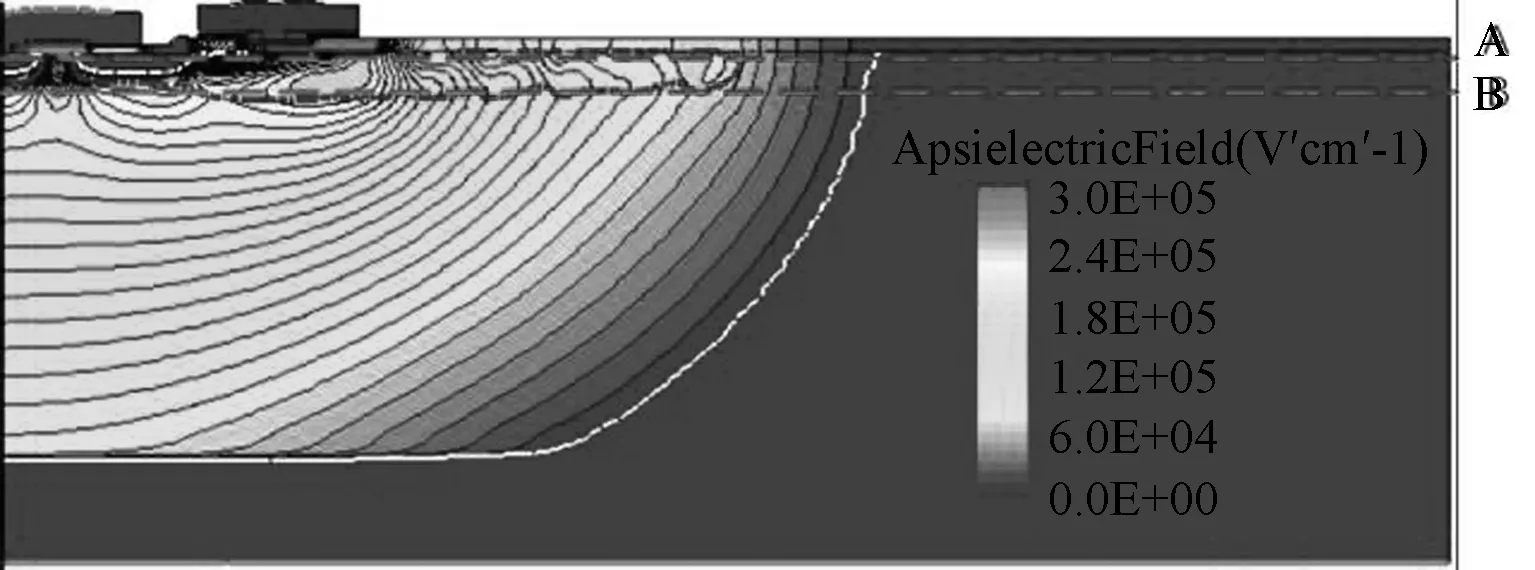

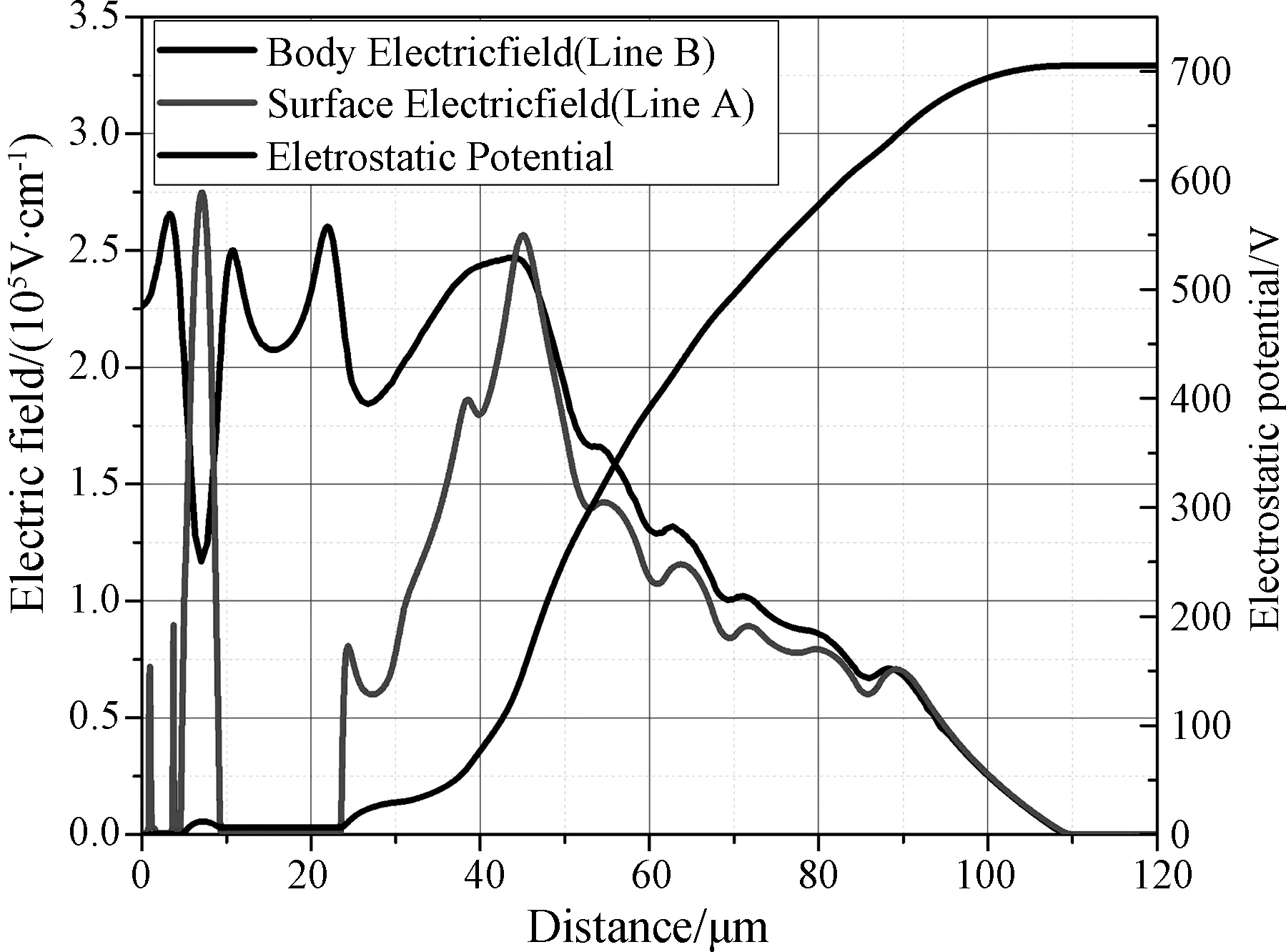

圖5為擊穿時的電流密度分布模型,從中可以看出最大電流密度在主結邊緣處,使耐壓達到最大,此處也是終端的擊穿點。圖6是電場分布模型,最大電場為3.0×105V·cm-1出現在氧化層中。在電場模型中分別截取了兩條曲線,其中切線A為硅表面電場,切線B為體內電場。

圖5 電流分布模型Fig.5 Model of the current distributions

圖6 電場分布模型Fig.6 Model of the electric field distributions

圖7是電場分布和表面電勢曲線。從圖7中可以看出主結處的最大電場為2.68×105V·cm-1,橫向變摻雜區的最大電場為2.50×105V·cm-1,由于崩潰點發生在主結處,那么在這種摻雜下的崩潰電場也為2.68×105V·cm-1。橫向變摻雜區的最大電場接近崩潰電場,說明該設計下橫向變摻雜區發揮了最大限度,橫向變摻雜區的橫向耐壓占整個終端耐壓的99.01%。

圖7 電場分布和表面電勢曲線Fig.7 Electric field and potential near the device’s surface

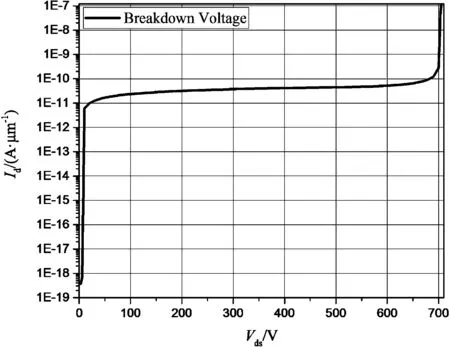

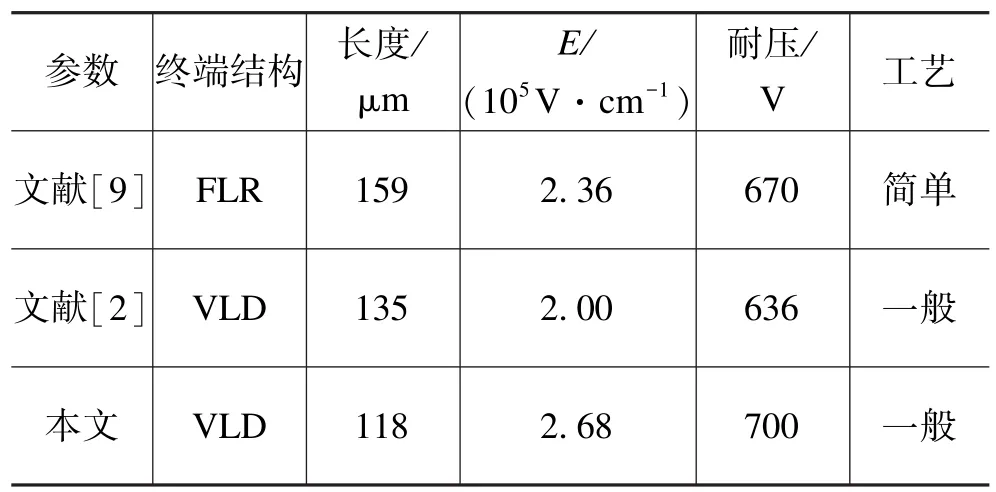

終端工作在反向偏置的擊穿曲線如圖8所示,擊穿電壓為700 V。根據設計的外延參數得到元胞區的仿真耐壓為750 V,終端耐壓的效率為93.33%,而傳統的FLR終端結構效率只有80%[10]。與其他文獻終端結構設計的比較,如表1所示。

圖8 終端的擊穿電壓曲線Fig.8 Characteristic curve of breakdown voltage on termination

表1 不同終端結構的比較Tab.1 Compare to different termination structure

3 結論

通過橫向變摻雜技術設計了一款650 V的終端結構,終端結構的長度為118 μm,仿真得出的擊穿電壓為700 V,最大電場為2.68×105V·cm-1。與文獻[8]相比終端長度縮短了25.8%,有利于減少芯片成本提高晶圓利用率。但在工藝上相比FLR結構終端要復雜一些。