一種支持源代碼級調試的全芯片仿真技術*

, ,

(中國電子科技集團公司第三十八研究所, 安徽合肥 230088)

0 引言

隨著半導體工藝的快速發展,以及“摩爾定律”所預言的晶體管增長趨勢,芯片規模、設計復雜度都在持續不斷迅速增大,片上系統(System on Chip, SoC)已成為主流的設計技術。為了縮短IC開發周期,目前的主流設計方法是采用軟件與硬件同時開發的手段,在實體硬件還沒有就位之前,軟件開發調試一般在系統仿真平臺上進行。在項目早期構建功能完備并支持源代碼級調試的全芯片仿真平臺能夠大幅提升目標軟件的開發效率,對整個項目的順利完成以及芯片產品的迅速推廣具有重要意義。

使用完全基于Verilog HDL硬件描述語言的數字前端仿真平臺[1-4]可以保證系統的周期精確性與功能完整性,但存在仿真速度慢且無法實現源代碼級調試的缺點。只能通過指令級或者匯編級的調試發現問題再反向追溯到高級語言的源代碼,不僅調試難度大而且效率低下。

使用基于C/C++的純軟件仿真方法[5-8]建立的目標機模型可以支持源代碼級調試且具有描述能力強、抽象層次豐富、仿真速度快等諸多優勢,但是在一個較大規模的全芯片系統中想要同時獲取所有子模塊對應的軟件模型難度較大,在實際操作中幾乎很難滿足。另一方面,由于到目前為止,工業界IC設計還是廣泛采用基于硬件描述語言Verilog HDL,因此基于Verilog HDL的前端數字仿真IP庫相當豐富。如果能夠有效地結合兩類不同的模型建立可源碼級調試的系統級仿真平臺,則對于早期開展目標機相關的操作系統程序及硬件驅動程序都具有重要意義。

本文針對以上問題,首先在第1節介紹基于SystemC[9]的純軟件虛擬仿真方法并分析其特點;第2節提出了一種基于VPI技術的可支持C語言源碼級調試的全芯片混合仿真方法并通過實際工程應用證明其有效性;最后總結全文。

1 SystemC軟件建模方法

基于片上網絡的復雜SoC電子系統的設計需要使用先進的系統級描述語言對其進行描述。SystemC是由OSCI(Open SystemC Initiative)提出的一種基于C++的統一建模平臺,其本質是在C++的基礎上添加了硬件擴展庫和仿真核,這使得SystemC可以在不同的抽象級別對復雜電子系統建模,解決了傳統C++語言在描述硬件時不具有并發性、時序概念等缺陷,從而可以在系統級用高級語言統一描述軟件和硬件行為。SystemC基本體系結構框架如圖1所示。

SystemC中關鍵類的繼承關系如圖2所示,其最底層是一個節拍式仿真內核,由sc_simcontext類封裝。其他常用的關鍵類型如下。

1) 模塊(sc_module)

一種層次化實體,可嵌套其他模塊和過程,一般一個完整的SystemC仿真系統可由大量模塊經實例化后互聯組成。

2) 過程(sc_process)

用來描述模塊的具體功能,可由事件觸發,多個過程可并行執行,SystemC支持3種不同的過程類型:方法過程(sc_method、線程過程(sc_thread)及時鐘線程(sc_cthread)。

3) 接口(sc_interface)

定義了一組方法實現目標,但是不實現。

4) 通道(sc_channel)

實現了接口中定義的方法,分為基本通道和層次化通道。

5) 信號(sc_signal)

用來實現各個過程之間的通信,SystemC提供了多種信號格式來滿足從寄存器傳輸級(Register Transmit Level,RTL)到功能級等不同抽象級的模擬。

6) 事件(sc_event)

用來觸發各個過程的開始以及暫停,通常多個事件組成一個敏感列表(sensitive list)共同控制一個過程的狀態。

7) 時鐘(sc_clock)

時鐘在同步電路設計中是一個非常重要的角色,本質上是一種特殊的信號,為仿真過程提供了時間基準。

由于SystemC中添加了專門用于硬件描述的類庫和仿真內核,使之可以在抽象層次較低的RTL層次對系統進行描述。尤其是SystemC支持延遲賦值這一硬件特殊行為,通過支持Δ延遲(delta-delay)來支持硬件信號的行為建模,Δ延遲是最小的仿真步驟,一個Δ周期包括許多估值 (evaluate)和更新(update)相,當事件調用notify()時,將在仿真環境的事件隊列中插入這個事件,用request_update()發出更新請求,在更新相時,調用update()更新信號。

另外,由于SystemC是完全基于標準C++實現的,使得其對抽象層次較高的行為級、算法級的系統任務天然地具有非常強的描述能力,同時有大量成熟的軟件庫可供使用,也較容易實現支持源代碼級調試的調試器[10-12]。

目前使用完全基于SystemC的純軟件仿真方法所面臨的主要問題是基于SystemC建立的模型庫還不夠完善,很多面向工業級應用的IP核依然缺乏;另一方面,由于歷史上Verilog HDL長期在工業界的數字前端設計領域占主導地位,因此基于Verilog HDL設計開發的模型庫是相當豐富的。

2 基于VPI技術的全芯片仿真

針對前文中對SystemC建模仿真方法的優勢及劣勢的分析,本文提出一種基于VPI技術的全芯片混合仿真方法。

VPI(Verilog Procedural Interface)是第三代Verilog HDL與C語言過程調用接口,目前已經成為IEEE 1364標準(IEEE Verilog HDL標準)的一部分,其中定義了一組標準API接口用以實現Verilog與標準C之間的通信。利用此接口,一方面可以為Verilog硬件代碼添加額外的用C實現的系統函數以彌補Verilog行為級描述能力的不足;另一方面,可以在軟件代碼中根據需要直接以后門方式讀寫Verilog硬件代碼中的仿真部件(如reg,wire,memory等),VPI技術為軟硬件混合仿真提供了必要條件。

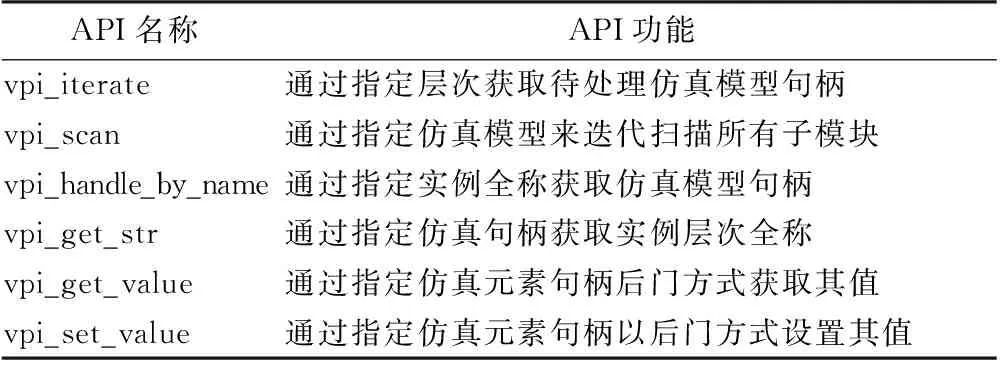

一些關鍵的VPI接口及其概要描述如表1所示。

表1 VPI中常用API概述

通過使用VPI技術可以實現全芯片級的軟硬件混合仿真平臺的搭建,將系統中復雜度最高、運算量最集中的指令執行模塊使用周期精確的軟件模型構建,同時對其他缺乏周期精確軟件模型的模塊直接使用Verilog HDL數字電路模型。因為目標機是由軟件實現的,因此自然地可以使用Socket編程方法實現本地Jtag Server進程與遠程軟件集成開發環境IDE(Integrated Development Environment )中運行的Jtag Client進程之間的通信,且由于使用了VPI技術,因此軟硬件模型之間的通信一方面可以通過傳統的端口連接實現,另一方面也可以通過VPI定義的API接口實現,如圖3所示。

圖3中最左側模塊可認為是有調試需求的指令執行部件,如CPU,DSP等,因此使用SystemC建立其周期精確的模擬;最右側使用Verilog模型可能是因為其軟件建模困難,或者已存在成熟的商用IP核;中間的模塊可以視為一個橋接功能模塊,一方面它與軟件模型之間通過TLM[13](Transaction Level Modeling,一種基于SystemC的事務級仿真框架)方式通信,通過C++函數調用接口nb_transport_bw/nb_transport_fw來傳遞被包裝成generic_payload(TLM中指定的數據幀格式)的數據幀,另一方面它通過sc_signal

“魂芯”多核DSP[14]是一款完全由中國電子科技集團公司第三十八研究所自主研發的面向高性能電子應用領域的通用DSP。由于該款芯片面向高端應用,因此其支持多種高速外設,而同時獲取或者構建所有這些外設控制器的周期精確的軟件模型是不現實的,同時也沒有必要,而邏輯最復雜同時也是計算量最密集的計算內核模塊其周期精確的軟件模型是可用的。基于以上事實,在該款DSP的實際設計中使用了本文提出的基于VPI技術的混合仿真方法為其構建了軟硬件混合仿真平臺,該平臺的大致結構如圖4所示。圖中的頂層是全芯片層,其中包含眾多的Verilog硬件模型,如AHB,Uart,RapidIO,PCIE等,而內核計算模型則是由SystemC實現的周期精確的模型(其內部實現了Jtag進程),另外在內核內部中還嵌入了一個DMAC(DMA Controller)硬件電路模型,整個混合仿真平臺既保證了系統的完整性,同時還支持在遠端IDE上進行基于源代碼級的軟件開發。

由于該混合仿真平臺使用周期精確的軟件模型描述計算內核,因此仿真速度大概是純硬件仿真速度的10~100倍(由目標機運行的應用程序決定),同時由于此平臺包含了幾乎所有高速外設的Verilog HDL模型,因此它也是功能完備的。在芯片流片的窗口期該平臺支撐了操作系統、驅動程序等目標機相關生態軟件的開發、調試,為大幅縮短產品研發周期起到了關鍵作用。

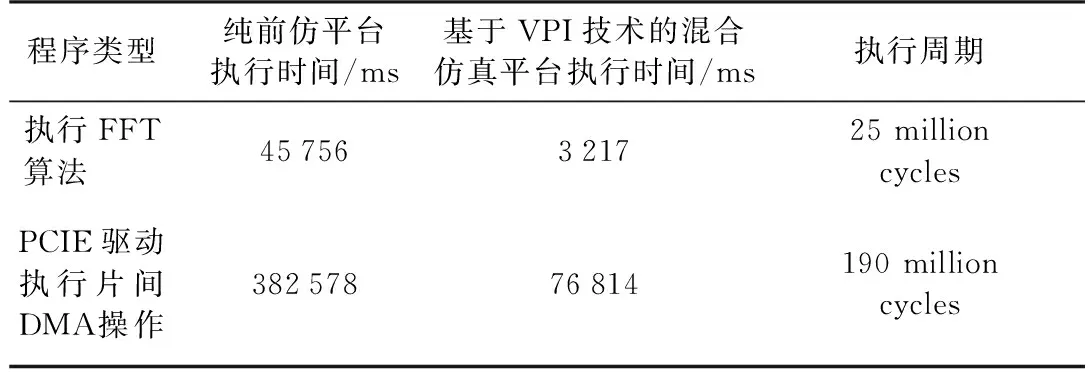

具體的執行效率對比如表2所示,第一項顯示了外設無關的程序在前仿平臺和混合仿真平臺在執行效率方面的對比(執行FFT算法),可以顯然地發現在完成同樣的仿真周期數的前提下,本文提出的混合仿真方法在執行效率方面相比純RTL的前仿平臺提升了大約1~1.5個數量級。而第二項顯示了一種PCIE驅動程序調試情景下的執行效率對比(通過PCIE執行片間DMA),由于存在內核與外設RTL模型的周期級交互,因此混合仿真平臺的執行效率有所下降,但仍然遠遠領先于純前仿平臺,大約提升了0.6個數量級。

表2 純前仿平臺與VPI混合仿真平臺的執行效率對比

3 結束語

在IC設計早期建立支持高級語言源碼級調試的全系統仿真平臺對于提升嵌入式軟件開發效率具有非常重要的意義。基于C++的SystemC仿真方法具有描述能力強、仿真速度快、可用軟件庫豐富等優點,但是目前工業界中大量使用的還是基于Verilog HDL的IP核,基于SystemC實現的周期精確的仿真模型相對還比較匱乏。在實際工程應用中試圖搭建功能完備的純軟件仿真平臺難度較大,可能需要放棄系統的完整性,而系統功能完整性對于操作系統軟件以及硬件驅動程序的開發是非常必要的。本文提出一種基于VPI技術的全芯片混合仿真方法,通過后門讀寫的方式完成軟件模型與硬件模型的交互,一方面保證了系統的完整性,同時支持多種源碼級調試手段。最后通過將該方法在一款實際DSP設計中的應用說明了本文提出方法是可行的、有效的。

另外,本文提出的混合仿真方法在執行效率方面還有進一步提升的空間。由于使用了VPI編程接口,因此使得系統軟硬件模塊的裁剪變得更加靈活和自由,一方面,可以在面向某些特定需求的仿真時,根據需要裁減掉一些當前場景下無關的大型復雜的硬件模型;另一方面,當周期精確不再是系統必需的特征時,可以使用TLM方法進行行為級建模,進而進一步大幅提升執行效率。以上是下一步研究的重點內容。