1553B總線模塊上電啟動異常故障的分析與解決

曹興岡 樊江鋒 韓 晨

(中國航空計算技術(shù)研究所,陜西 西安 710068)

1553B總線模塊上電啟動異常故障的分析與解決

曹興岡 樊江鋒 韓 晨

(中國航空計算技術(shù)研究所,陜西 西安 710068)

機(jī)載計算機(jī)在系統(tǒng)上電時,1553B總線模塊出現(xiàn)上電啟動異常。從故障機(jī)理,時序邏輯和復(fù)位電路等方面分析,通過常溫、高低溫環(huán)境下的信號波形反復(fù)測試。分析定位為上電復(fù)位電路中的某電容導(dǎo)致上電復(fù)位信號爬升緩慢,產(chǎn)生抖動,引起1553B總線模塊上電啟動異常現(xiàn)象,對于此類現(xiàn)象采取有效措施,消除故障。

復(fù)位電路;上電啟動;信號抖動

上電啟動是機(jī)載計算機(jī) 1553B總線模塊的重要性能之一,在系統(tǒng)測試和應(yīng)用時,存在一些問題,嚴(yán)重影響了機(jī)載計算機(jī)系統(tǒng)功能正常運(yùn)行,解決1553B總線模塊上電啟動異常問題,對于機(jī)載計算機(jī)系統(tǒng)穩(wěn)定、可靠運(yùn)行具有重要意義。

1 故障現(xiàn)象

機(jī)載計算機(jī)整機(jī)上電時,CPU模塊串口打印信息顯示上總線1553B總線模塊或下總線1553B總線模塊初始化不成功。

2 故障分析

CPU的串口打印1553B總線模塊初始化不成功,返回值為“0001”或“0003”,對應(yīng)函數(shù)返回值的描述信息,說明1553B總線模塊尚未準(zhǔn)備好接收主機(jī)的初始化命令,也就是1553B總線模塊上電啟動不成功。此故障一般由1553B總線模塊硬件電路造成,和系統(tǒng)應(yīng)用軟件無關(guān)。

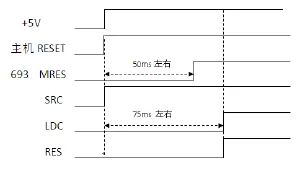

機(jī)載計算機(jī)整機(jī)系統(tǒng)軟件在上電后對1553B總線模塊有軟復(fù)位操作,下總線1553B總線模塊復(fù)位操作命令為“OW 40C,1”,上總線1553B總線模塊復(fù)位操作命令為“OW 20C,1”。40C或20C為1553B總線模塊和主機(jī)的I/O接口,主機(jī)端通過給這個IO接口寫“1”可以對1553B總線模塊進(jìn)行軟件復(fù)位,生成SRC軟復(fù)位信號,SRC信號經(jīng)邏輯譯碼后產(chǎn)生80186芯片的復(fù)位輸入信號RES,80186芯片的復(fù)位輸出信號RST和RES信號為反向的關(guān)系,其作為80186的復(fù)位輸出供系統(tǒng)使用。軟復(fù)位操作后復(fù)位信號的邏輯時序如圖1。

圖1 上電復(fù)位信號邏輯框圖

1553B總線模塊設(shè)計的主機(jī)接口電路中,IOW等控制信號在1553B總線模塊板內(nèi)設(shè)計有驅(qū)動隔離電路,使用八向驅(qū)動器驅(qū)動IOW等主機(jī)控制信號,八向驅(qū)動器芯片的使能端設(shè)計為用RST信號控制。

RST信號作為主機(jī)接口控制信號的使能控制,是防止在1553B總線模塊復(fù)位期間內(nèi)主機(jī)對1553B總線模塊進(jìn)行任何操作。故障1553B總線模塊上電復(fù)位時RES信號存在抖動,80186芯片復(fù)位不完全時,會出現(xiàn)RST信號輸出常高的現(xiàn)象,見圖2。

圖2 RES信號抖動造成80186不啟動

通過上述分析可以看出,主機(jī)接口電路設(shè)計合理,I/O接口軟復(fù)位操作不能復(fù)位1553B總線模塊是由于1553B總線模塊自身上電復(fù)位信號RES抖動,不能正常復(fù)位80186造成。

2.11553B總線模塊復(fù)位電路分析

1553B總線模塊80186處理器的的輸入復(fù)位信號RES的邏輯由GAL實(shí)現(xiàn),邏輯表達(dá)式為:RES = RESET & MRES & SRC & LDC。

其中RESET為系統(tǒng)復(fù)位,MRES為1553B總線模塊的上電復(fù)位,SRC為軟件復(fù)位,LDC為XC1765和XC3042邏輯加載完成標(biāo)志信號。

1553B總線模塊的復(fù)位信號邏輯輸出,可以看出 1553B總線模塊的上電復(fù)位由復(fù)位芯片的復(fù)位信號MRES決定。

2.1.1上電復(fù)位分析

1553B總線模塊的上電復(fù)位電路由復(fù)位芯片實(shí)現(xiàn),復(fù)位芯片的復(fù)位信號MRES在+5V輸出達(dá)到4.65V 50ms后復(fù)位結(jié)束,MRES信號置高。

故障 1553B總線模塊的復(fù)位由復(fù)位芯片復(fù)位輸出信號MRES決定,復(fù)位芯片芯片的復(fù)位MRES輸出從0V到5V的爬升需要1.6ms,其中在0.8V~2.0V的三態(tài)區(qū)的爬升時間為300us左右,期間大約有20us時間GAL邏輯輸出RES信號一直抖動。

MG80C186芯片的手冊要求,復(fù)位信號低電平有效,復(fù)位時間應(yīng)大于4個時鐘周期,約為330ns,輸入復(fù)位信號RES抖動,低電平時間短,不滿足MG80C186芯片的復(fù)位時間的要求,導(dǎo)致芯片不能正常啟動。

2.1.2復(fù)位信號抖動原因分析

復(fù)位芯片的復(fù)位信號MRES輸出從0V到5V的爬升需要1.6ms是由于設(shè)計中MRES對地接一個0.1uF的電容,如圖3所示,C4電容導(dǎo)致了MRES爬升緩慢,GAL輸出復(fù)位信號RES抖動。

圖3 1553B總線模塊上電復(fù)位邏輯圖

復(fù)位芯片典型應(yīng)用圖中,在使用手動復(fù)位時需并聯(lián)一0.1 μF電容,同時手冊中指出,不需要手動復(fù)位時該部分電路可以被刪除。手動復(fù)位只在1553B總線模塊設(shè)計調(diào)試階段使用,產(chǎn)品狀態(tài)穩(wěn)定后,手動復(fù)位可去掉,所以 C4電容應(yīng)去掉。1553B總線模塊在機(jī)載計算機(jī)整機(jī)系統(tǒng)中支持手動復(fù)位功能,由母板總線的X_RESET信號引入1553B總線模塊,該功能和復(fù)位芯片的手動復(fù)位無任何關(guān)系,去掉C4電容不影響機(jī)載計算機(jī)整機(jī)系統(tǒng)的手動復(fù)位功能。去掉C4電容,MRES輸出從0V到5V爬升在1us內(nèi)完成,其中在0.8V~2.0V的三態(tài)區(qū)的時間為100ns左右,這種條件下GAL的輸出信號RES沒有任何抖動,見圖4,1553B總線模塊啟動正常。經(jīng)過常溫、高溫、低溫環(huán)境試驗(yàn)的驗(yàn)證,去掉C4電容后,RES信號輸出正常,無抖動,同時在機(jī)載計算機(jī)整機(jī)進(jìn)行系統(tǒng)級測試,各項測試合格,確認(rèn)去掉C4電容排除故障措施有效。

圖4 1553B總線模塊去掉C4電容RES和MRES的輸出波形

2.2FPGA邏輯加載標(biāo)志LDC

1553B總線模塊設(shè)計的RTC時鐘接口電路為FPGA芯片和串行PROM芯片實(shí)現(xiàn)。在上電過程中,須將PROM芯片中的邏輯加載到FPGA芯片中,加載過程中LDC信號常低,加載完成后 LDC信號置高,串行 PROM加載邏輯過程約需75ms。

使用FPGA芯片和PROM芯片的1553B總線模塊的復(fù)位邏輯關(guān)系如圖5所示,1553B總線模塊上電復(fù)位由LDC決定,復(fù)位信號正常,1553B總線模塊沒有任何故障。

圖5 裝焊FPGA芯片和PROM芯片的1553B總線模塊復(fù)位信號邏輯關(guān)系

故障的1553B總線模塊使用了替代芯片,裝焊FPGA芯片和串行PROM芯片狀態(tài)的1553B總線模塊在系統(tǒng)中測試正常,使用過程中未出現(xiàn)該故障。

裝焊替代芯片的1553B總線模塊和裝焊FPGA芯片和串行PROM芯片的兩種1553B總線模塊,元器件的變化導(dǎo)致了1553B總線模塊復(fù)位信號變化。裝焊替代芯片的1553B總線模塊無需串行PROM加載邏輯過程,LDC上電后直接置高,復(fù)位信號的時序關(guān)系如圖6,這時80186的輸入復(fù)位信號RES由1553B總線模塊上電復(fù)位信號MRES決定,上電復(fù)位信號抖動,造成80186不能正常啟動。

圖6 裝焊替代芯片1553B總線模塊復(fù)位信號邏輯關(guān)系

通過以上分析認(rèn)為:1553B總線模塊由于FPGA芯片和串行PROM芯片使用了其國產(chǎn)化替代芯片,從而帶來了1553B總線模塊復(fù)位信號的變化。使用替代芯片的1553B總線模塊復(fù)位信號由上電復(fù)位電路產(chǎn)生,復(fù)位芯片的復(fù)位輸出 MRES信號對GND接有1個0.1uF(位號C4)的電容,此電容導(dǎo)致MRES信號爬升緩慢,MRES通過GAL邏輯譯碼產(chǎn)生的RES信號抖動,造成80186CPU芯片復(fù)位不完整,并且導(dǎo)致RST信號輸出常高,RST信號禁止了主機(jī)的IOW信號通過驅(qū)動芯片輸入到接口電路,使軟復(fù)位操作無效。這種情況下,1553B總線模塊上電不能正常復(fù)位啟動,造成了上電后主機(jī)不能初始化1553B總線模塊的故障現(xiàn)象。

3 處理措施

通過以上分析,故障的根本原因是上電復(fù)位信號 MRES信號上接的C4電容,導(dǎo)致了上電復(fù)位信號異常,產(chǎn)品不能正常啟動,實(shí)施去掉電容C4,同時在元器件替代驗(yàn)證應(yīng)透徹分析,充分驗(yàn)證,從技術(shù)和管理上徹底消除該故障。

4 結(jié)束語

通過消除1553B總線模塊上電復(fù)位信號的抖動,解決了上電起動異常問題,同時在類似產(chǎn)品元器件替代驗(yàn)證中,應(yīng)充分考慮元器件各種參數(shù)變化和影響,驗(yàn)證充分,使得機(jī)載計算機(jī)系統(tǒng)功能、性能達(dá)到穩(wěn)定可靠。

[1] 黃波.1553B總線控制系統(tǒng)時間同步設(shè)計[J].航天控制, 2008,26(6):70-73.

[2] 馬文波,鄭宇平.關(guān)于單片機(jī)不能正常上電復(fù)位的解決辦法[J].中國科技信息,2006,(6):123-124.

[3] 解維坤.基于 ATE的 FPGA測試[J].電子與封裝,2009, 9(12):17-19.

[4] 張京晶,程甘霖,包斌.基于FPGA嵌入式的PROM接口實(shí)現(xiàn)[J].電子測量技術(shù),2013,36(1):75-78.

Analyze and solve about last electricity start abnormal of 1553B data bus

When the airborne computer at system up time, the 1553B data bus appear the start abnormal condition。Analysis from the aspect of break down mechanism, the cycle time logic and reset electric circuit,test several times about the wave of the signal under normal,high and low temperature environment,After analyze,the reason for the abnormal was caused by an electric capacity in the wire reply an electric circuit up,the electric capacity caused the signal of start upset rise slowly,and also create trembles,and then the 1553B data bus show abnormal. Adopt valid measure to this kind of phenomenon, the cancellation break down.

Reset electric circuit;last electricity start;signal trembles

TP3

A

1008-1151(2015)06-0010-03

2015-05-11

航空基金項目(2006ZC31002)。

曹興岡(1977-),男,陜西戶縣人,中國航空計算技術(shù)研究所高級工程師,研究方向?yàn)橛嬎銠C(jī)應(yīng)用。