基于FPGA的多功能信號發生器設計與實現

劉艷昌,左現剛,李國厚

(河南科技學院 信息工程學院,新鄉 453003)

0 引言

信號發生器在工業、科技、教學等領域中已得到廣泛應用,通常情況下使用較多的設計方案是利用FPGA、單片機等處理器芯片來控制專用信號發生芯片,這種設計方案與傳統采用模擬分立器件來設計信號發生器的方法相比,具有信號頻率更穩定、精度更高、信號參數易調節等優點,但存在電路設計復雜,成本較高等問題。隨著電子技術和EDA技術的快速發展和深入研究,DDS技術得到飛速發展[1],使得信號發生器的設計和實現更加容易和靈活。DDS即直接頻率合成器,與傳統頻率合成技術相比,具有頻率分辨率高、頻率切換速度快、頻率改變時相位連續性保持不變和頻率穩定度高等優點,因此極易實現信號的頻率、相位和幅度控制。

針對采用VHDL或Verilog HDL語言設計一個所需的DDS模塊存在編制源程序復雜問題,本文利用Altera公司推出的DSP Builder與MATLAB配合使用可以很方便搭建DDS模塊,然后通過SignalCompiler工具對DDS模塊進行編譯,轉化為可在QuartusII軟件中使用的VHDL文件,最終將該VHDL文件生成實體化模塊,以便與控制模塊和D/A轉換模塊配合完成基于FPGA的多功能信號發生器的設計與實現。本文設計的多功能信號發生器,可輸出正弦波、方波、三角波、鋸齒波四種基本波形及其對應調幅波性和2ASK、2FSK、2PSK三種數字調制波波形,輸出頻率范圍為1Hz~20MHz之間,輸出幅度范圍為1mV~5V且具有頻率、相位和幅度可調功能。

1 基于DSP Builder的DDS實現

1.1 DDS設計原理

DDS是直接數字式頻率合成器(Direct Digital Synthesizer)的英文縮寫,它是從相位概念出發,建立在采樣定理基礎上的一種新的頻率合成技術[2~4]。它主要由基準時鐘源、相位累加器、相位調制器、波形存儲器、幅度調制器、D/A轉換器和低通濾波器LPF組成,其中N位相位累加器是核心。DDS原理結構圖如圖1所示[5~8]。

圖1中時鐘源fc為本系統的參考時鐘,其頻率fc=50MHz,輸出信號的頻率fo、幅度和相位可由頻率控制字FCW、幅度控制字ACW和PCW字的值來控制,即通過改變不同的FCW、ACW和PCW控制字來獲得輸出不同的頻率、幅度和相位信號。設相位累加器的位寬為N(頻率輸入控制字位寬),相位調制器位寬為M,則DDS的輸出信號頻率為:

輸出信號的相位相移為:

輸出信號的相對幅度為:

1.2 DDS系統模型的建立及仿真

1.2.1 基本波和AM調制波的DDS系統模型建立及仿真

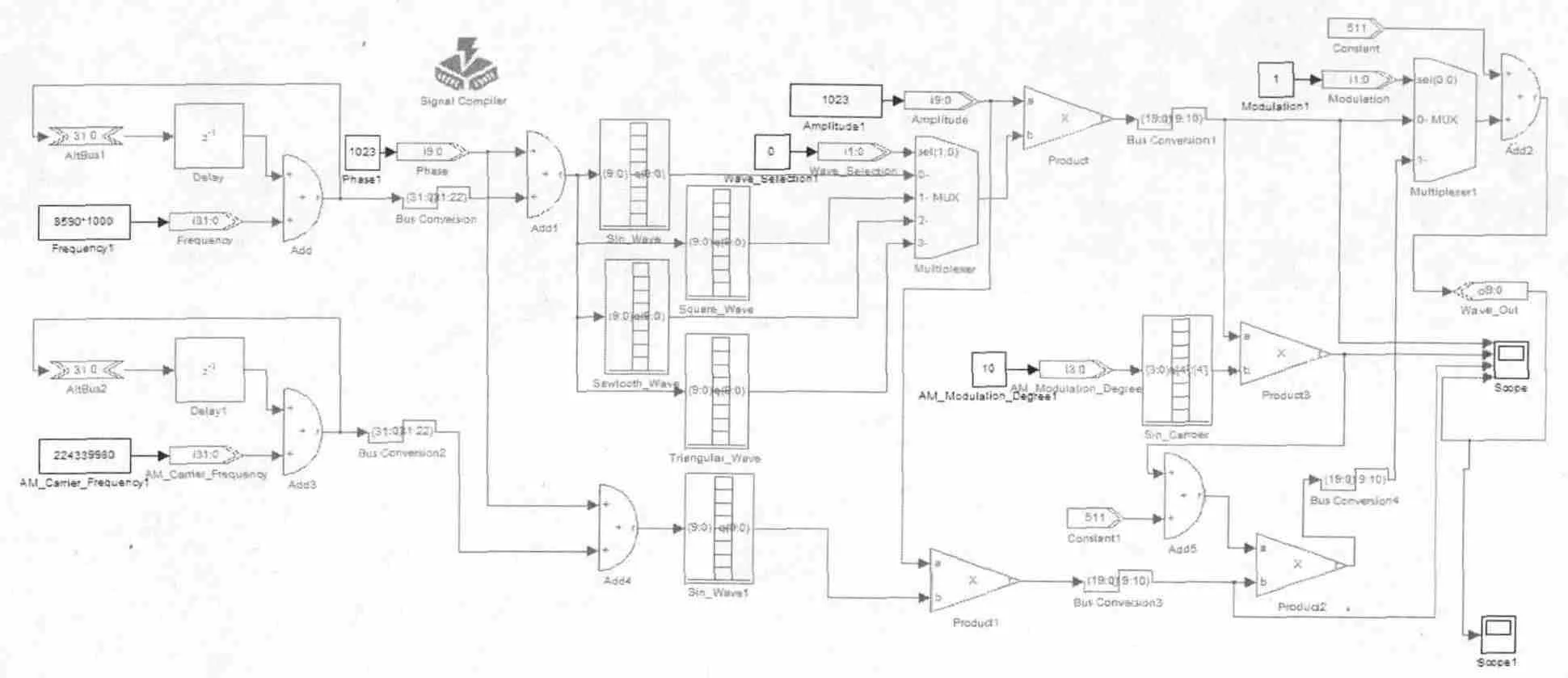

啟動MATLAB軟件,打開Simlink窗口新建一個.mld文件,然后調用Altera DSP Builder Blockset里面的模塊搭建基本波和AM調制波的DDS系統模型如圖2所示。

該系統主要由基本波形信號發生器、載波信號發生器、AM調制器和多路選擇器組成。其波形參數設置時需在“MATLAB Array”編輯框中分別輸入“511*sin([0:2*pi/1023:2*pi]),511*square(2*pi*[0:1/1023:1],50),511*(sawtooth(2*pi*[0:1/1023:1],1)),511*(sawtooth(2*pi*[0:1/1023:1],0.5))”,即可在SignalCompiler編譯過程中,自動產生1024個相應的正弦波、方波、鋸齒波和三角波數據。在搭建模塊時,數據類型采用默認設置,即有符號整型,由于D/A轉換芯片輸入數據都是無符號正數,因此在總模塊輸出時通過加法器在輸出端加511,就可把處在縱坐標負半軸的搬移到正半軸,以便在示波器上正確顯示(其他加法器也是同樣的道理)。

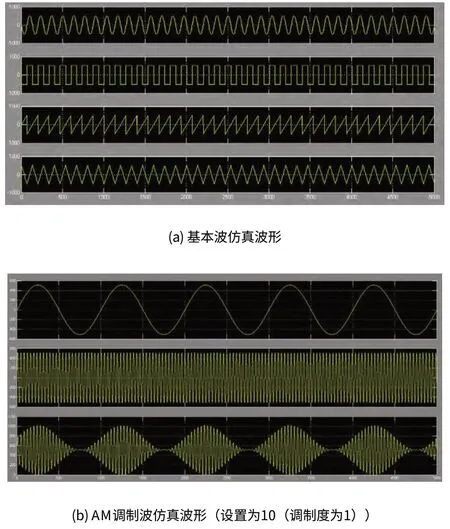

在圖2中分別設置頻率控制字為8590×1000,載波頻率控制字為224339980,幅度控制字為1023,相位控制字為1023,載波調制深度為10(即幅度控制字為1023),數據選擇器Multiplexer的波形選擇Wave_Selection控制字取0(正弦波),數據選擇器Multiplexer1的波形選擇Wave_Selection控制字取1(正弦波調制)時的仿真波形如圖3所示。

1.2.2 數字調制波的DDS系統模型建立及仿真

在1.2.1基本DDS模型設計基礎上,利用其產生的正弦波作為載波信號,以二進制數字基帶信號為調制信號,即可實現二進制數字調制信號。數字調制波的DDS系統模型如圖4所示,主要由基本DDS模型及2ASK、2FSK和2PSK數字調制模塊組成,通過改變幅度輸入字、頻率輸入字和相位輸入字即可實現2ASK、2FSK和2PSK的數字調制信號。

圖2 基本波和AM調制波系統模型

圖3 基本波和AM調制波仿真波形

按圖4參數設置完成后,將基波和載波的波形輸出接入同一個顯示窗口便可啟動仿真,其數字調制波仿真波形如圖5所示:當二進制數字基帶信號輸出為0時,多路選擇器Multiplexe、Multiplexe1和Multiplexe2選擇0通道,即2ASK輸出幅度為0,2FSK輸出低頻,2PSK輸出0相位;當二進制數字基帶信號輸出為1時,多路選擇器Multiplexe、Multiplexe1和Multiplexe2選擇1通道,即2ASK輸出幅度為511,2FSK輸出高頻,2PSK輸出π相位,當多路選擇器Multiplexe4輸入端sel為00、01和10時,可分別實現2ASK、2FSK和2PSK調制波輸出。

圖4 數字調制波系統模型

圖5 數字調制波仿真波形

2 多功能信號發生器硬件實現

2.1 DDS系統模塊的生成

在上述基本波和AM調制波系統模型和數字調制波系統模型中首先雙擊Signal Compiler圖標,然后選定Altera公司的EP2C5T144芯片類型后開始分析,可將在Simulink中設計的sin_GN.mdl和Binary_Keying_GN.mdl模型文件自動轉化為.vhdl文件,最后在QuartusII環境中打開已創建的dgnxhfsq.bdf工程文件,將得到的.vhdl轉化為sin_GN.bsf和Binary_Keying_GN.bsf文件,即為所生成的信號發生模塊硬件符號,如圖6所示。

圖6 信號發生模塊硬件符號

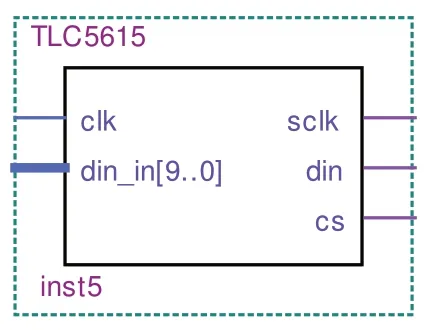

2.2 D/A轉換模塊

D/A轉換器選擇TLC5615芯片,該芯片是10位高速數模轉換器。只需通過3根串行總線就可以完成10位數據串行輸入,功耗低,使用方便。本系統只用一片TCL5615芯片,因此工作方式選擇第一種。根據TLC5615工作時序,在QuartusII軟件中通過verilog HDL語言編寫驅動程序,然后將其生成模塊硬件符號,如圖7所示。為了提高輸出波形的頻率和分辨率,D/A芯片掃描時鐘采用400MHz,這里利用QaurtusII內的IP核定制鎖相環實現對信號的倍頻。

其中clk為400MHz時鐘信號;sclk為TLC5615芯片串行時鐘輸入信號;din_in[9..0]為輸入的并行10位數據;din為經并-串轉換后的數據輸出送給TLC5615芯片輸入端;sc為TLC5615的片選信號,低電平串行數據寫入,高電平禁止。

圖7 D/A驅動模塊硬件符號

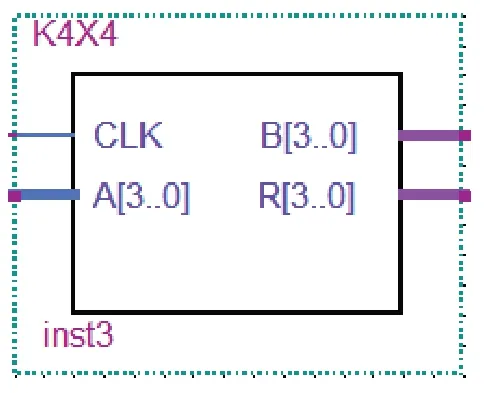

2.3 4×4矩陣鍵盤模塊

矩陣鍵盤電路采用4×4行列式結構,將4條I/O線作為行線,與4條I/O列線進行交叉,便得到16個交叉點,在每個交叉點上接入一個按鍵,就構成4×4矩陣鍵盤。在判斷具體哪個按鍵按下時,采用逐行掃描低電平方式,檢查行輸入是否處于低電平的狀態來確定。根據各按鍵實現功能,在QuartusII軟件中通過verilog HDL語言編寫其驅動程序,然后將其生成模塊硬件符號,如圖8所示。

圖8 4×4鍵盤驅動模塊硬件符號

其中CLK為50MHz時鐘信號;A[3..0]為鍵盤4位行線輸入;B[3..0]為鍵盤4位列線輸出;R[3..0]為鍵盤鍵值輸出。

2.4 鍵值輸入處理模塊

鍵值輸入處理模塊主要實現對16個輸入按鍵的具體功能進行處理,其中數字鍵10個,調制方式選擇鍵、波形選擇鍵、波態選擇鍵、調制度鍵、確認鍵和刪除鍵各1個。根據鍵值輸入處理模塊實現功能,在QuartusII軟件中通過verilog HDL語言編寫其驅動程序,然后將其生成模塊硬件符號,如圖9所示。

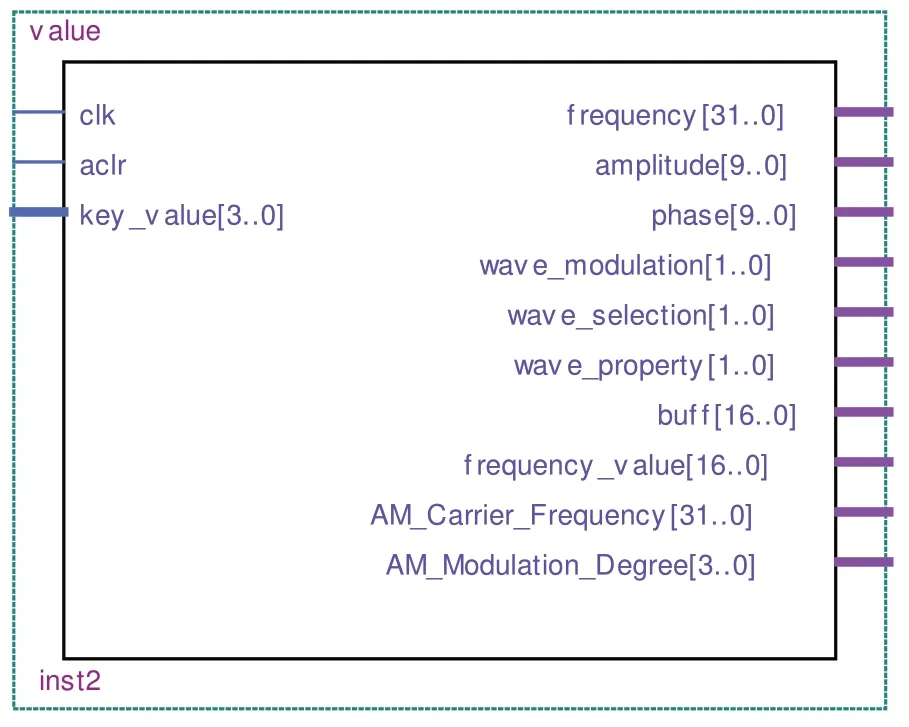

圖9 輸入鍵值處理模塊硬件符號

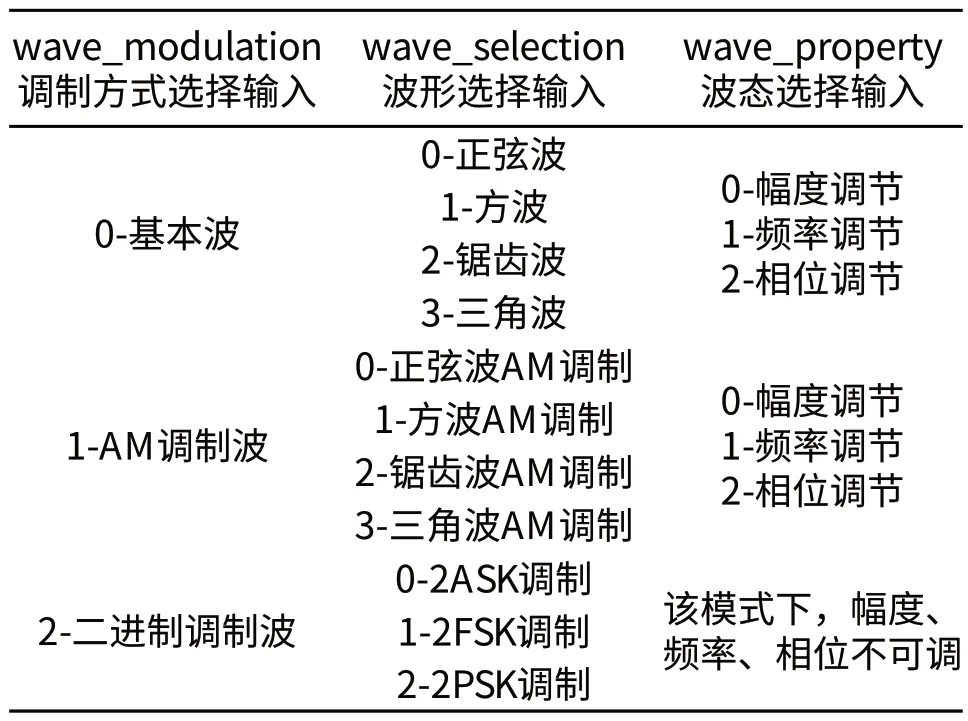

其中輸入端口key_value[3..0]為鍵值輸入;輸出端口:frequency_value[16..0]為頻率控制字輸出;amplitude[9..0]為幅度控制字輸出;phase[9..0]為相位控制字輸出;buff[16..0]為緩存數據輸輸出;frequency_value[16..0]為頻率值輸出;AM_Carrier_Frequeny[31..0]為載波頻率輸出;AM_Modulation_Degree[3..0]為調幅波調制深度輸出;其余輸出端口控制功能如表1所示。

表1 波形輸入端口控制功能

2.5 LCD顯示模塊

LCD顯示模塊采用帶中文字庫的12864型LCD液晶顯示,主要用來顯示輸出波形的頻率、幅度和相位值。根據顯示功能,在QuartusII軟件中通過verilog HDL語言編寫顯示驅動程序,然后將其生成模塊硬件符號,如圖10所示。

圖10 LCD顯示驅動模塊硬件符號

其中輸出端口:rs、rw、en、data[7..0]分別為LCD12864液晶顯示器的讀、寫、使能、數據控制端口。

3 多功能信號發生器硬件下載與系統測試

3.1 多功能信號發生器硬件下載

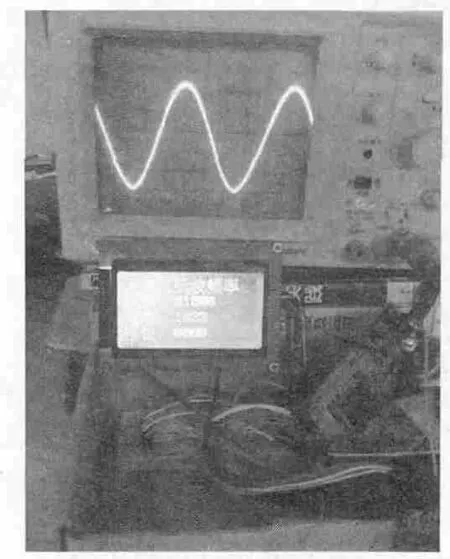

在QuartusII環境中打開已創建的dgnxhfsq.bdf工程文件,將上述各模塊添加到該工程里,將其保存后設為頂層,編譯、綜合成功后將生成的dgnxhfsq.sof文件,通過JTAG模式下載到ALTERA公司的EP2C5T144C8芯片中得到實際硬件電路。文件下載成功后,通過鍵盤調試使其輸出頻率為1KHz,幅度為3V,相位為0的正弦波,其顯示結果如圖11所示。

圖11 硬件下載結果

3.2 多功能信號發生器系統測試

為準確對系統性能進行分析,以正弦波為例從波形輸出頻率角度和幅度角度進行定量測試。采用頻率計對多組特定頻率及其穩定度進行定量測試,實測數據如表2所示。

表2實測結果表明,正弦波的輸出頻率范圍為1Hz~20MHz,其中頻率穩定度達到數量級10-5的輸出信號頻率范圍為10Hz~5MHz,且多數頻率測量點都存在正方向偏移。實測頻率存在正誤差的主要原因是由基準時鐘精確性不高和數值處理過程中取舍誤差造成的,通過改善基準時鐘的精確性和提高運算速度能夠改善該頻率精度和穩定度。

采用示波器對正弦波輸出幅度進行定量測試,實測數據如表3所示。

表3 正弦波輸出幅度數據

從表3測試數據可知,10Hz~1MHz的正弦波輸出信號幅度與滿值5V輸出相比,其最大偏差為0.2V,最小偏差0.02V,能夠滿足實際需要,且比較穩定。當輸出頻率大于1MHz時,幅度下降較大,輸出20MHz時偏差最大。其主要原因是D/A轉換精度不高和放大濾波電路增益衰減造成的,通過采用高精度D/A轉換芯片和提高濾波器帶寬及增益能夠改善這個問題。

4 結束語

本文采用MATLAB/Simulink、DSP Builder對基波、AM調制波和數字調制波的DDS系統模型進行設計、仿真和建模,利用DSP Builder中的Signal Compiller工具將圖形化建立的DDS模型轉化為可在QuartusII軟件中使用的VHDL文件,在QuartusII環境中生成硬件符號,并將其添加到工程中,然后再把各模塊連接好的頂層實體下載到目標器件中,最終實現多功能信號發生器的設計。與傳統的頻率合成方法相比不僅避免了DDS模塊編程的復雜性、節約了FPGA的邏輯資源,而且具有頻率切換時間短、頻率分辨率高、相位變化連續,功能擴充容易、成本較低、穩定度較高、抗干擾能力強、參數修改靈活和開發周期短等優點,能夠滿足實驗室的基本需要,具有廣闊的應用前景。

[1]朱鳳武,鄒麗娜,等.基于FPGA和DDS的數字調制信號發生器設計與實現[J].電子設計工程,2013,6(21):90-93.

[2]韓旭,鄭磊.基于FPGA的任意波形發生器的設計與實現[J].電子測量技術,2013,7(32):62-66.

[3]萬志江.基于FPGA的DDS IP核的研究與設計[J].微電子學與計算機,2013,8(30):98-102.

[4]張浪.DDS IP核設計及其在信號發生器中的應用[J].信息化研究,2010,10(36):46-48.

[5]王康佳,劉詩偉,孫番典.基于Matlab/DSP Builder任意波形信號發生器的兩種設計.現代電子技術,2011,3(34):179-184.

[6]劉楠.基于FPGA的DDS信號發生器的實現[D].哈爾濱:哈爾濱理工大學,2011.

[7]肖炎根.基于SOPC的DDS函數信號發生器的設計[D].長沙:中南大學,2011.