應用于ESD防護電路的抗噪聲LVTSCR組件研究

馬萬里

(深圳方正微電子有限公司,廣東 深圳 518116)

1 引言

ESD防護的基本原則就是在盡量短的時間內將盡量多的電荷通過一定的通路泄放掉。由于SCR組件的保持電壓低、單位面積的電流泄放能力高,成為目前ESD防護電路中效果最好的組件。

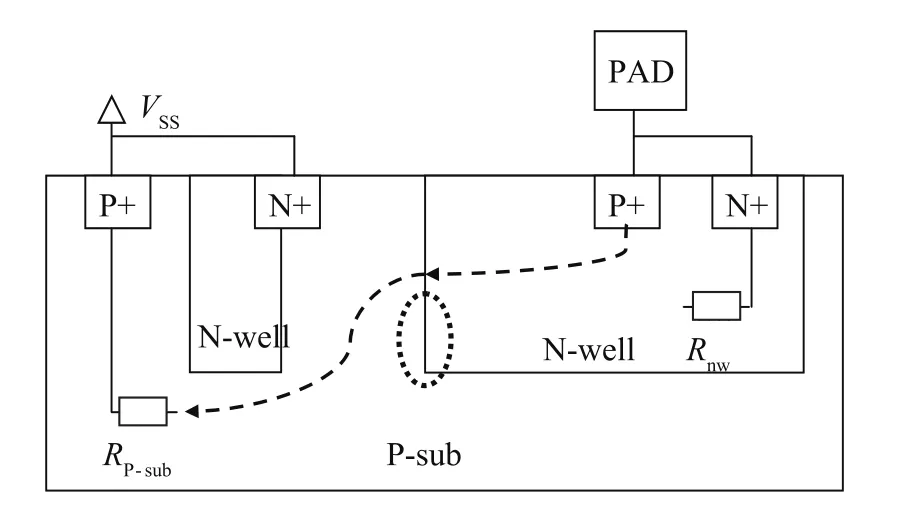

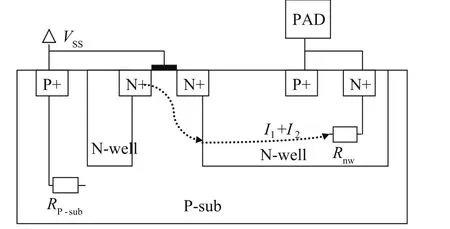

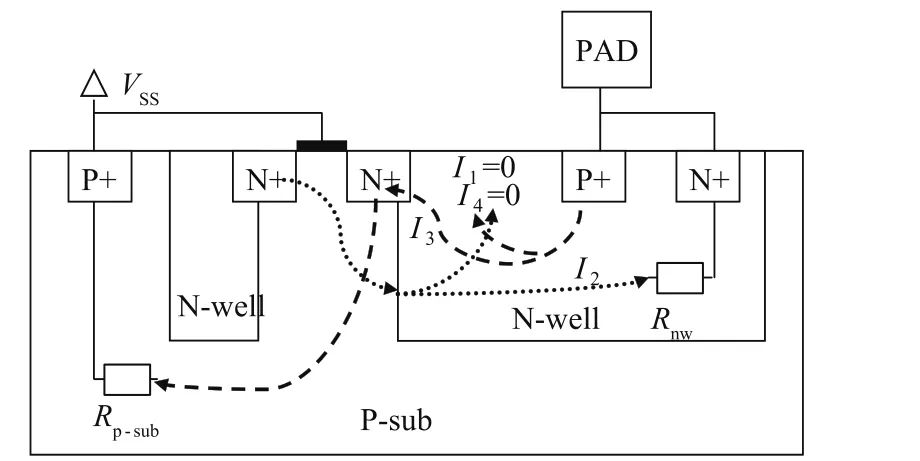

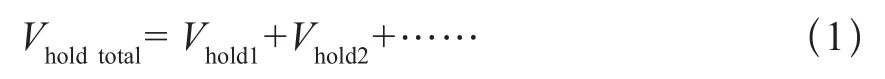

下面以ESD防護中的PS模塊(P表示在I/O端口施加正激勵,S表示VSS)說明其基本原理。如圖1所示,整體為PNPN結構,當PAD端口受到一個高壓靜電時,N-well與P-sub的結會擊穿,產生如圖1中虛線所示電流,原本P-sub電位同VSS一致,由于此時P-sub中有電流通過,當Isub×Rp-sub造成的壓降值達到一定程度時,會觸發由N+、P-sub、N-well組成的寄生NPN晶體管,產生如圖2所示的電流,N+為發射極,P-sub為基區,N-well區充當集電區。當Inw×Rnw的值達到一定程度時,會使得N-well與P+形成的PN結正偏,從而觸發由P+、N-well、P-sub組成的PNP晶體管。自此,完整的Latch up效應產生了,從PAD到VSS之間形成了一個低阻通道[1],可以釋放大量的靜電電荷。這就是SCR組件應用于ESD防護的基本原理。

2 低壓觸發的SCR(LVTSCR)

圖1 SCR用于靜電防護的基本原理

圖2 寄生NPN管的電流流向

從圖1中看到,要觸發該SCR組件,前提是N-well與P-sub組成的PN結要發生反向擊穿,亞微米的CMOS工藝中,這個觸發電壓一般在30V以上。而芯片內部的N+與P-sub組成的PN結,相比之下,由于N型一側的摻雜要濃,此結的擊穿電壓要遠低于30V。所以當遇到靜電時,還沒有等到SCR觸發,芯片內部的電路已經燒毀了。更需要說明的是,N-well與P-sub結的擊穿電壓要高于同工藝條件下MOS器件的柵氧擊穿電壓,所以必須降低SCR組件的觸發電壓。

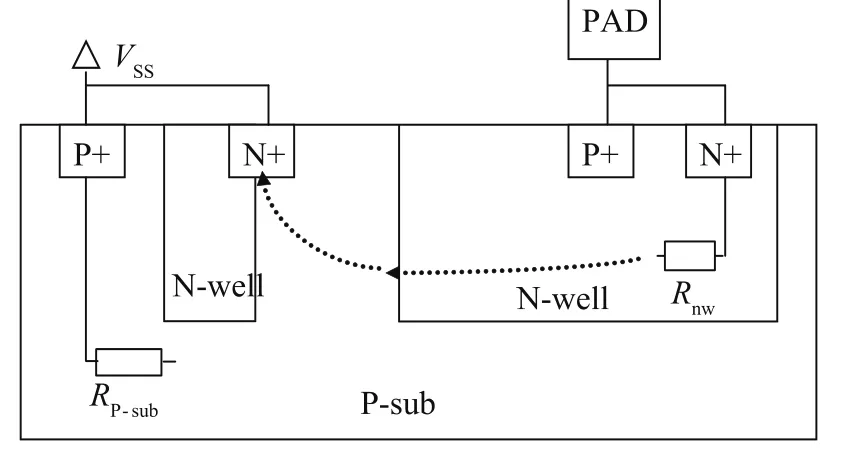

經過改進,在N-well的邊緣增加一個N+區域,這樣一來,當PAD上受到靜電沖擊時,這個N+與P-sub組成的結會先于N-well與P-sub的結擊穿,大大降低了SCR的觸發電壓[2~3]。擊穿時,產生的觸發電流的流向如圖3所示。

圖3 低壓觸發SCR的觸發過程

同時為了避免此N+與其左側的N+(如圖3所示)產生漏電,需要將兩個N+組成的NMOS管的柵極接到VSS。

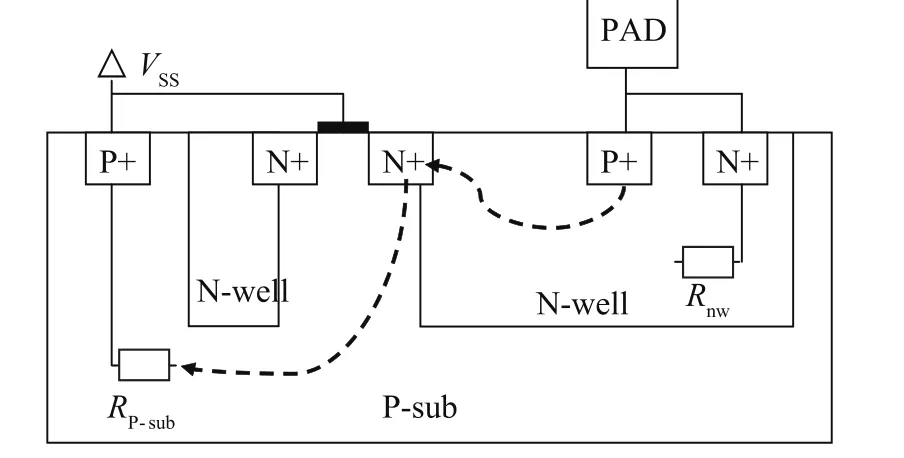

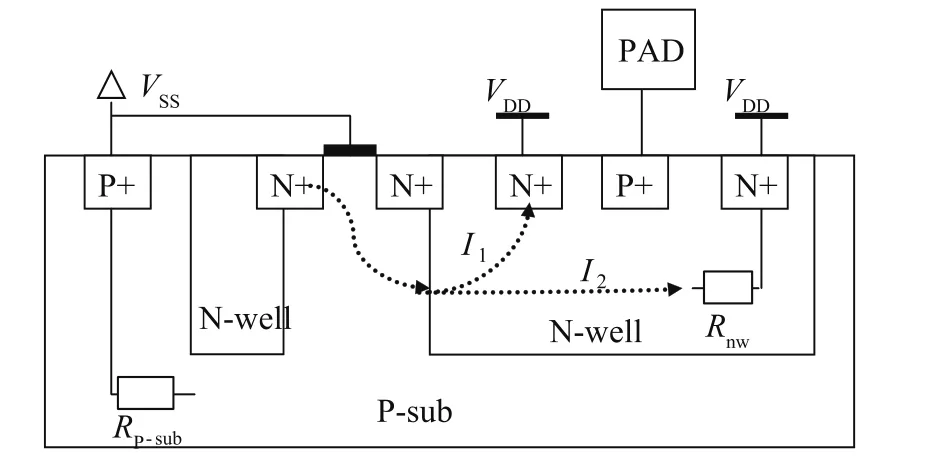

此觸發電流通過P-sub到達VSS,當Ip-sub×Rp-sub的值大到一定程度,會觸發另一組N-well與P-sub組成的結,使之正偏,也就使得由此N-well、P-sub、N-well組成的NPN管開始工作,產生如圖4所示的電流。此電流又通過了N-well中的Rnw,促使了由N-well的P+、N-well、P-sub組成的PNP晶體管開始工作,進而類似Latch up的低阻通路產生,靜電可以通過此通路泄放。

圖4 低壓觸發SCR的NPN寄生晶體管電流流向

3 噪聲干擾對LVTSCR組件的影響

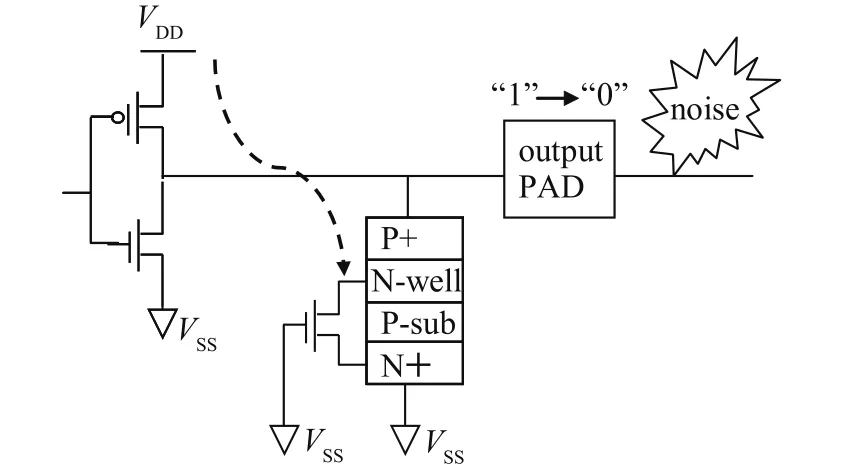

集成電路在工作時,隨時可能受到噪聲的干擾,如圖5所示,為一反相器接一用于防靜電的SCR組件,當反相器輸出高電平到PAD端口時,如果在這個時候,有噪音耦合到此電路上,極可能觸發SCR,觸發后的SCR由于保持電壓(holding voltage)很低,只有1V~2V,這會將反相器的輸出端電平拉低。

此時PAD端口得到的就不再是本來需要的高電平,而是由于SCR導通產生的低電平,這會造成電路的嚴重誤動作。并且由于VDD到VSS之間形成了一個低阻通道,還會造成嚴重的能量損耗,所以有必要考慮如何解決噪聲干擾問題。

圖5 噪聲干擾造成的SCR誤工作

4 提高LVTSCR的觸發電流

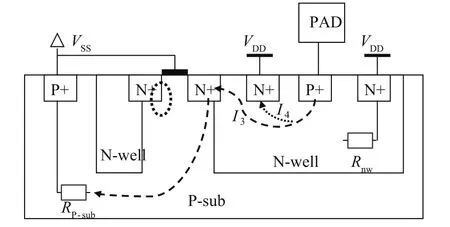

通過在N-well中增加一個N+區域,當PAD遭受到噪聲干擾時,雖然仍是N+/P-sub結被擊穿,但此時從P+流入的電流會有一部分經過新增加的N+流到VDD[4],如圖6所示的I4。直接流入P-sub的電流就少了一些。由于Ip-sub的大小決定了NPN管是否被觸發,Ip-sub小了,NPN管就不容易被觸發,如果要被觸發,就需要更強的噪聲。

圖6 高觸發電流的LVTSCR組件剖面

當噪聲強到足夠觸發NPN寄生管時,NPN管的電流(電子流)方向如圖7所示。此時進入N-well的電流有一部分被N+區分流了,如圖7中的I1。經過Rnw的電流小了,由Inw造成的電壓差也隨之變小,由N-well中的P+、N-well、P-sub組成的PNP管,因發射結正偏而觸發的難度就加大了。如果要被觸發,就需要更強的噪聲。

圖7 高觸發電流LVTSCR的寄生NPN管電流方向

對于沒有增加N+區域的常規低壓觸發SCR(LVTSCR),當PAD遭受噪聲,N-well/P-sub結擊穿時,從P+流出的電流沒有被N+分流(I4=0),如圖8所示,全部進入P-sub,Ip-sub的電流就相對大些,經過P-sub造成的電壓差就大些,NPN管被觸發也容易些。萬一NPN被觸發后,其進入N-well中的電流也全部通過Rnw,沒有I1分流(I1=0),如圖8。其由Inw引起的壓降要大一些,觸發PNP管就更容易一些。所以,不加N+區的SCR組件不能有效地抗噪聲干擾。

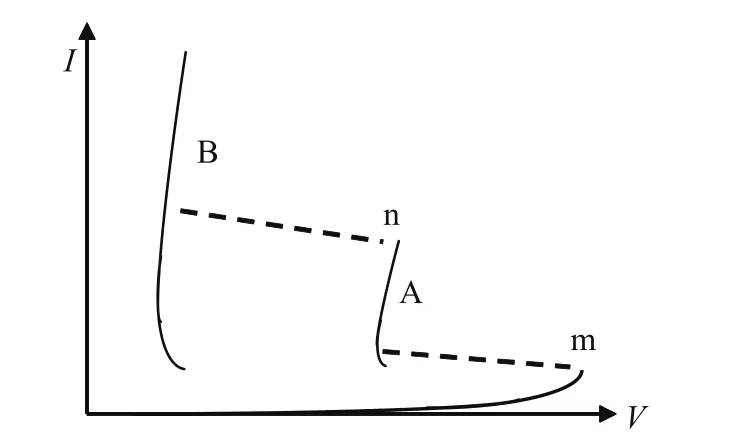

對于有N+區域的SCR結構,稱為高電流觸發的SCR(HITSCR)。對于采取HITSCR方式的ESD結構,且使用0.5μm SPDM工藝實現的芯片,測量其I-V特性,發現具有很奇特的曲線,具有二次觸發特性,如圖9所示。

第一觸發點m:V=12.1V,I= 2.0mA

第二觸發點n:V=9.3V,I=205.5mA

第一保持區A:V =7.9V,I=27.0mA

第二保持區B:V =1.2V,I=12.0mA

圖8 無N+區域的LVTSCR組件中的寄生NPN與PNP電流

圖9 HITSCR的I-V特性曲線

第一個觸發點m,是由于N+與P-sub之間的結擊穿所致,擊穿造成了低阻通路,電流急劇上升。但是由于N-well中的N+(用于分流的作用)區域存在,此時的電流還不能完全使得SCR組件中的PNP/NPN寄生管的發射結正偏,也就是說還不能觸發SCR組件進入閂鎖狀態。如果只是噪聲干擾,已經發生擊穿的N+、P-sub通路不能夠繼續維持下去。這就抑制了噪聲干擾。當存在較強靜電時,電流會繼續增大,進而會完全觸發SCR組件中的NPN、PNP寄生管導通,就進入第二觸發點n。這會形成完整的閂鎖效應,此通路的電流更大、電阻更小,就進入了第二保持區B。

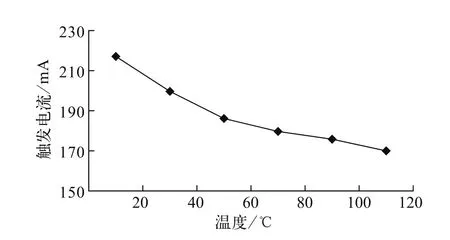

抗噪聲干擾的高電流觸發SCR組件(HITSCR)對溫度也有一定的敏感性,由于NPN、PNP管的放大系數會隨著溫度升高而變大,而放大系數越大,便可以在更小的觸發電流情況下觸發SCR組件。所以HITSCR的觸發電流隨著溫度的上升而降低,如圖10所示。不過即使在120℃,觸發電流仍舊可以達到170mA。這對噪聲干擾還是具有很強的免疫能力。

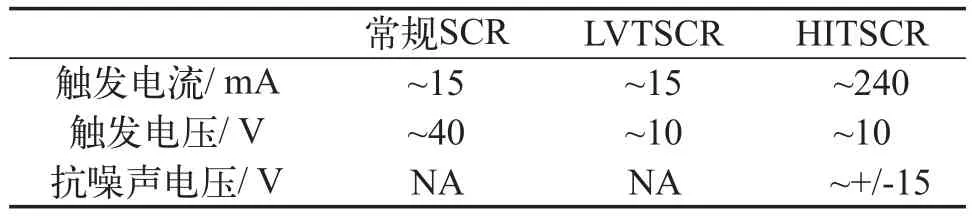

對于同樣采用0.5μm SPDM工藝流程、設計面積相同但設計結構不同的ESD防護,通過測量不同結構SCR組件的觸發電流、觸發電壓、抗噪聲能力,可以看到HITSCR確實有很強的抗噪聲干擾能力,如表1所示。

圖10 HITSCR的觸發電流與溫度關系曲線

表1 不同結構的SCR組件觸發以及抗噪聲能力對比

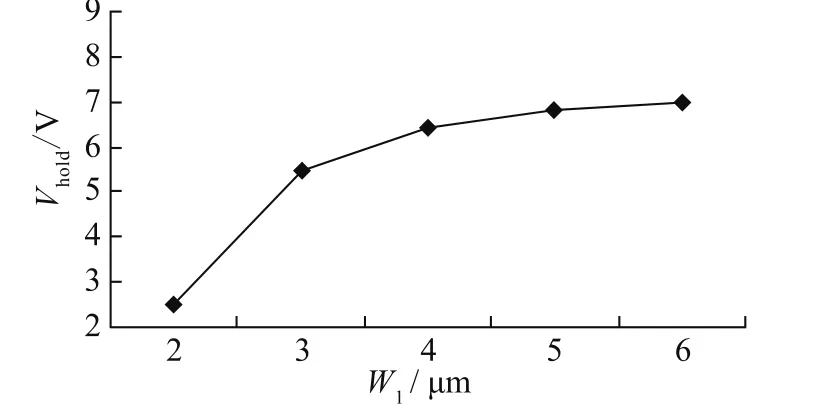

5 提高LVTSCR的保持電壓

通過提高SCR的保持電壓(holding voltage),使之比電路中的VDD電位要高,此時SCR的觸發電壓不變,但是由于高保持電壓,即使噪聲干擾觸發了SCR,噪聲干擾消失后,由于VDD電位不能夠提供足夠高的保持電壓,也不會形成持久的閂鎖效應,SCR就會自動關閉。有3種設計方法可以實現此要求。

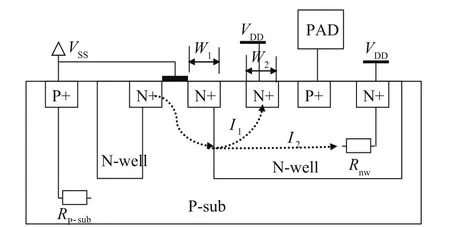

優化SCR結構,使得不容易發生閂鎖效應。比如加寬HITSCR組件中的N+區域寬度W1/W2,如圖11所示,隨著N+寬度W1的增大,對于NPN管來說,P-sub基區的橫向寬度也變大了。隨著N+寬度W2的增大,對于PNP管來說,N-well基區的橫向寬度也變大了。它們的放大系數β變小。SCR組件中NPN、PNP管發生Latch up效應的難度變大,通路中電阻增大,維持電壓也增大。但這又會影響遇到靜電時的放電效果,所以是一組矛盾關系。在實際的設計中,這點是控制難點,也是關鍵點。N+寬度既不能過大,也不能過小。如果過大,SCR組件會很難被觸發,就不能起到防靜電作用。如果過小,雖然防靜電效果好,但是又很容易受到電路中的噪聲干擾。圖12中給出了W1與保持電壓Vhold的關系。

此外,可以通過HITSCR組件的串聯使用,或將HITSCR與二極管串聯[4],也可以使Vhold的總值增大。

多個HITSCR串聯使用時,Vhold關系如下:

Vholdn為各個HITSCR的單個保持電壓。

HITSCR與二極管串聯使用時,Vhold關系如下:

Vd為單個二極管的正向導通壓降。

圖11 增大HITSCR的N+寬度提高保持電壓

圖12 HITSCR的N+區寬度與Vhold的關系

6 結論

通過在well的邊緣,設置與well同樣類型的重摻雜區域,可以有效降低SCR的觸發電壓。但這種結構在電路的應用中也極易受到噪聲干擾。

優化LVTSCR的結構,通過提高LVTSCR的觸發電流,可以在保持低觸發電壓的前提下,提高對噪聲干擾的免疫能力。通過提高LVTSCR的保持電壓,可以使得LVTSCR在被噪聲觸發的情況下,不使之繼續維持下去,同樣提高了抗噪聲干擾的能力。

[1] 董麗鳳,李艷麗. CMOS集成電路閂鎖效應抑制技術[J].電子與封裝,2010,10(9):28-30.

[2] 湯培望. SCR的I-V曲線中二次崩潰對ESD性能的影響[J].現代電子技術,2010,34(18):1-3.

[3] 李冰,楊袁淵. 基于SCR的ESD器件低觸發電壓設計[J].固體電子學研究與進展,2009,29(4):561-565.

[4] 李冰,王剛. 基于SCR的ESD保護電路防閂鎖設計[J].微電子學,2009,39(4):786-789.