基于CMOS工藝平臺反熔絲FPGA實現

陶 偉,石喬林,李天陽

(中國電子科技集團公司第58研究所,江蘇 無錫 214035)

1 引言

對于集成電路在衛星系統中的應用,設計人員可以選擇的技術包括:專用集成電路(ASIC)、以SRAM為基礎的現場可編程邏輯陣列(FPGA)、反熔絲為基礎的FPGA。對于以上三種技術,設計人員需要針對特定的應用權衡取舍各種特性,以找出最佳的解決方案。

對于多數衛星的運載艙和有效負荷設備,ASIC是具有高密度、最小重量和最低功耗的解決方案,但是缺乏FPGA所提供的靈活性。而且,把設計工具成本、校驗時間和非經常性工程費用(NRE)一并考慮后,ASIC也是成本最高的解決方案。以SRAM為基礎的FPGA優勢在于擁有高邏輯密度和高靈活性,可在衛星發射前后期修改設計,因此多用于有效負荷設備中。然而,靈活性的增加會提高系統的復雜性,并增加元件數目和功耗、降低總體可靠性。更關鍵的是由于其更容易受到宇宙輻射,產生單粒子效應(SEU)干擾。以反熔絲為基礎的非揮發性FPGA器件比ASIC和SRAM產品具有更多優勢,采用抗輻射的反熔絲FPGA,設計人員可以免除ASIC設計中那些NRE成本和工程延誤風險,并且可享有只有FPGA才能提供的設計靈活性和產品快速上市的優勢[1]。

目前國外對于反熔絲FPGA開展了很多研究[2~6],ACTEL等公司已經相繼開發出一系列的產品。主要實現方法包括MTM和ONO熔斷技術[7~8]。但由于工藝平臺的限制,國內尚未見反熔絲FPGA的報道,使我國衛星和軍事應用受到極大的限制。針對目前現狀,本文利用普通CMOS工藝,開發出一種反熔絲技術,可滿足不同應用領域的要求。

2 反熔絲單元試驗

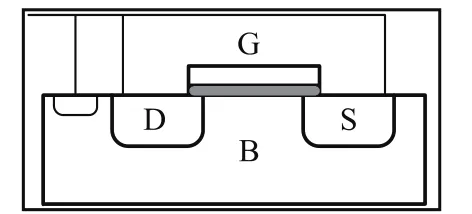

反熔絲單元利用普通MOS管結構,采用MOS管電容連接方式,將漏源和襯底連接在一起,利用高壓將柵氧化層擊穿,以實現熔斷,如圖1所示。此工藝的關鍵是優質柵氧化層的實現,對單元編程后的穩定性起到關鍵作用。

圖1 反熔絲單元

我們利用現有工藝線,在工藝工程批次中制備了五種不同厚度的柵氧化層,分別為4nm、8.35nm、12.5nm、16.5nm和27.5nm。以27.5nm柵氧化層為例,利用7.5V的電壓對兩試驗樣品進行熔斷。測試采用NI PXI-4130可編程電源,具體測試結果如下。

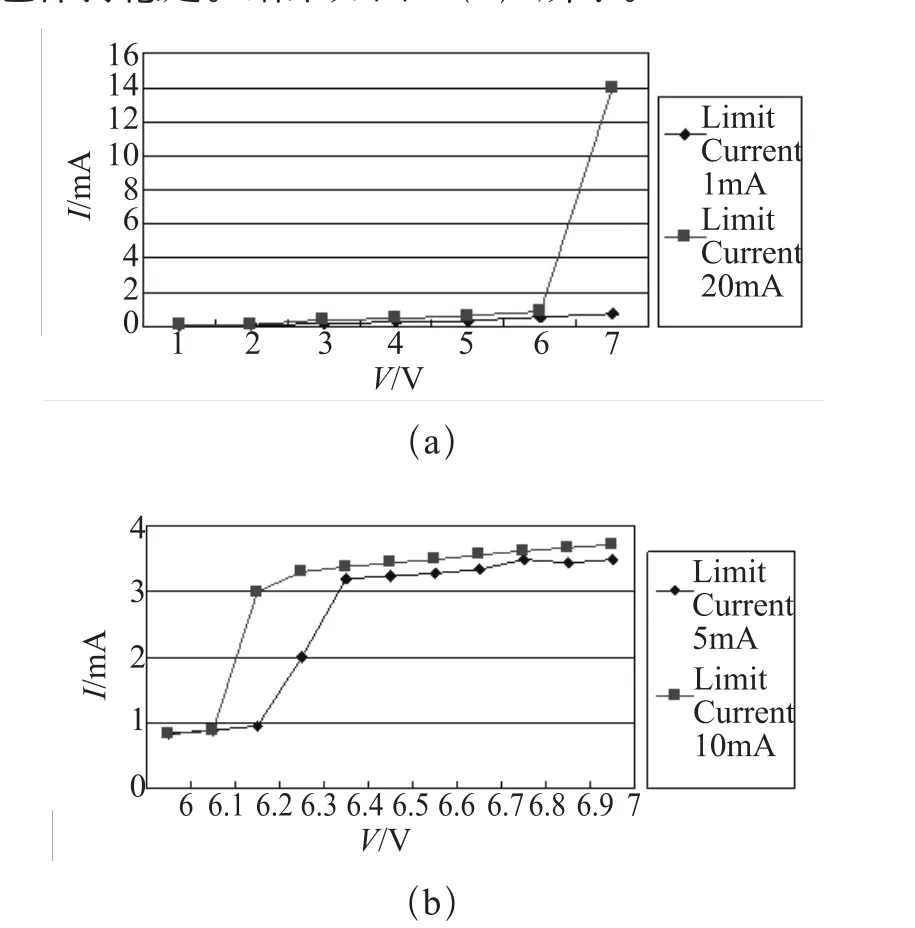

樣品一:選擇0~7V的電壓測試范圍,測試電壓步長為50mV,限流1mA。在測試過程中,單元一直未熔斷。將限流條件放寬至20mA,電壓步長為20mV,發現在6.76V時單元被熔斷,此時電流為1.15mA。此后加大電壓,電阻值保持在350Ω左右,電流為14mA。結果如圖2(a)所示。之后對樣品一的電壓測試范圍調整至6V~7V,限流5mA,測試步長為10mV。熔斷電壓約為6.3V,此時熔斷電流為2mA,熔斷電阻為2kΩ,且保持穩定。將限流調整為10mA,測試步長為5mV。發現在6.2V時發生熔斷,此時熔斷電流達到3mA,熔斷電阻為1.31kΩ,且之后也保持穩定。結果如圖2(b)所示。

圖2 樣片一測試結果

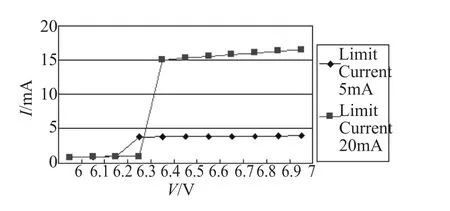

樣品二:初始測試與樣品一相似,在0~7V范圍內,限流1mA情況下,單元一直未熔斷,將限流條件放寬至20mA,電壓步長為20mV,發現在6.6V時單元被熔斷,此時電流為1.23mA。此后加大電壓,電阻值同樣保持在350Ω左右,電流為17mA。測試曲線與圖2(a)相似。調整測試方案,在6V~7V的電壓范圍內,限流5mA,測試步長為20mV,發現單元在6.3V左右熔斷,熔斷后電流為3.8mA,電阻保持在2.3kΩ左右,將限流擴大至20mA,測試步長調整為5mV,發現測試樣品大約在6.4V熔斷,熔斷后電流為15mA,熔斷后電阻保持在335Ω左右。結果如圖3所示。

圖3 樣品二測試結果

單元熔斷后,重新加0~7V電壓,不限流情況下重新測試,得出以下結果:在電壓正負不顛倒的情況下,熔斷電壓在6.2V~6.7V范圍內,限流在1mA時已熔斷,但電阻在6kΩ左右,隨著限流增大,電阻等比例減小。而在不限流時,熔斷電阻基本保持在330Ω~400Ω左右,電流保持14mA~19mA。樣品一可能由于柵氧制備原因引起窗口問題,導致熔斷后單元有不穩定的情況。而樣品二熔斷后能保持穩定。

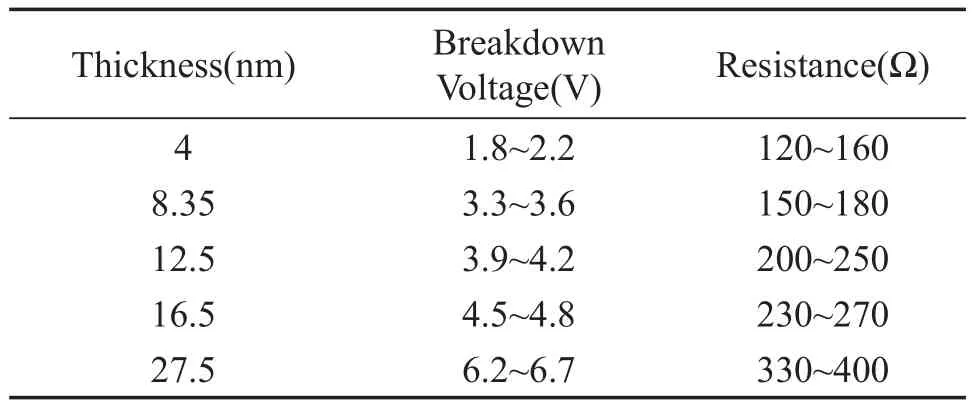

利用柵氧化層擊穿技術形成的反熔絲單元,其擊穿電壓主要與介質層厚度有關,同時也受到制備條件及成分密度的影響。采用相同的測試方法,各種不同厚度的樣品擊穿電壓以及擊穿后電阻的大小如表1所示。

表1 各樣品擊穿電壓及阻值

測試結果說明,與MTM以及ONO反熔絲技術相比,此結構的單元同樣具有很好的穩定性與熔斷特性,且不受特殊工藝的限制,能與CMOS工藝兼容,是一種理想的實現方法。

3 反熔絲陣列設計

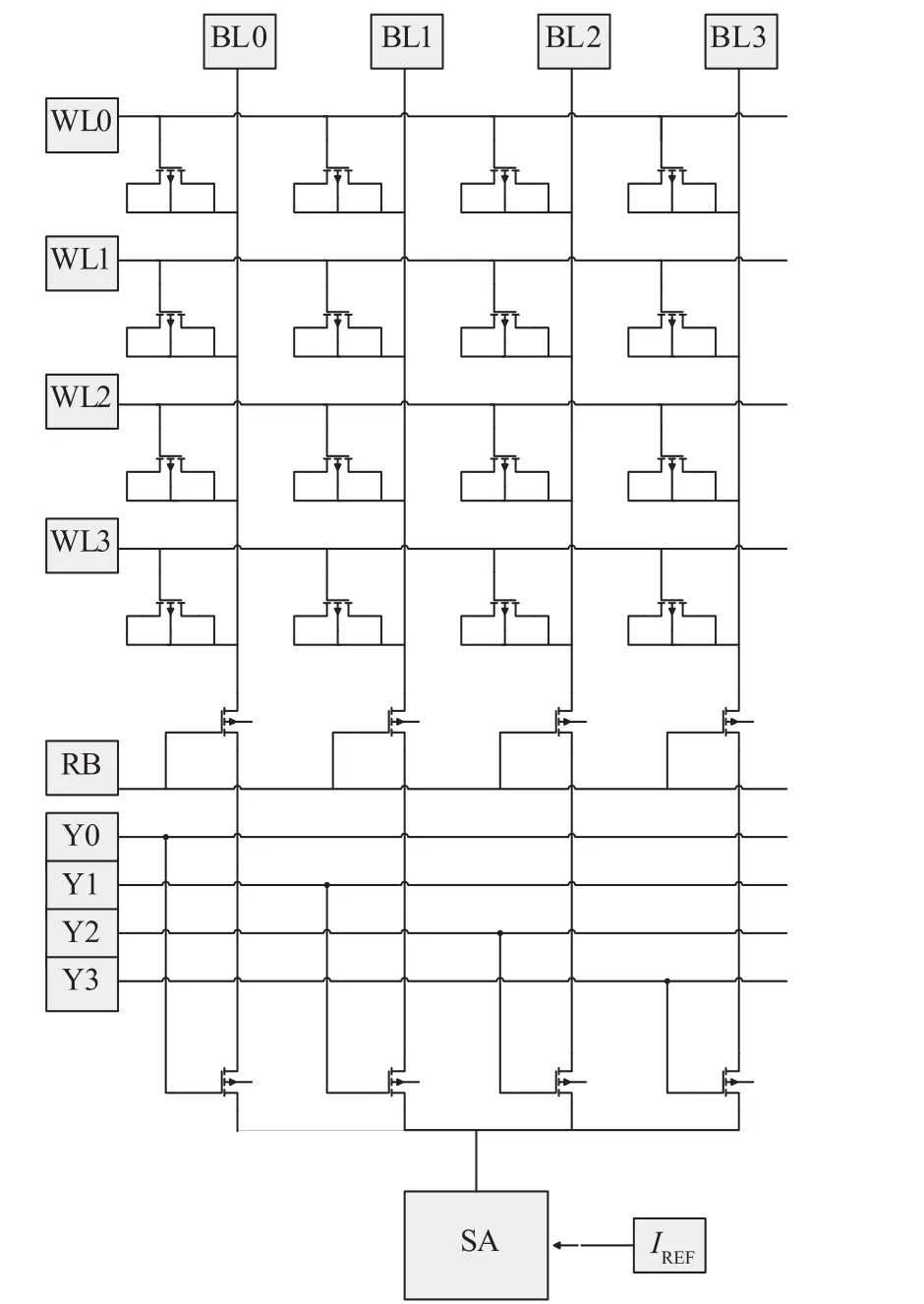

以4×4反熔絲陣列為例,如圖4所示,其中WL為字線,BL為位線,RB是讀允許控制端,Y端為列譯碼線,SA為靈敏放大器,用于將從單元讀出的電流與IREF電流比較,讀出數據“0”和“1”。具體工作方式為:(1)編程階段。RB端為低電壓,讀操作被關閉,字線WL端接相應的熔斷電壓。對需要編程的位,將BL端接GND,不需要編程的位,將BL端接高電壓或浮空。將MOS單元熔斷,實現編程。(2)讀出階段。將RB端接高電平,使讀出允許。將需要讀出字的WL端接VDD,通過譯碼控制Y0~Y4,將對應位以電流的形式讀出。將讀出電流傳輸至小信號放大器(SA),通過與參考電流IREF的比較,讀出數據“0”或“1”。整個電路簡潔,編程和讀出操作也易于實現,且具有高密度、低功耗的優點,方便此結構FPGA的大規模應用。

4 總結

文章在現有MOS工藝的基礎上,通過對不同厚度柵氧化層擊穿電壓的試驗和測試,找到了一種可兼容MOS工藝的反熔絲單元設計。通過試驗證明了熔斷后單元的穩定性,是傳統的、需要特殊工藝支持的反熔絲FPGA 的一種良好的替代。并且具有電路簡潔、編程和讀出操作易于實現、高密度、低功耗的優點,方便了此結構反熔絲FPGA的大規模應用,不但滿足了軍事和航天領域的需求,也為以后反熔絲產品的實現提供了有價值的借鑒。

圖4 反熔絲陣列設計

[1] Ken O'Neill. Antifuse FPGA Technology Best Option for Satellite Application[J]. 電子產品世界,2005,10:92-94.

[2] McCollum J. ASIC versus antifuse FPGA reliability[J].IEEE Aerospace conference, 2009:1-11.

[3] Nejad R J, Rickey P A, Konadu K, et al. Radiation Characterization of a Hardened 0.22μm Anti-Fuse Field Programmable Gate Array[J]. IEEE Transactions on Nuclear Science, 2006, 53(6):3525-3531.

[4] Rezgui S, Wang J J, et al. SET characterization and mitigation in RTAX-S antifuse FPGAs[J]. IEEE Aerospace conference, 2009:11-14.

[5] Daichi Kaku, Toshimasa Namekawa, et al. A Field Programmable 40-nm Pure CMOS Embedded Memory Macro using a PMOS Antifuse[J]. Solid-State Circuits Conference, 2009:217 - 220.

[6] Wlodek Kurjanowicz, Ottawa, Split-channel Antifuse Array Architecture:USA 7,402,855B2[P/OL]. 2008-06-22[2005-05-06].

[7] Yoshida, et al. Method of Manufacturing Semiconductor Integrate Circuits:USA 3,634,929[P/OL]. 1972-01-18[1969-10-29].

[8] Mohsen, et al. Programmable Low Impedance AntifuseElement:USA 4,823,181[P/OL].1989-04-18 [ 1986-05-09].