一種天文圖像的光纖傳輸系統的設計*

李漢青,李彬華,王春榮,金建輝

(昆明理工大學信息工程與自動化學院,昆明 650051)

在天文成像觀測領域,由于所傳輸的圖像數據量大,多采用Camera Link、GIGE、網絡和光纖等方式。每一種方式都有其優點和局限,比如Camera Link帶寬可達7140Mbps,但傳輸距離限制在10m以內,不能應用于遠程傳輸。利用Gig EVision技術可以在1000Mbps的速率下傳輸100m,如果需要更遠的距離則可以使用中繼或光纖媒介[1]。通過10/100M的普通TCP/IP網絡傳輸,其局限性是速率比較低。以一個2k×2k相機實驗為例,在不使用網絡加速手段時,將采集到的一幅圖像上傳至計算機大約需要70s的時間。國家天文臺曾有人通過網絡加速的方法,使傳輸速率得到較大提升,可以達到70~80Mb/s[2]。此方法大大提高了傳輸的時效性,但是,可靠性隨之降低。因此,采用網絡加速的方法在某些時候并不適用。為兼顧傳輸時效性和傳輸距離,可以采用“USB+光纖”的方式,先用USB接口轉光纖接口的設備將數據轉化為光信號以適合在光纖中遠距離傳輸。在計算機端,再用光纖接口轉USB接口的設備恢復為原始的圖像信息,通過USB接口上傳到計算機[3]。

天文圖像傳輸所采用的通信系統大都是針對整個觀測系統的特點而開發的專用系統,通用性稍差。結合一個正在研制的天文用CCD相機系統的要求,并參考UCO/Lick CCD相機的光纖傳輸電路,開發出一種可滿足當前課題要求的天文圖像光纖傳輸系統。本文介紹該系統的結構、硬件和VHDL設計思想和實現的技術。

1 傳輸系統設計總體思想

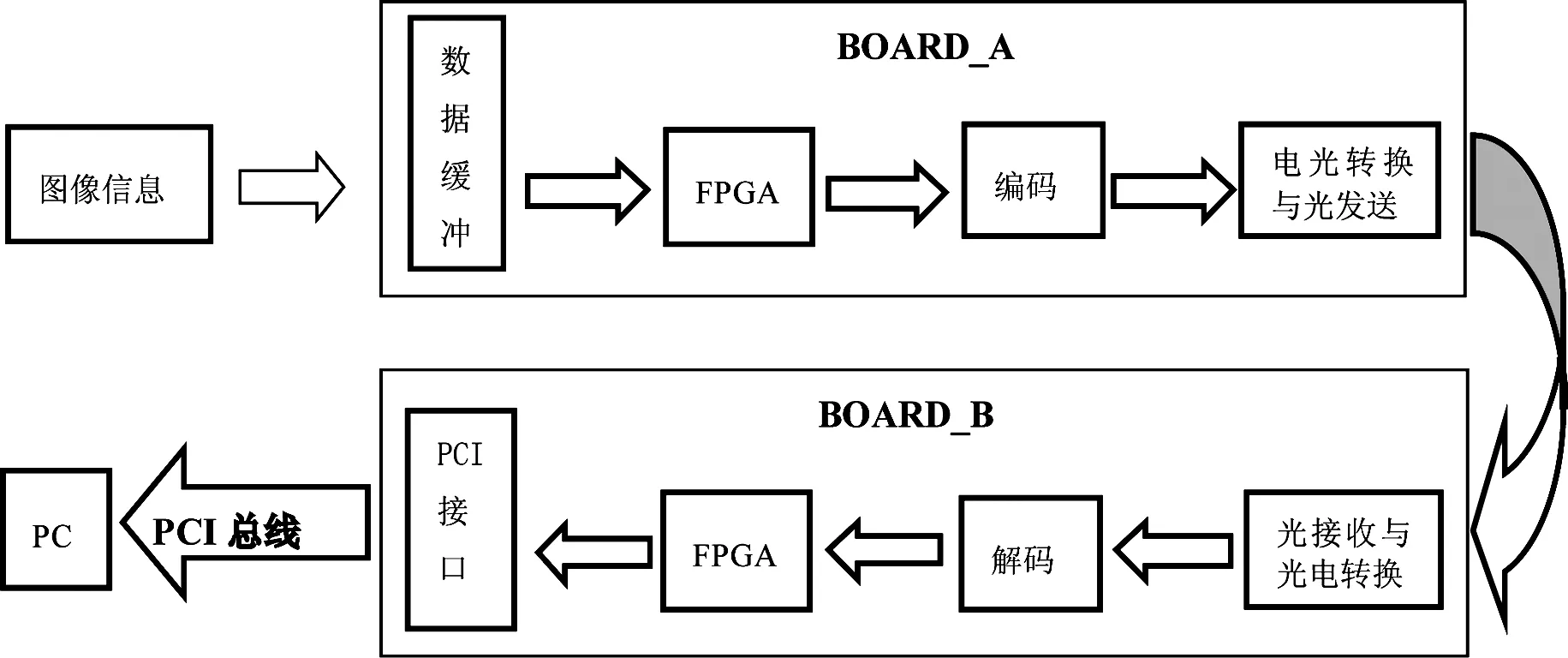

整個系統要實現的功能是將CCD相機采集的圖像數據通過光纖信道快速上傳到計算機。在相機端,要將圖像數據進行編碼和電光轉換,并送入光纖信道;在計算機端,要將接收到的圖像數據光電轉換和解碼,并通過PCI總線發送到計算機。整個系統主要以數據的光傳輸為基礎來構建。因此,在系統設計時,需要首先考慮光纖的選型,其次是PCI總線接口芯片、編碼/解碼器件、電光/光電轉換器件和作為控制用的FPGA等關鍵性元器件的選擇。

光纖分為多模光纖和單模光纖,其通信模式、通信速率、通信距離以及纖芯大小與所使用光波的工作波長均有很大差異。總的來說,單模光纖頻帶寬、傳輸容量大,傳輸距離長,一般不用光放大就能以10Gbit/s及以上速率傳輸幾十千米。多模光纖的帶寬、容量以及傳輸距離不及單模光纖,速率一般在10Gbit/s以下,距離一般在1~2km,但其芯徑粗、數值孔徑大,連接時不必精確對準,操作方便簡單。基于以上分析和課題具體要求,選擇多模光纖。

圖像數據上傳到計算機端后,需要經過PCI總線接口芯片送到計算機存儲器中。在比較PCI9042和CY7C09449這兩片常用的芯片之后發現,CY7C09449支持DMA功能,可以作為PCI主設備發起傳輸,并且其內部有一個16KB共享雙口RAM,能增強設計的靈活性[4]。因此,PCI接口控制器采用CY7C09449。對于編碼/解碼器件、電光/光電轉換器件,參考Lick CCD相機的電路,使用CY7B923/933和HFBR1119T/2119T。FPGA采用ALTERA公司的EP1C6Q240,它有近6000個邏輯單元、185個用戶I/O、92160比特存儲器和兩個PLL,能滿足設計所需的資源。

根據以上分析,本系統需要在相機端和計算機端各設計制作一塊電路板,分別命名為BOARD_A和BOARD_B,均采用4層板設計。BOARD_A主要由數據緩沖器、FPGA、編碼器、電光轉換器以及配置芯片和電源模塊組成。FPGA實現對數據16bit/8bit轉換以及對編碼器的控制。BOARD_B由光電轉換器、解碼芯片、大容量FIFO、FPGA、PCI接口芯片以及配置芯片和電源模塊組成。各模塊和信號流程圖如圖1。

圖1 傳輸系統模塊及其信號流程圖Fig.1 Block diagram of the transmission system

2 傳輸系統的電路設計

2.1 FPGA周邊電路的設計

FPGA的外圍電路主要包括電源電路、配置電路、用戶IO接口以及數據/信號緩沖器。選用的FPGA器件需要1.5V和3.3V兩個電源,其中1.5V的電源為FPGA內部的PLL和邏輯單元供電,3.3V的電源給FPGA的IO供電。分別采用LMS1585ACT-1.5和LM1085-3.3兩種集成穩壓器。FPGA提供足夠的IO引腳,但使用時要考慮布線要求,如布線長度和復雜度等,所以需要根據芯片的布局(即位置)選用合適的IO引腳。

對FPGA進行編程和調試的接口可以使用JTAG接口,也可以采用AS接口。JTAG接口可以用來調試EP1C6,下載速度快,而且支持在線調試,但它不能用來編程配置芯片,如EPCS。AS接口可以用來編程EPCS芯片,同時也可以用來調試。具體過程是首先編程EPCS,然后通過EPCS配置FPGA,運行程序。EPCS芯片有高達十萬次的重復編程能力,能滿足調試需要。因此,為了簡化電路,該設計中只采用AS接口。其與EP1C6的電路連接采用了串行配置器件EPCS1&EPCS4說明書中的方案。

需要注意的是,當使用AS模式時,EP1C6的模式選擇引腳MSEL0和MSEL1要置0。另外,為了方便調試,要在QUARTUSII軟件中選中DEV_CLRN選項,使能此引腳。當這個腳被置低,所有的寄存器都會被清零[5]。在EP1C6的DEV_CLRN管腳上接一個低電平復位電路,以此作為該器件的復位管腳。

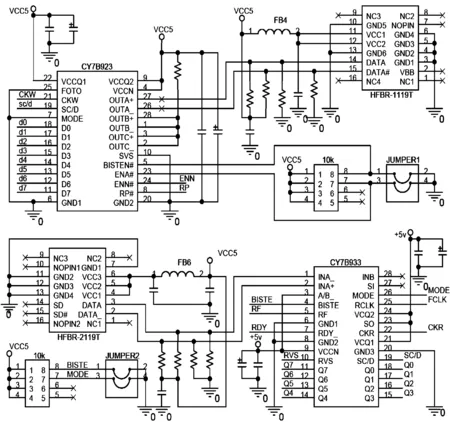

2.2 編碼/解碼電路和光發送/接收電路的設計

編碼/解碼器使用CYPRESS公司的CY7B923/933-SC芯片。該芯片的傳輸速率最高可達330Mbps;具有8B/10B編碼、10-bit解碼能力;兼容光纖、同軸電纜、雙絞線等介質;使用+5V單電源供電,除正常的工作模式外,還有內置的自測模式。在工作之前,可以先進入自測模式,檢測整個光纖鏈路的通信。此外,自測模式還可以用來粗略估算系統的誤碼率。

光發送/接收器使用HP公司的HFBR-1119T/21119T。該芯片用于50μm和62.5μm的多模光纖,工作波長為1300nm,可以以266MBd的速率傳輸1500m[6]。

最后,參考CY7B923/933、HFBR-1119T/21119T的說明書上推薦電路,并結合系統要求,設計的編碼/解碼電路和光接收/發送鏈路的原理圖如圖2。

圖2 光發送/接收電路原理圖Fig.2 Schematic diagram of the transmitter and receiver

3 FPGA的設計

FPGA在系統中的主要作用是對編碼器和解碼器進行控制、產生PCI接口控制器的驅動波形、生成在不同時鐘域之間數據傳輸所需要的FIFO以及對FIFO進行控制。FPGA的設計在Quartus Ⅱ開發環境下使用VHDL語言和電路原理圖相結合的形式完成。

在光發送端:當檢測到鎖存器的鎖存信號CCLK有效,說明數據已到來,使能鎖存器將16bit數據鎖存到兩個8位鎖存器中,然后分兩次寫入FIFO。當檢測到FIFO半滿時,CY7B923使能信號ENA和FIFO讀請求RDREQ有效,數據讀出。FIFO的讀時鐘采用CY7B923輸出的時鐘RP以保證FIFO和編碼器同步。由于RP在編碼器的ENA有效后才輸出,即半滿之前FIFO讀時鐘無效,用來指示空狀態的RDUSED信號一直為0,也就是一直為空,就一直不能觸發讀出。因此,FIFO的讀時鐘要一直有效。鑒于此,在CY7B923使能信號ENA和FIFO讀請求RDREQ有效前,采用FPGA內部時鐘作為讀時鐘,ENA和RDREQ有效后讀時鐘采用編碼器輸出時鐘RP。

此外,為便于調試,在發送端的FPGA中還實現一個產生模擬圖像數據的模塊。該模塊產生一個2080×2048個像素,每一行的第N個像素都用16bit的N的二進制表示。

在光接收端:當FPGA接收到CY7B933的準備好標志信號RDY有效,表明數據已準備好,此時使FIFO芯片SN74V293寫請求有效。讀時鐘采用解碼器的輸出時鐘。當FIFO到達約定值時,產生PCI接口芯CY7C09449的驅動波形,向其內部的雙口RAM發送數據,當RAM中數據達到8KB時,觸發DMA傳輸。通過PCI總線將數據傳送到PC。

4 系統仿真和實測結果的分析

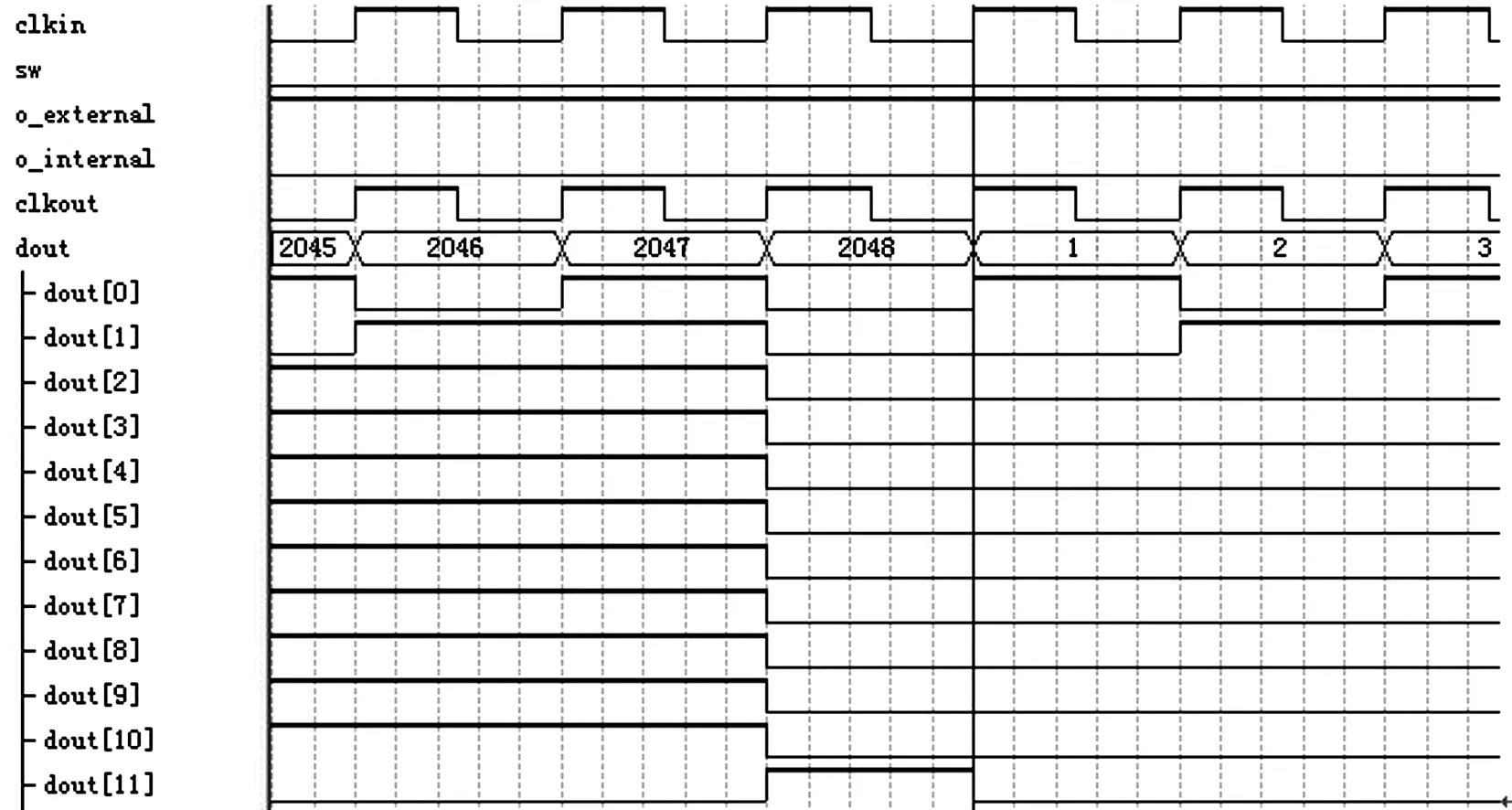

4.1 數據生成模塊的仿真與測試

模擬數據生成模塊產生的是一幅2080×2048個像素的圖像,共2080行、2048列,每行的像素值從1到2048依次遞增,即每行的輸出從0000000000000001到0000100000000000遞增。圖3是數據生成模塊仿真波形的一部分結果。數據輸出端口dout為2048時,對應的是某一行的最后一個像素,下一時刻dout輸出值為1,則表示是下一行的第一個數據。從圖中可以看出,輸出數據是依次遞增的,這說明設計模塊內部邏輯是正確的。

圖3 數據生成模塊仿真波形Fig.3 Simulated waveform of the data-generating module

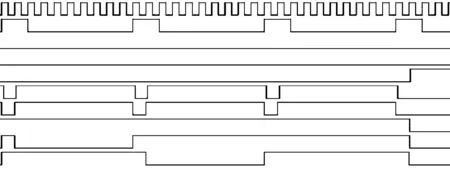

圖4是在FPGA的IO引腳上實測模擬數據輸出的波形。圖中從上至下的波形依次為,時鐘信號CLK、FIFO讀請求信號RDREQ、八位數據信號d7~d0。讀請求高有效,在CLK的下降沿讀出。從波形中看出,在相鄰4個讀請求有效時,讀出的數據依次為:00000111,00011101;00000111,00011110;00000111,00011111;00000111,00100000。即相鄰的4個像素值為0000011100011101;0000011100011110;0000011100011111;0000011100100000,依次遞增。實測結果顯示,輸入到CY7B923的數據是連續的,與仿真的結果相同,表明Board_A板上的模擬數據發送模塊產生的數據正確。

圖4 寫入CY7B923的數據波形Fig.4 Waveform of the data written into the CY7B923

4.2實測結果

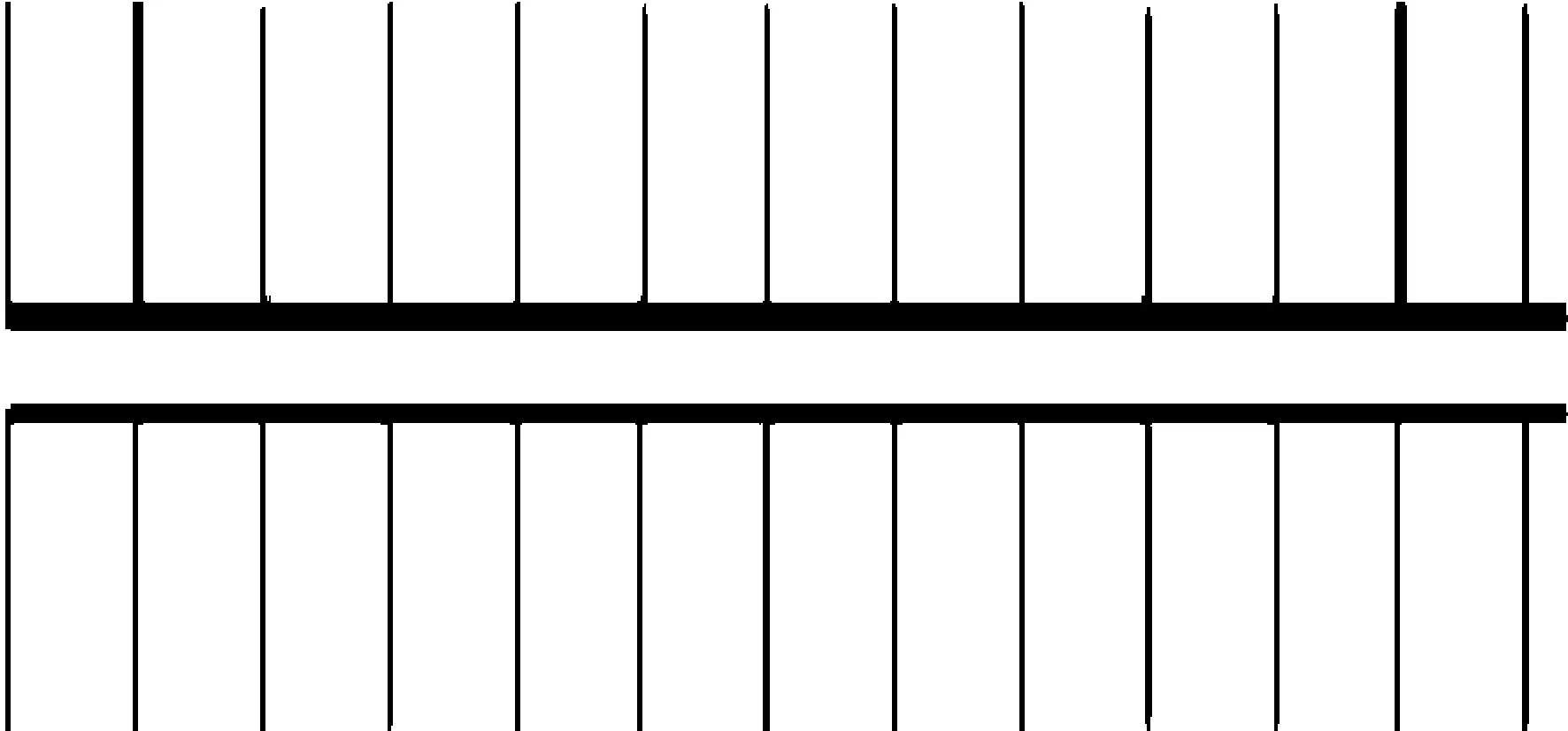

用示波器在BOARD_A的FPGA輸出端和BOARD_B的PCI接口芯片之前,測試某一時刻的波形,如圖5。

圖5 BOARD_A發送和BOARD_B接收的數據Fig.5 Data transmitted by the BOARD_A and received in the BOARD_B

圖5中,上面8位是接收端的波形,下面8位是發送端的波形。從圖中波形可以看出,數據在經過編碼、并串轉換、電光轉換、光纖傳輸、光電轉換、串并轉換、解碼等一系列動作之后,接收端實測的數據與發送端的一致,表明整個傳輸系統工作正常。通過示波器還可以看出,在接收端產生了一個確定的傳輸延遲,延遲量約500ns。這個延遲主要由編碼/解碼、電光/光電轉換產生。此外,中間的74AC541緩沖器也會產生約10ns的延遲。

4.3 自測模式下的誤碼率估算

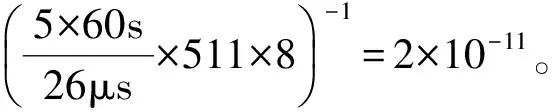

誤碼率估算借鑒文獻[7]中的方法。對于本系統來講,具體實現的方法是將CY7B923的BISTEN、ENN和CY7B933的BISTEN引腳置為低電平,選擇自測模式。在該模式下,CY7B923產生循環發送的偽隨機序列,每循環為一組,共511個字節。在一個循環中,讀脈沖RP產生一個周期的低電平,RDY產生一個高電平。CY7B933的讀時鐘引腳CKR輸出的20MHz時鐘作為FIFO的寫時鐘。接好光纖上電后,用示波器檢測相關引腳,波形如圖6、圖7。

圖6 RDY、RP和CKR信號波形Fig.6 Waveforms of the RDY, RP,and CKR

圖7 RDY和RP信號波形(脈沖)Fig.7 Waveforms of the RDY and RP

5 結束語

本文結合一個天文用CCD相機項目,設計出一種用于圖像數據傳輸、抗干擾能力強、帶寬高的光纖傳輸系統。介紹了系統硬件電路和FPGA的設計方案和實現技術,對FPGA數字部分進行了仿真并給出部分模塊的仿真波形,對系統的重要模塊及整個通信鏈路進行實測,同時估算了誤碼率。分析表明,所測結果正確,估算誤碼率也較低。目前,硬件工作基本完成,正在進行PCI驅動程序的設計工作。

致謝:感謝國家天文臺葉彬潯研究員、宋謙研究員,他們在本項目研究之初提出過一些建設性的意見和建議。

[1] 北京凌云光子技術公司.http://vision.lusterinc.com/episteme/framegrabber.html.2009-11.

[2] 段之昱.天文CCD相機控制系統的軟件研究[D].中國科學院研究生院碩士學位論文,2006-11.

Duan Zhiyu.A study of Control and Acquisition Software of an Astronomical CCD Camera[D].Master dissertation of Gradnate University of the Chinese Academy of Sciences,2006-11.

[3] Wei Mingzhi,Stover Richard J.A USB 2.0 computer interface for the UCO/Lick CCD cameras[J].SPIE,2004,5499:476-480.

[4] CYPRESS Company.128Kb Dual-Port SRAM with PCI Bus Controller(PCI-DP).2002.

[5] Altera Corp.Cyclone Device Handbook.2008.

[6] Agilent Technologies.Inc Fiber Optic Transmitter and Receive Data Links for 266 MBd Technical Data. 1999.

[7] 鄭劍鋒.水下遠程數據有線傳輸技術研究[D].中國科學院研究生院博士學位論文,2004.

Zheng Jianfeng.Researches on Underwater Long-Distance Cable Data Transmission Techuology[D].Ph D Dissertation of Graduate University of the Chinese Academy of Sciences,2004.