基于EDA的數(shù)字電子技術(shù)基礎(chǔ)教改實(shí)踐

摘 "要 "把項(xiàng)目驅(qū)動(dòng)式教學(xué)法引入數(shù)字電子技術(shù)基礎(chǔ)課程,增加電子設(shè)計(jì)自動(dòng)化(EDA)設(shè)計(jì)方法,將傳統(tǒng)數(shù)字電路的內(nèi)容與EDA設(shè)計(jì)相關(guān)內(nèi)容融合,課堂理論教學(xué)與實(shí)踐教學(xué)融入同一教學(xué)過程,在夯實(shí)學(xué)生知識(shí)基礎(chǔ)的同時(shí),適應(yīng)學(xué)生的就業(yè)需求,落實(shí)現(xiàn)代高校以學(xué)生為本的教學(xué)理念,取得良好的教學(xué)效果。

關(guān)鍵詞 "數(shù)字電子技術(shù)基礎(chǔ);EDA;項(xiàng)目驅(qū)動(dòng)式教學(xué);混合式教學(xué);翻轉(zhuǎn)課堂;創(chuàng)新實(shí)驗(yàn)

中圖分類號:G642.0 " 文獻(xiàn)標(biāo)識(shí)碼:B

文章編號:1671-489X(2022)11-0039-04

0 "引言

數(shù)字電子技術(shù)基礎(chǔ)課程是自動(dòng)化、計(jì)算機(jī)、電氣電子、通信、機(jī)械等專業(yè)重要的專業(yè)基礎(chǔ)課程。該課程以邏輯代數(shù)為基礎(chǔ),邏輯性強(qiáng),內(nèi)容豐富且較抽象,理論與實(shí)踐緊密結(jié)合,實(shí)踐性非常強(qiáng),工程應(yīng)用廣,與現(xiàn)代電子技術(shù)發(fā)展緊密相連[1]。EDA(electronic design automatic,電子設(shè)計(jì)自動(dòng)化)是以大規(guī)模可編程邏輯器件為設(shè)計(jì)載體,以硬件描述語言為系統(tǒng)邏輯描述的主要表達(dá)方式,以計(jì)算機(jī)、大規(guī)模可編程器件的開發(fā)軟件及實(shí)驗(yàn)開發(fā)系統(tǒng)為設(shè)計(jì)工具,從而實(shí)現(xiàn)硬件設(shè)計(jì)軟件化的新技術(shù)。很多學(xué)校把EDA的設(shè)計(jì)思路引入數(shù)字電路的教學(xué)中[2-7]。

基于EDA技術(shù),引入項(xiàng)目驅(qū)動(dòng)方式,采用線上線下相結(jié)合的混合式教學(xué)模式,在北京航空航天大學(xué)自動(dòng)化科學(xué)與電氣工程學(xué)院設(shè)置校級本科一流課程。項(xiàng)目式教學(xué)法以項(xiàng)目作為切入點(diǎn),將課堂理論教學(xué)與實(shí)踐教學(xué)融入同一教學(xué)過程中。教師把知識(shí)點(diǎn)融于項(xiàng)目中,再把項(xiàng)目分配給學(xué)生,學(xué)生在教師指導(dǎo)下完成項(xiàng)目。通過項(xiàng)目教學(xué)法,學(xué)生主動(dòng)學(xué)習(xí)元器件的工作原理及其使用方法,在實(shí)踐中加深對元器件的認(rèn)知。與傳統(tǒng)教學(xué)方法相比,學(xué)生學(xué)習(xí)的過程不再僅僅是枯燥乏味的聽課過程,而是學(xué)做一體的實(shí)踐過程,有助于學(xué)生理解和掌握抽象的知識(shí)與技能,還有助于培養(yǎng)分析、解決問題的能力,更有助于培養(yǎng)協(xié)作能力和團(tuán)隊(duì)精神。

1 "教改思路

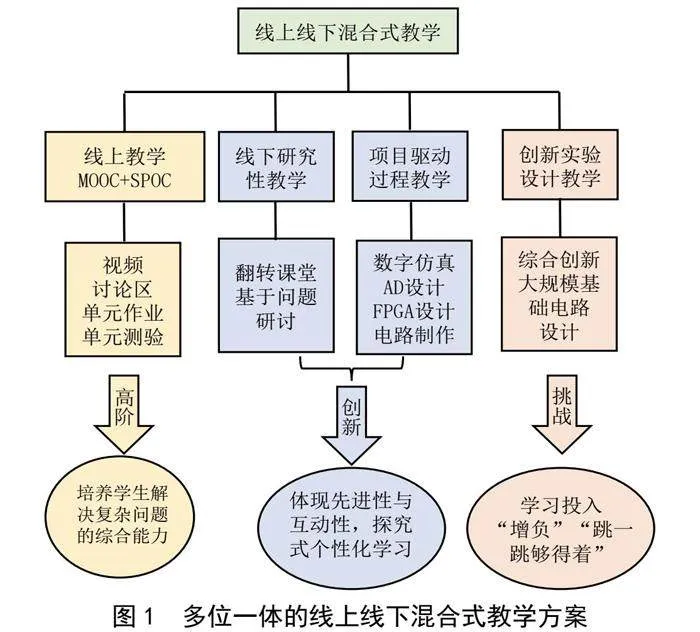

以學(xué)生為中心,從“高階性、創(chuàng)新性、挑戰(zhàn)度”的標(biāo)準(zhǔn)審視課程建設(shè)的一系列教學(xué)活動(dòng),引入項(xiàng)目驅(qū)動(dòng)式教學(xué)模式,在北京航空航天大學(xué)自動(dòng)化學(xué)院的數(shù)字電子技術(shù)基礎(chǔ)課程中采取圖1所示多位一體的線上線下混合式教學(xué)方案進(jìn)行授課。

1.1 "創(chuàng)新實(shí)驗(yàn)內(nèi)容設(shè)計(jì)

項(xiàng)目驅(qū)動(dòng)過程教學(xué)環(huán)節(jié)以及創(chuàng)新實(shí)驗(yàn)環(huán)節(jié)是學(xué)做一體實(shí)踐過程的關(guān)鍵。從系統(tǒng)性思維和能力培養(yǎng)出發(fā),設(shè)計(jì)項(xiàng)目驅(qū)動(dòng)過程教學(xué)的創(chuàng)新實(shí)驗(yàn)內(nèi)容,實(shí)驗(yàn)分為兩類。

1)基于中小規(guī)模集成電路的實(shí)驗(yàn)項(xiàng)目。電子鐘、電子秤、計(jì)費(fèi)器、模型計(jì)算機(jī)、乒乓球游戲機(jī)等電路的設(shè)計(jì),要求學(xué)生采用中小規(guī)模的集成電路完成電路的設(shè)計(jì)及仿真。

2)基于FPGA的大規(guī)模集成電路的實(shí)驗(yàn)項(xiàng)目。要求學(xué)生采用Verilog硬件描述語言,基于FPGA完成四類模塊的設(shè)計(jì),即門電路模塊設(shè)計(jì)、常見組合邏輯模塊設(shè)計(jì)(譯碼器、編碼器等)、常見時(shí)序電路模塊設(shè)計(jì)(觸發(fā)器、寄存器、計(jì)數(shù)器等)、綜合電路模塊設(shè)計(jì)(串口收發(fā)模塊)。除需要完成設(shè)計(jì)與仿真外,還要求學(xué)生在FPGA開發(fā)板上完成實(shí)驗(yàn)驗(yàn)證。

1.2 "學(xué)時(shí)安排及匹配

數(shù)字電子技術(shù)基礎(chǔ)課程一共48學(xué)時(shí),受學(xué)時(shí)限制,沒法將創(chuàng)新實(shí)驗(yàn)環(huán)節(jié)安排在翻轉(zhuǎn)課堂上進(jìn)行。將課程中創(chuàng)新實(shí)驗(yàn)相關(guān)內(nèi)容與自動(dòng)化科學(xué)與電氣工程學(xué)院的電子技術(shù)綜合實(shí)驗(yàn)(1)、電子技術(shù)綜合實(shí)驗(yàn)(2)兩門綜合實(shí)驗(yàn)課程(共32學(xué)時(shí))相結(jié)合,打通兩門課的實(shí)驗(yàn)內(nèi)容,在數(shù)字電子技術(shù)基礎(chǔ)課程中布置創(chuàng)新實(shí)驗(yàn)內(nèi)容,在翻轉(zhuǎn)課堂上進(jìn)行任務(wù)分配,學(xué)生利用課余時(shí)間以及32學(xué)時(shí)的綜合實(shí)驗(yàn)課程完成創(chuàng)新實(shí)驗(yàn)的任務(wù)。

1.3 "創(chuàng)新實(shí)驗(yàn)實(shí)施方案

在課程教學(xué)中后期,教師公布創(chuàng)新實(shí)驗(yàn)設(shè)計(jì)項(xiàng)目,學(xué)生自由組合成立項(xiàng)目小組,每個(gè)小組人數(shù)不超過四人。每個(gè)小組從基于中小規(guī)模的設(shè)計(jì)項(xiàng)目中選擇一個(gè)作為團(tuán)隊(duì)項(xiàng)目,從基于FPGA的大規(guī)模集成電路的四個(gè)模塊中各選擇一個(gè)作為設(shè)計(jì)任務(wù)。學(xué)生根據(jù)課程設(shè)計(jì)項(xiàng)目要求,通過查閱資料、討論等多種方式確定項(xiàng)目方案,利用課余時(shí)間在MOOC平臺(tái)上自學(xué)課程團(tuán)隊(duì)所錄制的Proteus軟件使用方法以及Verilog HDL基礎(chǔ)知識(shí)的教學(xué)視頻,掌握創(chuàng)新實(shí)驗(yàn)中所要用到的設(shè)計(jì)及仿真軟件的使用方法,運(yùn)用所學(xué)課程知識(shí)完成電路的設(shè)計(jì)、仿真及驗(yàn)證。

2 "基于EDA的教學(xué)模式實(shí)施方案

以時(shí)序邏輯電路的工程時(shí)序邏輯電路設(shè)計(jì)為例,闡述基于EDA的項(xiàng)目驅(qū)動(dòng)式教學(xué)方案實(shí)施過程。該部分的內(nèi)容處于“時(shí)序邏輯電路”這一章的中間部分,是承上啟下的重要環(huán)節(jié),涉及時(shí)序邏輯電路分析與設(shè)計(jì),在此基礎(chǔ)上采用邏輯問題解決方法教學(xué),為后續(xù)章節(jié)的教學(xué)奠定基礎(chǔ)。

2.1 "教學(xué)目標(biāo)

在知識(shí)層面,理解邏輯控制設(shè)計(jì)問題的邏輯抽象內(nèi)涵,掌握邏輯抽象的要領(lǐng)、方法和步驟,正確描述邏輯狀態(tài)和輸入輸出設(shè)定;在能力層面,掌握狀態(tài)分配要領(lǐng),正確描述狀態(tài)轉(zhuǎn)換,掌握求取狀態(tài)方程和輸出方程方法,掌握電路自啟動(dòng)設(shè)計(jì)方法;在應(yīng)用層面,理解仿真技術(shù)的意義目的,初步掌握Proteus邏輯電路仿真方法、Verilog HDL的硬件描述語言編程,并通過創(chuàng)新綜合實(shí)驗(yàn)實(shí)現(xiàn)電路設(shè)計(jì)方案。

2.2 "教學(xué)方法與策略

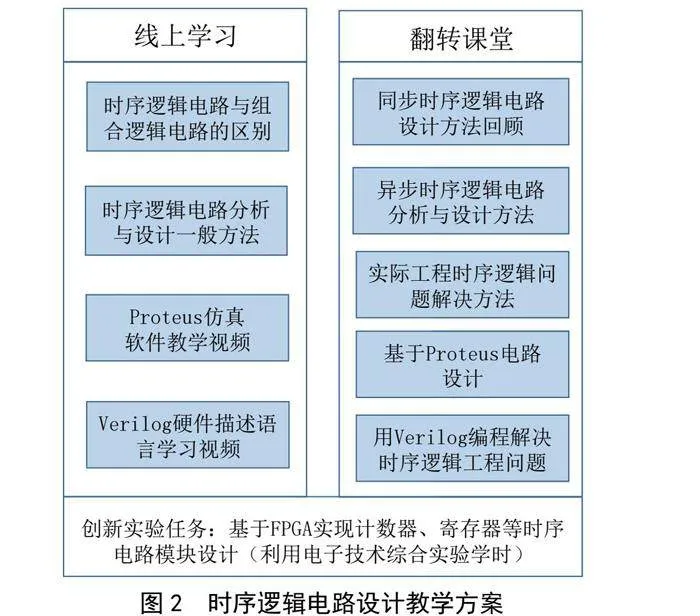

為了更好地體現(xiàn)學(xué)生主體和教師主導(dǎo)地位,基于線上線下混合式教學(xué)模式,從線上和翻轉(zhuǎn)課堂兩條主線進(jìn)行教學(xué)方法設(shè)計(jì),方案如圖2所示。首先,在翻轉(zhuǎn)課堂之前,將教學(xué)內(nèi)容中相對容易掌握的內(nèi)容安排為線上學(xué)習(xí)任務(wù);其次,翻轉(zhuǎn)課堂上,以專業(yè)背景的工程設(shè)計(jì)實(shí)例為引導(dǎo),激發(fā)學(xué)生的學(xué)習(xí)興趣,教學(xué)過程采用啟發(fā)式教學(xué)方法。教師采用多媒體和板書相結(jié)合的授課方式,在課堂上直觀地展示電路仿真電路驗(yàn)證過程,分析仿真結(jié)果,強(qiáng)化仿真實(shí)驗(yàn)手段的必要性和思想方法,演示基于Verilog的典型時(shí)序電路設(shè)計(jì)過程及代碼,線下項(xiàng)目研究與線上、線下課堂和創(chuàng)新綜合實(shí)驗(yàn)緊密結(jié)合,多位一體組合安排,綜合達(dá)成課程目標(biāo)。

2.3 "教學(xué)流程設(shè)計(jì)

針對時(shí)序電路第二節(jié)的教學(xué)內(nèi)容,基于EDA的項(xiàng)目驅(qū)動(dòng)式教學(xué)流程具體設(shè)計(jì)如下。

1)布置線上學(xué)習(xí)內(nèi)容:時(shí)序邏輯電路與組合邏輯電路的區(qū)別、時(shí)序邏輯電路的分析方法、Proteus仿真軟件及Verilog教學(xué)視頻。教師線上學(xué)習(xí)指導(dǎo),并在線上討論區(qū)與學(xué)生交流,讓學(xué)生準(zhǔn)確理解線上學(xué)習(xí)的要求。

2)線上視頻學(xué)習(xí)。學(xué)生自主選擇線上學(xué)習(xí)的時(shí)間,完成所布置的線上學(xué)習(xí)任務(wù)。教師線上與學(xué)生互動(dòng)討論,通過微信群等方式收集學(xué)生的疑惑和問題。學(xué)生通過這個(gè)環(huán)節(jié)掌握時(shí)序邏輯電路的分析和設(shè)計(jì)基本方法。

3)作業(yè)和互評。教師布置對應(yīng)作業(yè)題,組織學(xué)生互評,有助于學(xué)生理解知識(shí)點(diǎn),掌握時(shí)序電路分析和設(shè)計(jì)的基本方法。

4)翻轉(zhuǎn)課堂內(nèi)容設(shè)計(jì)。教師根據(jù)教學(xué)目標(biāo)設(shè)計(jì)翻轉(zhuǎn)課堂內(nèi)容,引入研究性教學(xué),所設(shè)計(jì)的線下翻轉(zhuǎn)內(nèi)容可以啟發(fā)學(xué)生思考,激發(fā)學(xué)生學(xué)習(xí)興趣。同時(shí),針對每屆學(xué)生學(xué)習(xí)能力可能存在的差異,對翻轉(zhuǎn)課堂的內(nèi)容進(jìn)行相應(yīng)調(diào)整。教師主要依據(jù)線上學(xué)習(xí)過程中作業(yè)及互評時(shí)出現(xiàn)的問題,以及利用微信群等方式收集的學(xué)生的疑問,對所設(shè)計(jì)的翻轉(zhuǎn)課堂內(nèi)容進(jìn)行修正。

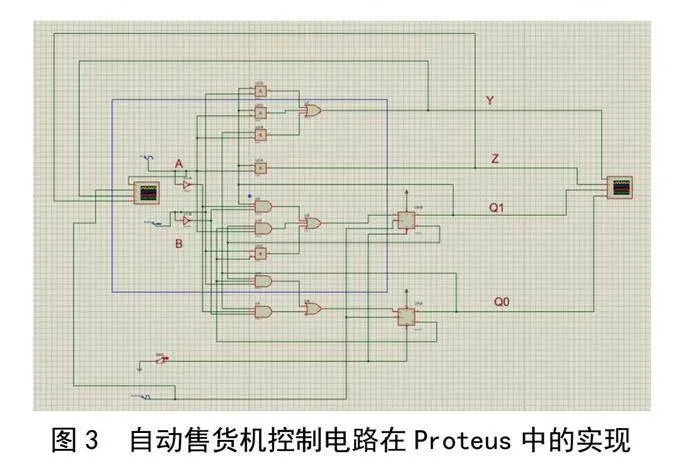

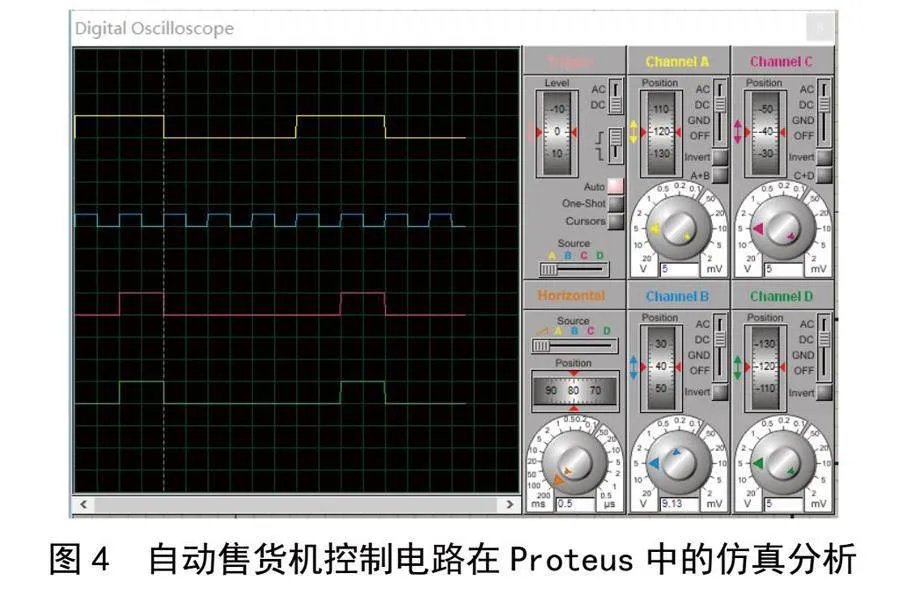

5)翻轉(zhuǎn)課堂授課。教師根據(jù)設(shè)計(jì)的翻轉(zhuǎn)課堂內(nèi)容進(jìn)行線下教學(xué)(2學(xué)時(shí))。首先,對布置的線上內(nèi)容進(jìn)行簡單復(fù)習(xí)和總結(jié),加深學(xué)生對線上知識(shí)的理解。其次,基于工程中常見的時(shí)序控制電路引出翻轉(zhuǎn)課堂的主要內(nèi)容——實(shí)際復(fù)雜工程時(shí)序電路設(shè)計(jì)的解決方法。以工程項(xiàng)目中常見的奇偶校驗(yàn)電路、數(shù)據(jù)檢測器電路、自動(dòng)售貨機(jī)控制電路等的設(shè)計(jì)需求為例,在線上課程內(nèi)容基礎(chǔ)上,對狀態(tài)化簡方法、電路的自啟動(dòng)設(shè)計(jì)方法等內(nèi)容進(jìn)行進(jìn)一步擴(kuò)展,培養(yǎng)學(xué)生分析、解決問題的能力。最后,將自動(dòng)售貨機(jī)的設(shè)計(jì)電路在Proteus中的仿真過程在課堂上展示出來,對設(shè)計(jì)進(jìn)行驗(yàn)證分析。圖3為采用Proteus軟件實(shí)現(xiàn)的自動(dòng)售貨機(jī)的控制電路,圖4為在Proteus仿真中添加虛擬示波器所觀察到的輸入輸出波形,通過輸出仿真分析,學(xué)生能夠更加生動(dòng)直觀地學(xué)習(xí)。

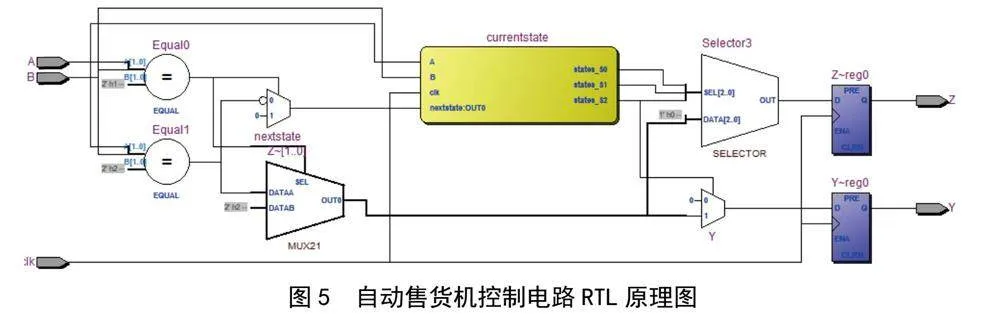

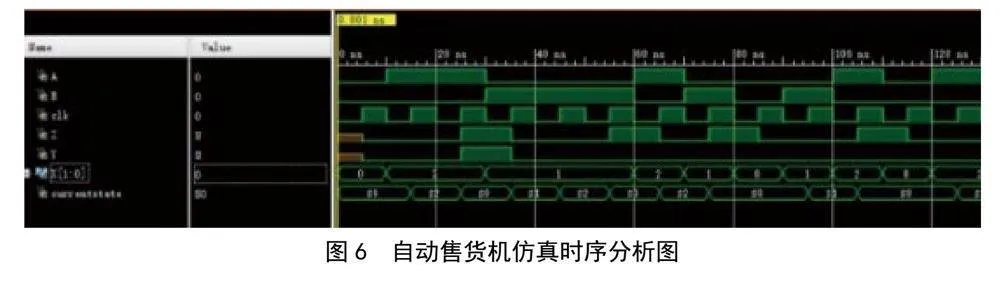

為了讓學(xué)生體驗(yàn)到“跳一跳才能夠得著”的學(xué)習(xí)挑戰(zhàn)目的,在翻轉(zhuǎn)課堂中增加具有一定挑戰(zhàn)度的內(nèi)容。課堂中加入基于硬件描述語言Verilog HDL的自動(dòng)售貨機(jī)控制電路設(shè)計(jì),給出實(shí)現(xiàn)該電路功能的Verilog HDL程序代碼,將時(shí)序電路中的狀態(tài)轉(zhuǎn)換圖與基于Verilog HDL的有限狀態(tài)機(jī)描述方法相結(jié)合,對程序代碼進(jìn)行解釋,學(xué)生能夠更加容易理解基于Verilog HDL的設(shè)計(jì)思想。同時(shí),基于Quartus II軟件,完成設(shè)計(jì)及仿真,并在FPGA開發(fā)板上進(jìn)行驗(yàn)證。通過這種方法,學(xué)生可以初步了解可編程邏輯器件設(shè)計(jì)方法,掌握基于Verilog"HDL的數(shù)字電路設(shè)計(jì)的基本流程。圖5為運(yùn)用Quar-tus II綜合設(shè)計(jì)的自動(dòng)售貨機(jī)控制電路RTL原理圖,圖6為自動(dòng)售貨機(jī)控制電路時(shí)序仿真圖。通過這種方式,能夠呈現(xiàn)真實(shí)電路工作狀態(tài),也可以在軟件上調(diào)整參數(shù),與學(xué)生互動(dòng),加深學(xué)生的理解,充分發(fā)揮演示功能在教學(xué)中的作用,提高學(xué)生對復(fù)雜數(shù)字電路的邏輯設(shè)計(jì)能力。

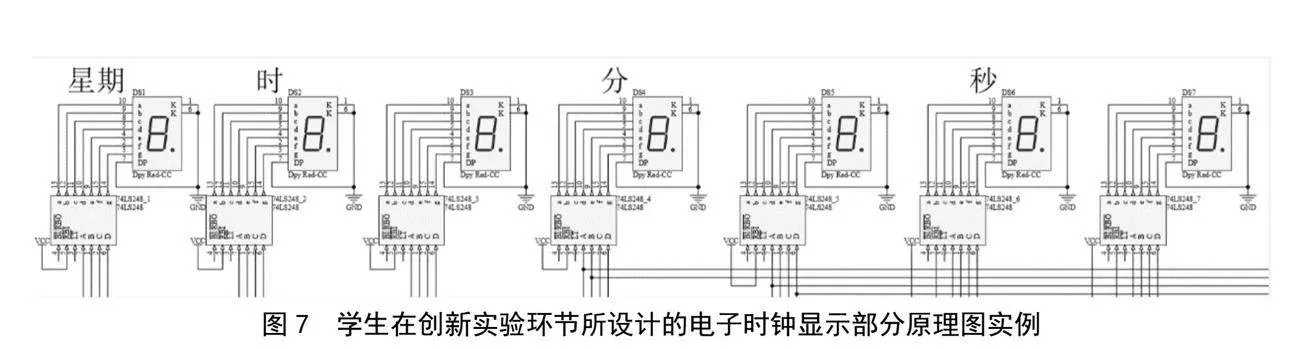

6)創(chuàng)新實(shí)驗(yàn)。在課程教學(xué)中后期,教師公布創(chuàng)新實(shí)驗(yàn)設(shè)計(jì)項(xiàng)目,學(xué)生自由組合成立項(xiàng)目小組,每個(gè)小組人數(shù)不超過四人。每個(gè)小組從基于中小規(guī)模的設(shè)計(jì)項(xiàng)目中選擇一個(gè)作為團(tuán)隊(duì)項(xiàng)目,同時(shí)需要從基于FPGA的大規(guī)模集成電路的四個(gè)模塊中各選擇一個(gè)作為設(shè)計(jì)任務(wù)。學(xué)生根據(jù)課程設(shè)計(jì)項(xiàng)目要求,通過查閱資料、討論等多種方式確定項(xiàng)目方案,運(yùn)用所學(xué)課程知識(shí)完成電路的設(shè)計(jì)、仿真及驗(yàn)證。設(shè)計(jì)過程中,學(xué)生可以通過翻轉(zhuǎn)課堂或者其他線上線下的交流方式獲得教師團(tuán)隊(duì)的指導(dǎo),在電子技術(shù)綜合實(shí)驗(yàn)(1)和(2)的線下實(shí)驗(yàn)課中完成綜合實(shí)驗(yàn)。最后,實(shí)驗(yàn)課教師通過檢查設(shè)計(jì)原理圖、程序源代碼、仿真結(jié)果以及現(xiàn)場答辯等方式,給出創(chuàng)新實(shí)驗(yàn)環(huán)節(jié)的成績。圖7為學(xué)生在創(chuàng)新實(shí)驗(yàn)環(huán)節(jié)所設(shè)計(jì)的電子時(shí)鐘顯示部分原理圖實(shí)例。

2.4 "考核方案

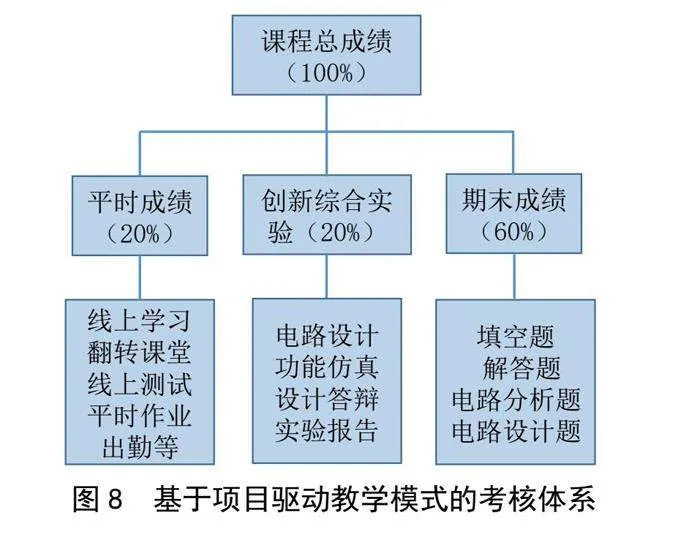

課程考核是檢驗(yàn)教學(xué)效果、提高教學(xué)質(zhì)量的關(guān)鍵環(huán)節(jié)。傳統(tǒng)的以卷面分?jǐn)?shù)為標(biāo)準(zhǔn)的考核方式存在重分?jǐn)?shù)輕能力、重講授輕實(shí)踐的問題。建立圖8所示多元化、過程化、能力化課程考核體系,該考核體系更加重視過程考核,考核評價(jià)貫穿教學(xué)過程,在課前、課中、課后各個(gè)環(huán)節(jié)給予適時(shí)、恰當(dāng)?shù)脑u價(jià)。創(chuàng)新綜合實(shí)驗(yàn)從電路設(shè)計(jì)、功能仿真結(jié)果、設(shè)計(jì)答辯過程等多方面進(jìn)行考核,充分考慮過程性考核。綜合性考核方式實(shí)現(xiàn)對學(xué)生從基礎(chǔ)知識(shí)、概念、實(shí)踐能力和創(chuàng)新能力等多個(gè)角度的綜合考查,教學(xué)實(shí)踐效果表明其更為合理有效。

3 "教改效果

在北京航空航天大學(xué)自動(dòng)化科學(xué)與電氣工程學(xué)院近兩年的教學(xué)中,基于EDA技術(shù),引入項(xiàng)目式驅(qū)動(dòng)線上線下混合式教學(xué)方式,獲得良好的教學(xué)效果,絕大部分學(xué)生不僅在期末考試中獲得良好的筆試成績,而且順利完成創(chuàng)新實(shí)驗(yàn)。借助這一教學(xué)模式,學(xué)生不僅掌握了教學(xué)大綱所規(guī)定的內(nèi)容,還具備了一定的解決復(fù)雜工程問題的能力。創(chuàng)新實(shí)驗(yàn)環(huán)節(jié)的鍛煉,讓學(xué)生能夠基于EDA技術(shù),掌握數(shù)字系統(tǒng)的設(shè)計(jì)、仿真和調(diào)試流程。這種學(xué)做一體的實(shí)踐過程不僅有助于學(xué)生理解和掌握抽象的知識(shí)與技能,還為培養(yǎng)具有創(chuàng)新精神、工匠精神的求真務(wù)實(shí)、全面發(fā)展的創(chuàng)新型人才奠定基礎(chǔ)。

4 "結(jié)束語

基于EDA技術(shù),將項(xiàng)目驅(qū)動(dòng)教學(xué)法應(yīng)用到數(shù)字電子技術(shù)基礎(chǔ)課程教學(xué)實(shí)踐中,取得很好的實(shí)施效果。該教學(xué)法有效激發(fā)了學(xué)生的學(xué)習(xí)興趣和能動(dòng)性,具有將教學(xué)理論與實(shí)踐融為一體、學(xué)生主動(dòng)參與的突出優(yōu)點(diǎn),充分發(fā)掘?qū)W生的創(chuàng)造潛能,實(shí)現(xiàn)“高階性、創(chuàng)新性、挑戰(zhàn)度”的教學(xué)目標(biāo)。

參考文獻(xiàn)

[1] 徐東,胡曉光,劉敬猛,等.淺談在數(shù)字電路教學(xué)中

培養(yǎng)工程能力[J].教育教學(xué)論壇,2019,10(40):225-226.

[2] 吳俞憬,張祎,許一男.EDA技術(shù)在“數(shù)字電路”課

程教學(xué)中的應(yīng)用[J].中國電力教育,2021(8):72-73.

[3] 艾偉清,陳景波,王偉,等.基于FPGA的“數(shù)字電路”

教學(xué)改革探索[J].電氣電子教學(xué)學(xué)報(bào),2021,43(2):49-51.

[4] 周佳暉,杜世民,楊潤萍,等.基于Proteus和FPGA

的“虛實(shí)結(jié)合”的數(shù)字電路綜合實(shí)驗(yàn)研究[J].無線

通信技術(shù),2020,29(1):15-20.

[5] 朱敦忠,劉潔,周紅鍇.項(xiàng)目驅(qū)動(dòng)教學(xué)法在《數(shù)字電

路與EDA設(shè)計(jì)》課程教學(xué)中的應(yīng)用[J].裝備制造技

術(shù),2019(7):150-152,159.

[6] 王紅航,劉凱,鄧春健,等.數(shù)字電路和EDA課程融

合實(shí)踐與探討[J].實(shí)驗(yàn)科學(xué)與技術(shù),2018,16(2):162-165.

[7] 倪德克,師亞莉,朱旭花.EDA技術(shù)在數(shù)字電路課程

設(shè)計(jì)教學(xué)改革中的探索與實(shí)踐[J].大學(xué)教育,2016(4):"118-119.