16Gbit/s 高速串并收發器調試及交流耦合電容選取方案

張秀均,于 治,宋林峰,季振凱

(無錫中微億芯有限公司,江蘇無錫 214072)

1 引言

隨著高速數據傳輸技術的快速發展,國際上高速串并收發器(SerDes)的傳輸速率可達56 Gbit/s 乃至112 Gbit/s,如何改善高速SerDes 的傳輸性能已成為研究的熱點問題[1]。由于測試條件的限制,目前國內高速SerDes 的傳輸測試速率大多在10.3125 Gbit/s。為了保證信號的傳輸質量,AC 耦合電容廣泛應用于高速SerDes 傳輸[2],因為AC 耦合電容能夠消除收發模塊間共模電壓的失配,實現不同電壓邏輯信號間的互連。耦合電容選取不當會造成碼型抖動、信號傳輸質量惡化、誤碼率增加等。因此AC 耦合電容的選取對高速SerDes 傳輸至關重要。

相較于國外V7 系列12.5 Gbit/s 的SerDes 芯片,本研究基于公司研發的集成16 Gbit/s 高速SerDes 的FPGA 芯片,測試了不同速率下的SerDes 性能。基于可測性設計(DFT)[3]測試了不同速率下的眼圖、抖動等性能參數,并通過理論分析和實際測試比較出不同速率下性能最好的AC 耦合電容值。

2 基于DFT 的高速SerDes 調試方法

2.1 高速SerDes 結構及參數

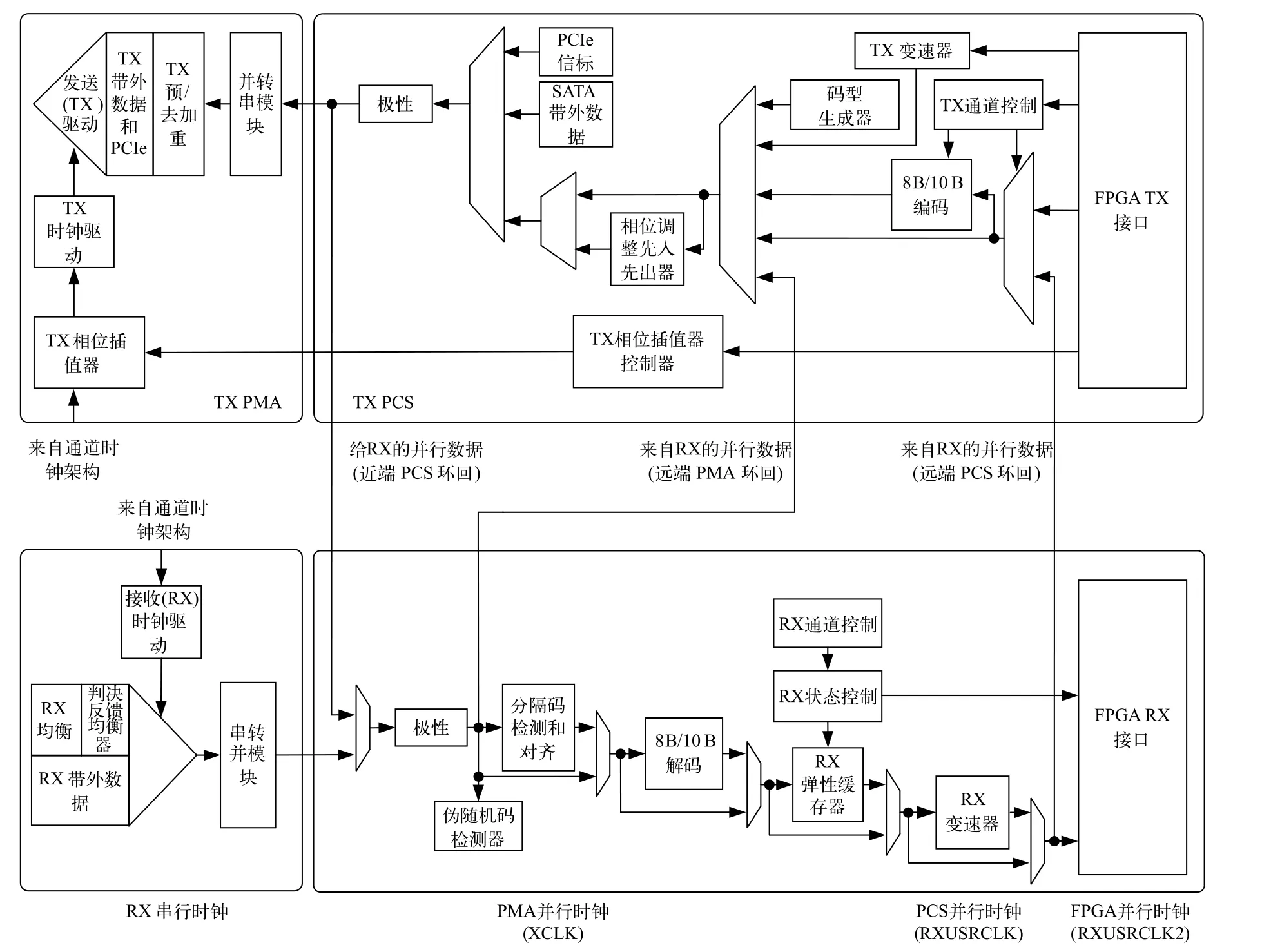

高速SerDes 由發送單元和接收單元組成,發端和收端的功能彼此相互獨立且都包含物理媒介適配層(PMA)和物理編碼子層(PCS)[4],高速SerDes 電路結構如圖1 所示。

圖1 高速SerDes 電路結構

高速SerDes 的功能本質上是實現串并轉換,發送端將并行信號經過8 B/10 B 編碼轉化為串行信號后經過信道傳輸再解碼為并行信號處理[5]。為了保證數據在高速傳輸過程中的穩定性,發送端和接收端還包含加重/預加重、時鐘驅動、均衡、時鐘恢復等模塊,每個模塊都有自己對應的參數配置。如何配置各模塊的參數在高速SerDes 調試過程中至關重要,經統計,SerDes 調試過程中需要修改的配置參數達上百個。……