PCIe 5.0 Riser Card 線纜方案PCBA設計

周敏杰

(安費諾電子裝配(廈門)有限公司,福建廈門 361009)

0.引言

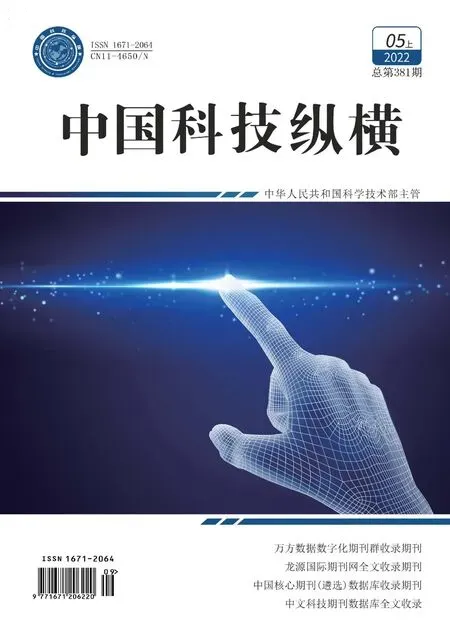

在PCIe5.0之前,服務器內(nèi)部幾乎所有的高速信號都是采用PCB走線的方式去連接,采用的方式基本就是主板+背板的方式,結構清晰,能夠滿足信號的要求。但是速率來到PCIe5.0之后,PCB走線的插入損耗大大增加,原因在于基礎頻率又從原來的8GHz(PCIe4.0)直接擴大到16GHz,這就使得原本符合PCIe4.0的系統(tǒng)要求,卻再也無法滿足PCIe5.0的要求,急需要解決的問題就是高速通道的信號插入損耗過大問題。針對這個問題,安費諾公司提出采用內(nèi)部線纜的方案去實現(xiàn)。因為線纜的插入損耗要遠小于PCB走線,通常情況下,采用線纜方案的插入損耗只有PCB走線的1/5,可以參考圖1。至此,Riser card線纜方案應運而生,而傳統(tǒng)的Riser card方案是沒有線纜的,同時高速線纜方案也是幾乎不放置電子元件的,于是這一創(chuàng)新方案必然會帶來更多的挑戰(zhàn)。

圖1 PCB trace與線纜的插入損耗對比圖

本文就是基于這2個方面的融合所產(chǎn)生的問題,對與線纜有關的過孔和焊盤而做的總結,并推薦一個可行的PCB設計方案,為后來的設計者提供參考。

1.Riser card線纜結構

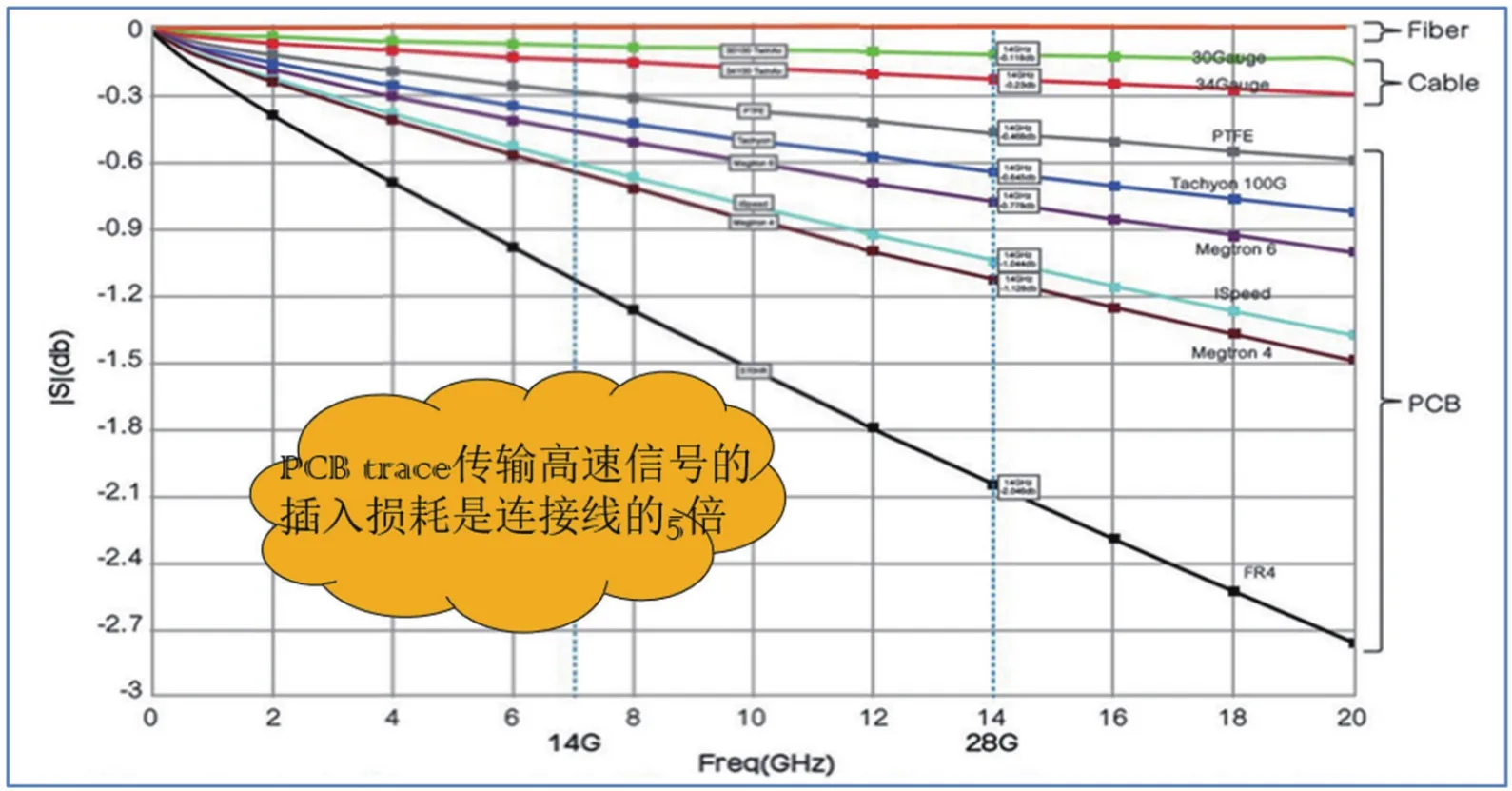

Riser card的線纜結構如圖2所示。它的內(nèi)部組成為CEM連接器+PCBA+Raw Cable+PCBA+連接器2,其中連接器2可以根據(jù)客戶需求選用不同的方案。

圖2 Riser card線纜圖示

2.Riser card線纜PCBA阻抗設計

高速信號傳輸?shù)囊粋€重要參數(shù)就是阻抗匹配,如果阻抗匹配得好,其他參數(shù)都會變好,如ILD會更平穩(wěn)、回波損耗會更小等。一般而言,Riser card的PCBA阻抗管控的好壞直接決定了這條線纜的性能,而影響Riser card PCBA的阻抗連續(xù)性主要有5個關鍵區(qū)域:

(1)高速連接器本身的阻抗;(2)高速連接器的SMT區(qū)域;(3)PCBA板上走線的區(qū)域;(4)PCBA過孔區(qū)域;(5)PCBA 焊盤區(qū)域。

2.1 Riser Card線纜PCBA過孔設計

細分以上總結的5大影響阻抗的區(qū)域,連接器本身阻抗以及SMT區(qū)域與PCB設計關系不大,而PCB走線也比較容易管控。傳統(tǒng)的Riser card與線纜方案的Riser card區(qū)別也恰恰在于過孔設計和線纜的焊盤設計,首先看過孔設計。

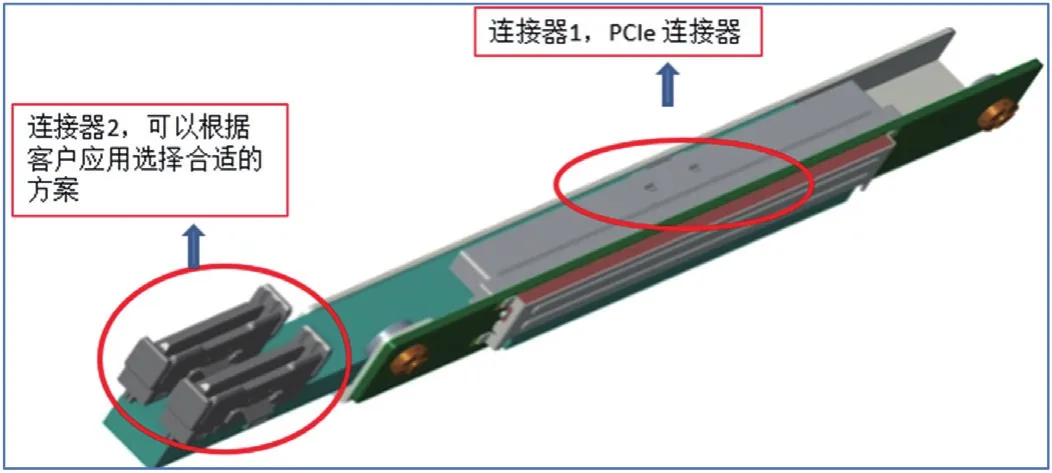

這里的過孔指的是靠近線纜焊盤的過孔,因容易受到線纜焊接的影響,會跟以往的設計不同。根據(jù)仿真結果,過孔之間的中心距與中心距的值在0.7mm~0.76mm最佳,過孔的直徑可以選擇10mils或者12mils,而最佳搭配可以參考PCB材料的DK值。過孔的尺寸可以參考圖3。

圖3 過孔及相關的避空尺寸

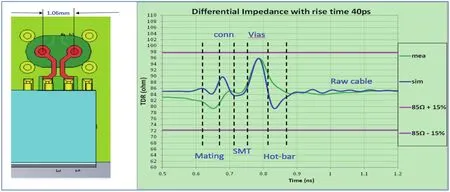

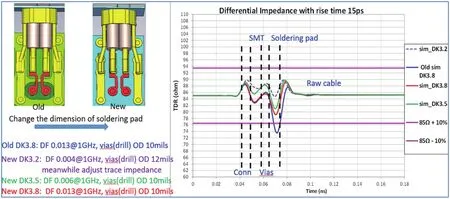

如下是采用和不采用推薦的過孔直徑仿真結果、實測結果對比,如圖4(非推薦尺寸)和圖5(優(yōu)化成推薦尺寸)所示。

圖4 采用過孔間距1.06mm的設計仿真和實測對比

圖5 按照推薦尺寸的仿真結果

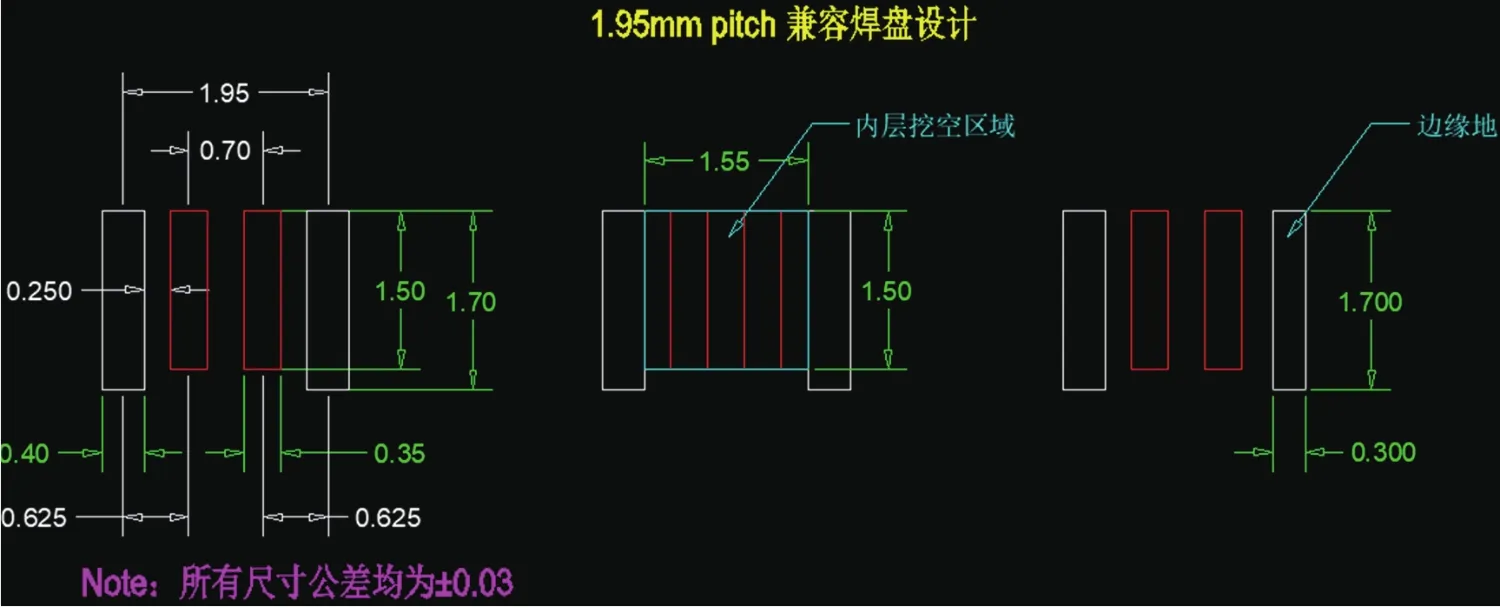

2.2 Riser card PCBA焊盤設計

針對PCBA焊接區(qū)域,要考慮焊線、涂UV膠及內(nèi)模工序會使該區(qū)域的阻抗下降。因此,設計時需同時考慮該區(qū)域焊盤區(qū)域的阻抗線材、UV膠及內(nèi)模綜合因素等。經(jīng)過多次的實驗和仿真,推薦焊盤尺寸如圖6所示。同時給出仿真數(shù)據(jù),采用不同的PCB材料、不同的過孔尺寸所做的一個結果對比,如圖7所示。

圖6 焊線焊盤的推薦尺寸

圖7 經(jīng)過焊線、涂UV膠及內(nèi)模工序后的仿真(已隱藏UV膠和內(nèi)模部分)

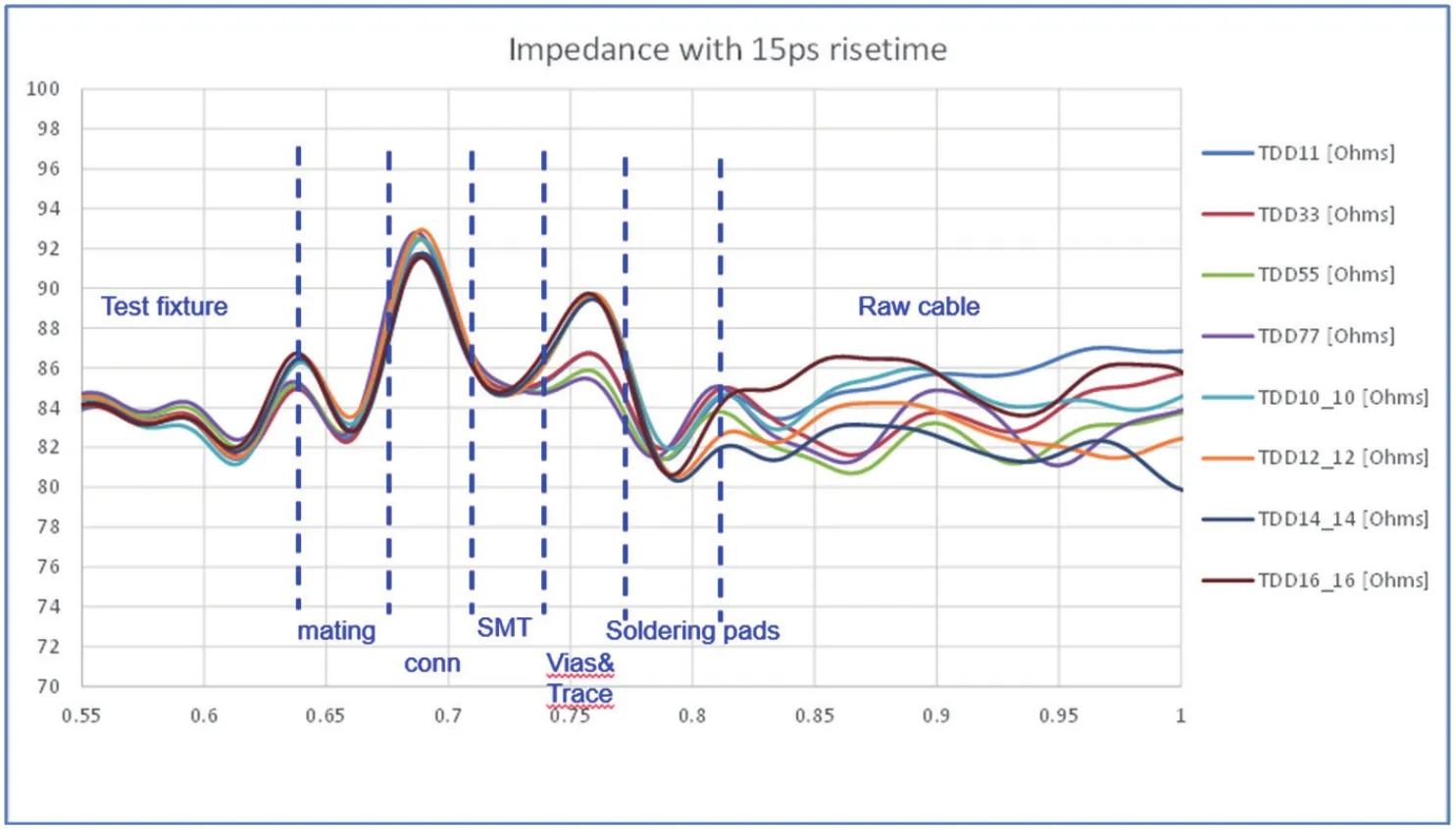

以上結果是基于仿真的結果,而焊盤區(qū)域的阻抗還與制程密切相關,如焊點錫量過大,就會導致阻抗偏低很多。所以對于PCIe5.0的應用,最好推薦DK相對較低的材料,并結合焊點較理想制程管控才能得到合格的SI要求。如下實測的阻抗曲線圖可供參考,如圖8所示。

圖8 實測阻抗曲線圖

3.結語

本文提出通過CST仿真軟件,結合Riser card線纜實測數(shù)據(jù),模擬仿真Riser card PCBA阻抗與實測數(shù)據(jù)的對比,并推薦出PCIe5.0 Riser card線纜方案的PCBA設計方案,重點推薦了高速信號在焊盤附近的過孔尺寸,以及焊線焊盤的尺寸。參考此方面的設計經(jīng)驗,可以大大縮小開發(fā)時間,因此可以避開傳統(tǒng)Riser card與線纜Riser card的設計不同而導致系統(tǒng)調(diào)試失敗。線纜Riser card是一種傳統(tǒng)高速線纜與傳統(tǒng)的Riser card的技術融合。