一種相控陣雷達多通道同步方法*

祝昇翔,何岷,賀志毅,王嘉欣

(北京遙感設備研究所,北京 100854)

0 引言

相控陣技術自出現以來,憑借其波束快速掃描和靈活捷變,以及空域濾波和定向能力,大大提升了雷達的威力[1]。早期的相控陣雷達采用經典的和、方位、俯仰三通道方式,使用了大量移相器、衰減器、和差器等模擬器件。而多通道相控陣雷達包括多個天線子陣、射頻和信號處理通道,更多地使用了數字方式。采用多通道工作方式后,系統自由度大幅度提升。按照軟件無線電的思想,將數字處理部分前移,雷達系統能夠支持自適應波束形成、空間譜估計、空時自適應信號處理等先進空域處理算法,極大地提升了系統的性能[2-4]。

目前,多家研究機構開展了多通道相控陣雷達的關鍵技術研究和系統研制[4-6]。文獻[5-6]將新型高速模數轉換器(analog to digital converter,AD)和數模轉換器(digital to analog converter,DA)用于多通道相控陣雷達模擬器和數字化收發組件研制。采用多通道方式并不意味著通道數目的簡單疊加,伴隨而來的就是單個通道的采樣速率和數據傳輸速率提升后,多個通道之間的一致性難以保證,導致系統性能下降。文獻[7-8]研究了大型分布式陣列雷達的時間、頻率和相位同步問題。事實上,對所有多通道相控陣雷達來說,同步問題都是必須解決的首要問題。

隨著技術的進步,AD 和DA 的采樣速率已達到每秒千兆次采樣(gigabit samples per-second,GSPS)量級[9-10]。而傳統的并行器件存在采樣速率受限,占用管腳多等問題,無法滿足多通道和小型化的工程需求。為解決這一矛盾,JEDEC(joint electron en?gineering council)組織發布了JESD204B 標準[11],采用串行數據鏈路和共模邏輯電平方式,簡化了系統設計,降低了功耗,支持通道間同步功能,傳輸速率可達12.5 Gbps。目前,廠商推出了大量支持該標準的器件和知識產權。國內多家單位均開展了基于該標準的多通道數據采集板卡和同步技術研究[12-18]。

針對相控陣雷達多個時鐘芯片和多個模數轉換器均需要同步的難題,本文提出了一種多通道同步方法,以雷達時序信號為基準,實現多個時鐘芯片和模數轉換器的同步,以滿足同步的實際需求。

1 多通道相控陣雷達

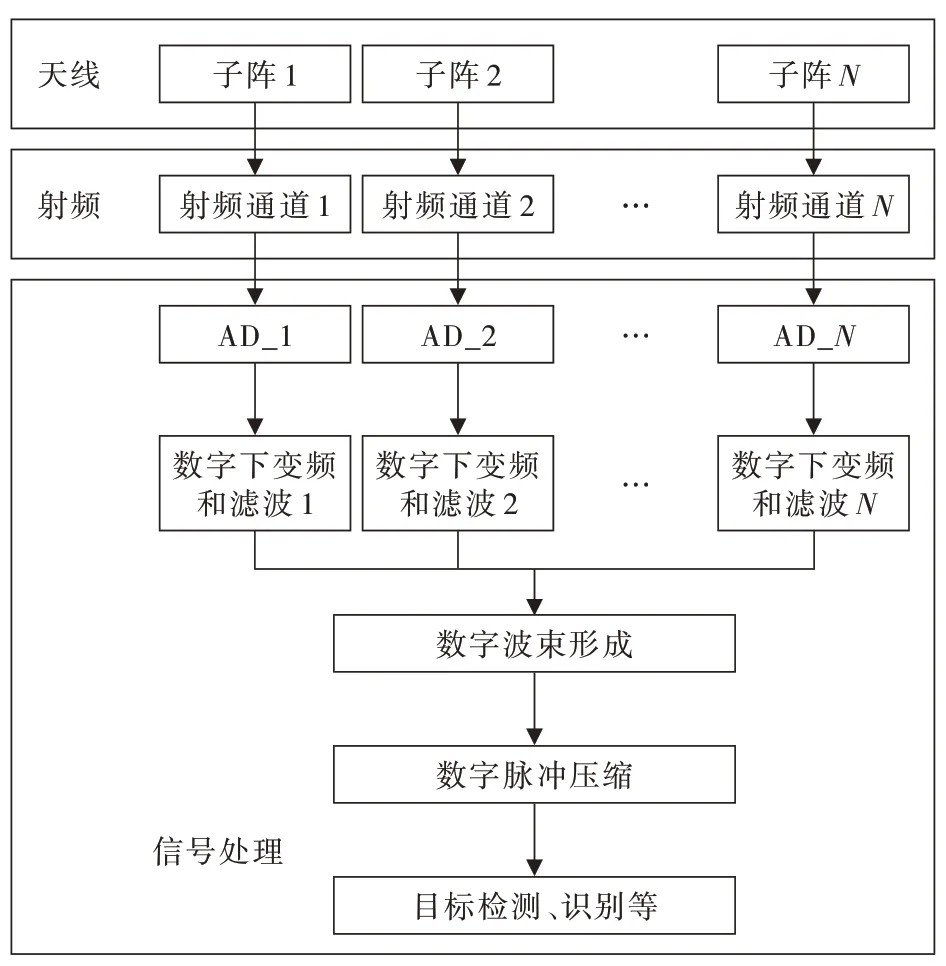

1.1 雷達系統

多通道相控陣雷達系統由天線、射頻和信號處理等分系統組成,如圖1 所示。其中天線按照天線陣面分為多個子陣,每個子陣與對應的射頻通道連接。除了變頻收發功能外,射頻分系統還負責提供時鐘。信號處理分系統由多片高速AD 對多通道的子陣數據進行采集,然后進行數字下變頻和濾波,通過數字波束形成得到所需要的波束,進行數字脈沖壓縮實現匹配濾波,完成目標檢測和識別等功能。

圖1 多通道相控陣雷達系統Fig.1 Multi-channel phased array radar system

1.2 問題提出

雷達系統通過發射電磁波信號,并接收目標反射的回波,完成最基本的測距功能。

式中:τ為電磁波往返的雙程延時;R為雷達與目標的單程距離;c為光速。

雷達發射波形為線性調頻信號,其基帶形式為

式中:rect()為矩形信號;T為信號脈寬;k為線性調頻斜率。

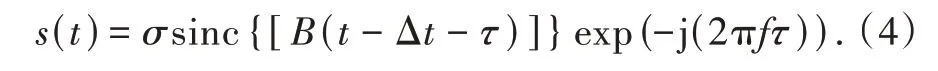

雷達發射的信號被場景中的單個點目標反射后,對收到的回波信號進行數字下變頻和脈沖壓縮,可得到

式中:σ為目標的散射系數;f為載波頻率;sinc()為辛格函數。

雷達系統使用AD 對回波信號進行數據采集,其時序由采樣波門和采樣時鐘決定。當發生采樣偏差時,即在時域上產生了Δt的偏差,式(3)變為

此時,脈沖壓縮結果發生了Δt的偏差,對應測距結果產生偏差,直接影響后續的目標檢測和跟蹤環節。特別是對于多通道系統來說,由于多個通道需要進行數字波束形成來實現相參處理,這種偏差的影響更大。

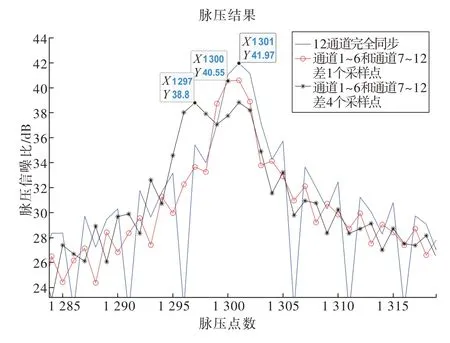

設置線性調頻信號帶寬為40 MHz,脈寬為26 μs,采樣率為100 MHz,使用12 個通道進行仿真,結果如圖2 所示。可以看出,當一半通道存在一個采樣點的偏差時,數字波束形成的和波束脈壓增益下降約1.4 dB。當一半通道存在4 個采樣點的偏差時,數字波束形成的和波束脈壓增益下降約3.2 dB,而且結果變為了2 個尖峰,嚴重影響后續的目標檢測和測量。

圖2 多通道間存在偏差時脈壓結果圖Fig.2 Pulse compression results with deviations among multiple channels

2 多通道同步

2.1 時鐘芯片同步

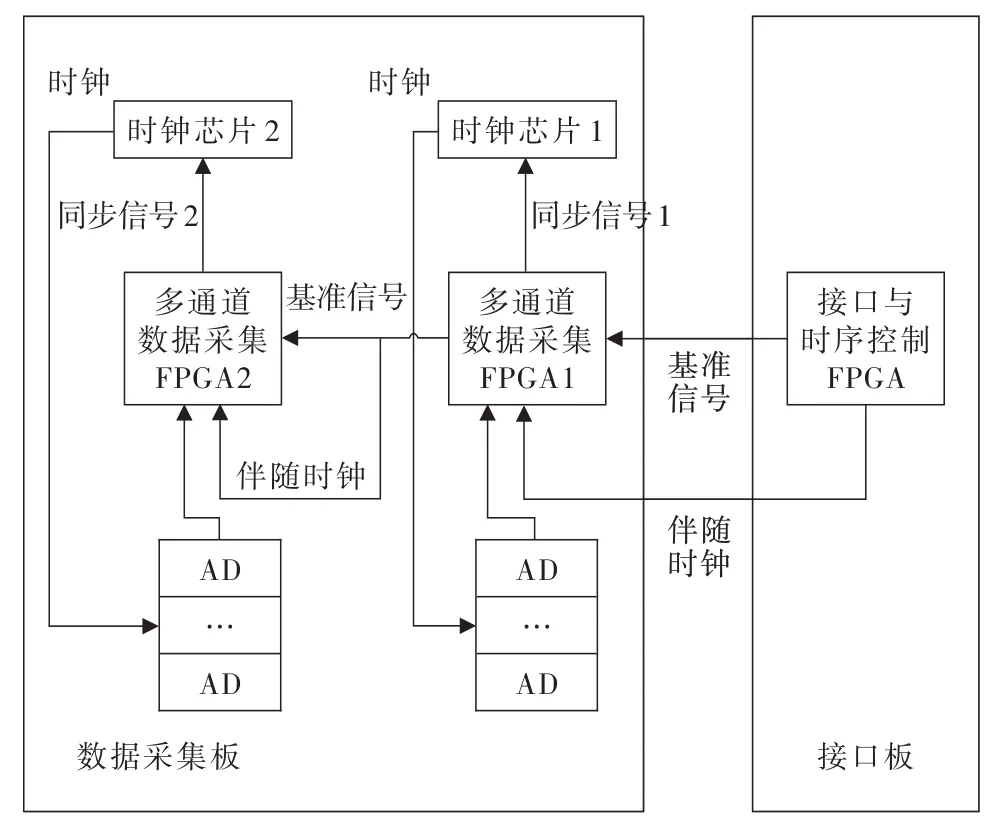

雷達信號處理分系統由接口板上的現場可編程門陣列(field programmable gate array,FPGA)產生雷達工作時序信號。將該信號作為基準和伴隨時鐘一起傳給數據采集板。數據采集板的時鐘芯片對射頻分系統中的頻率源提供的時鐘進行鎖相、分頻后,輸出多路采樣時鐘、器件時鐘以及同步參考信號SYSREF,提供給多片AD 和FPGA,AD以SYSREF 信號為基準進行模數轉換,如圖3所示。

圖3 多通道信號處理框圖Fig.3 Multi-channel signal processing

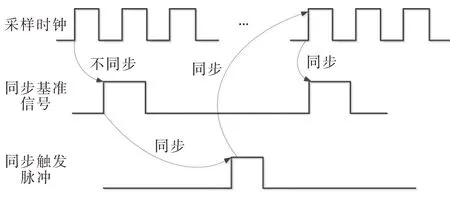

時鐘是高速多通道數據采集系統的基準,雖然輸入時鐘均來自同一個頻率源,但是數據采集板的時鐘芯片輸出的時鐘和同步參考信號,與接口板FPGA 輸出的基準信號并不能保證每次上電后相位關系一致[19-20]。為了解決該問題,首先采用基于外同步觸發信號的同步方法,對單個時鐘芯片進行同步。數據采集板的FPGA 根據基準信號的上升沿,在伴隨時鐘下采樣產生同步觸發脈沖,并輸出給時鐘芯片。重新配置其寄存器,使得時鐘芯片以同步觸發脈沖為基準,重新輸出AD 采樣時鐘和SYSREF 信號等。配置完成之后,時鐘芯片輸出的所有時鐘均以雷達工作時序為基準,完成了單時鐘芯片同步,如圖4所示。

圖4 單時鐘芯片同步圖Fig.4 Synchronization of single clock chip

由于雷達通道數多,而單個時鐘芯片輸出時鐘數目有限,因此實際當中需要使用多個時鐘芯片驅動模數轉換器。雖然配置和同步方式完全一致,但是多個時鐘芯片所使用的基準信號,伴隨時鐘以及時鐘芯片同步信號對應的印制板走線延時和FPGA內部布線延時各不相同。延時差異導致不同時鐘芯片對應的AD 采樣結果存在極小的偏差。采用常規方法難以對這類偏差進行測量和補償。

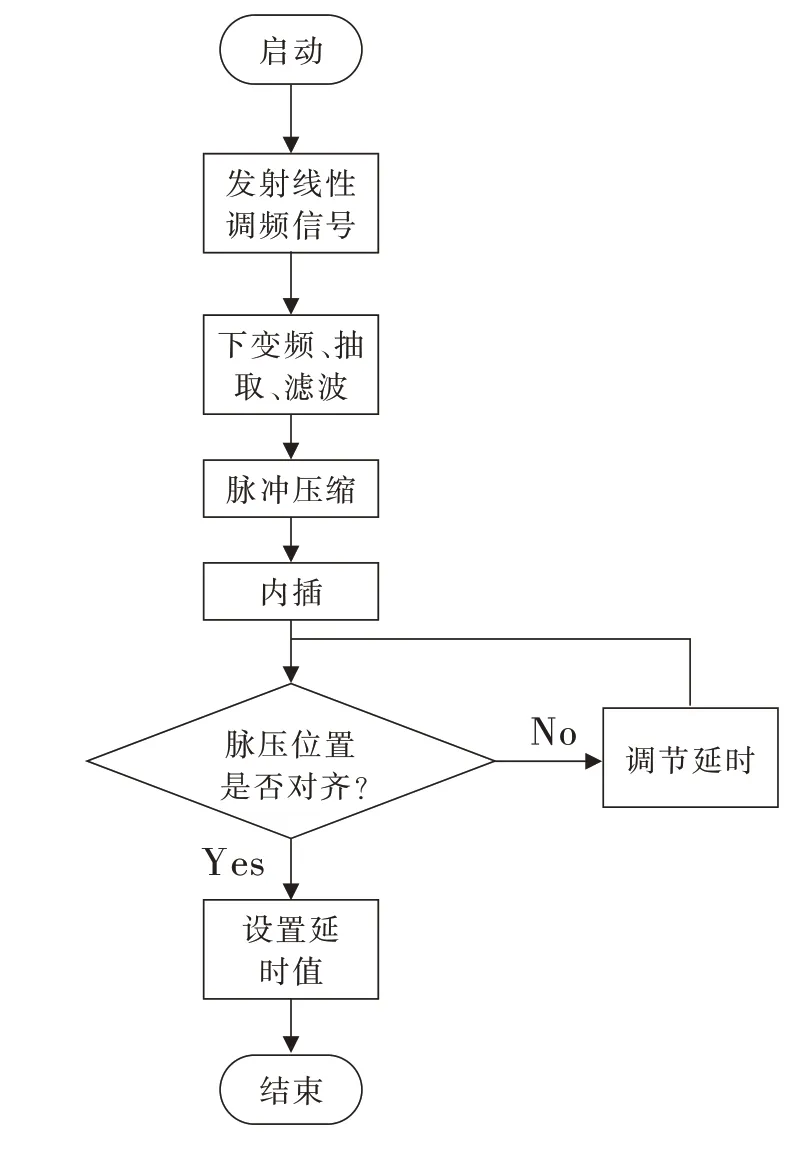

為了解決多個時鐘芯片同步的難題,采用FPGA片內的輸出延時單元ODELAY,通過精確的延時調節,實現多個時鐘芯片同步信號延時不一致的補償。具體方法為:使用接口板發射線性調頻信號,經過射頻通道接收后由數據采集板對收到的信號進行AD采樣、下變頻、抽取、濾波、脈沖壓縮和內插處理,得到脈壓峰值點位置。然后以時鐘芯片1 對應通道的脈壓位置為基準,逐步調節時鐘芯片2 對應的時鐘芯片同步信號的延時,使得二者最終一致,即可完成多時鐘芯片同步,如圖5 所示。其中ODELAY 的參考時鐘fclk為200 MHz,內部共32 階,每一階的延時為1/(2 × 32 ×fclk),約78 ps,根據實際測量結果計算得到延時值,然后寫入ODELAY 的配置即可。

圖5 多時鐘芯片同步框圖Fig.5 Synchronization of multiple clock chips

2.2 模數轉換器同步

為了滿足多通道高速數據采集的需求,選用支持JESD204B 標準子類一的AD 器件,支持傳輸層的幀填充功能,擾碼功能,鏈路層的8B/10B 編碼功能,以及同步字符產生和初始鏈路對齊功能。該標準定義了鏈路的確定性延遲,即基于幀的采樣數據到達串行發送器的時間與數據從串行接收器輸出的時間之差。子類一使用外部參考信號SYSREF 來支持確定性延遲,是器件同步的關鍵。器件時鐘作為系統基準,用于數據采樣和捕獲SYSREF 信號。確定性延遲的精度取決于SYSREF 和器件時鐘之間的關系。當多片AD 需要同步時,為了滿足采樣窗口的建立和保持時間要求,需要對每一個器件的器件時鐘和SYSREF 信號進行走線匹配以保證時序。

每個AD 通道采用一個JESD204B 控制器進行協議解析和數據格式轉換,通過FPGA 實現。根據采樣速率,每個控制器內部可設置L個lane(差分信號對)。由于每次上電后各個lane 的數據延時并不相同,導致最后的AD 采樣數據延時也各不相同,因此提出一種自適應采樣窗口中心調節的AD 多通道同步方法,以實現自校準同步。

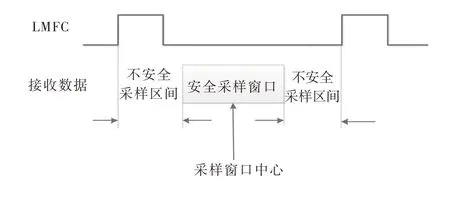

假定幀大小F=2,每個多幀中的幀數K=16,二者的乘積為多幀大小MF=32。根據本地多幀時鐘(local multiframe clock,LMFC)的時序要求,采樣時刻需要在安全采樣窗口內,才能保證可靠采樣,如圖6 所示。根據此MF值,扣除掉不安全采樣區間后,得到安全采樣窗口的范圍應為8~24。

圖6 采樣窗口圖Fig.6 Sample window

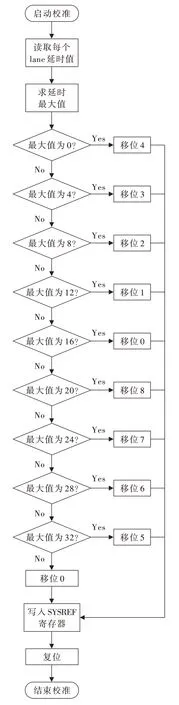

在AD 配置完成后,依次讀取L個lane 對應的延時緩沖寄存器,獲取每個lane 的延時值,并求它們的最大值。根據該最大值的大小設置移位值,將采樣中心統一移到16,即安全采樣窗口的中心位置,并寫入SYSREF 寄存器,從而調節SYSREF 同步信號時序進行對齊。需要注意的是,移位方向是單向的,因此當延時值大于采樣中心位置16 時,需要按照折疊方式設置移位值。最后,對所有AD 通道對應的JESD204B 控制器在同一時刻進行復位,即可完成多個AD 通道的同步,如圖7 所示。多通道同步精度為一個采樣點,如果AD 采樣率為1 GSPS,則可實現的同步精度為1 ns。

圖7 多通道AD 同步流程圖Fig.7 Synchronization of multi-channel AD

3 測試結果

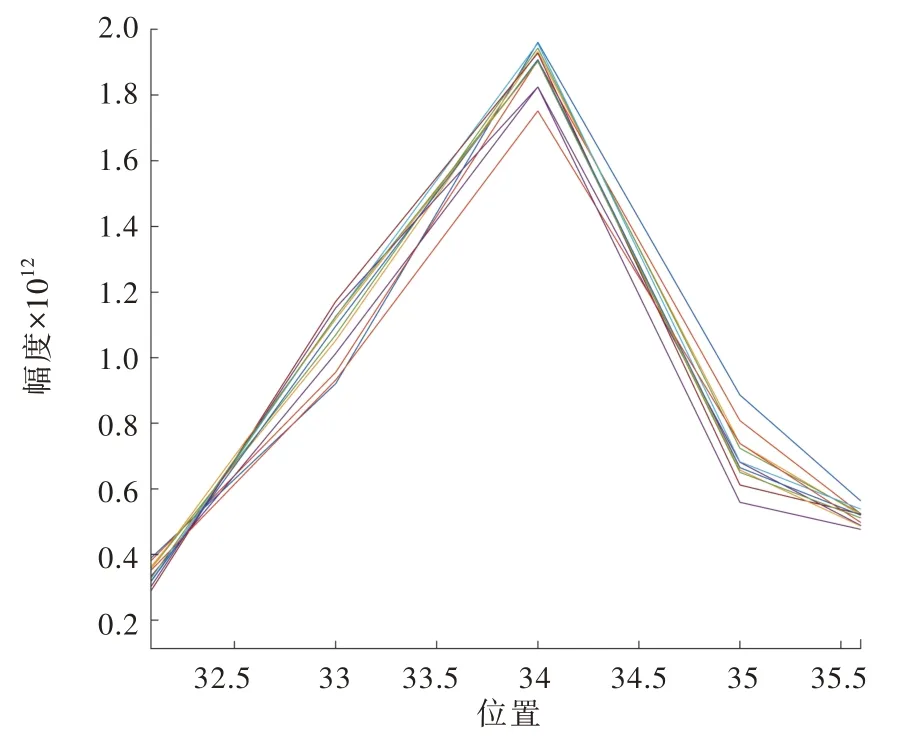

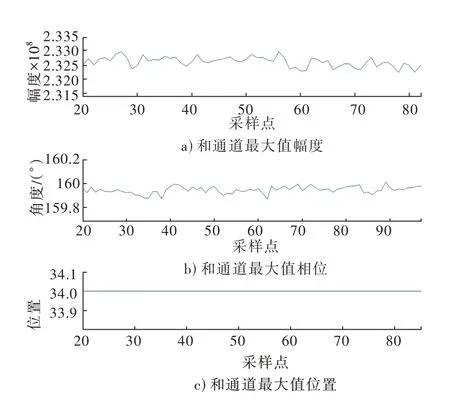

對相控陣雷達多通道同步性能進行測試。上電后用模擬器發射線性調頻波形,用數據采集板接收并采集多通道數據。將經過AD 采集、混頻、抽取、濾波等處理的數字下變頻實時處理數據,存儲在數據采集設備后,對數據進行后處理分析,結果如圖8,9 所示。圖8 為多通道脈壓結果的位置,峰值位置均為34。圖9 為在多個脈沖重復周期測得的數字波束形成的和波束幅度、相位和脈壓位置。可以看出,經過多通道同步處理后,脈壓位置、信號幅度和相位都是穩定的。

圖8 多通道脈壓位置圖Fig.8 Pulse compression positions of multiple channels

圖9 和波束幅度、相位和脈壓位置圖Fig.9 Amplitude,phase and position of pulse compression of sum beam

4 結束語

本文針對多通道相控陣雷達面臨的同步問題,提出了一種多通道同步方法。首先采用基準時序產生觸發脈沖實現單時鐘芯片同步,然后對同步信號進行ps 級精確延時補償實現多時鐘芯片同步,采用自適應采樣窗口中心調節實現多路AD 的精確采樣同步,最終實現了相控陣雷達多個通道的穩定同步。將該方法應用于實際產品,確保了雷達系統的測量性能,具有較高的應用價值。