基于SoC FPGA 的FPGA to HPS數據通信系統設計*

劉春雅

(陜西國防工業職業技術學院,陜西 西安 710300)

1 概述

數字信號處理領域內較為典型的應用為ADC高速數據采集及處理,由中端或高端FPGA 完成若干通道的ADC 接口邏輯,數據接收后進入FPGA 邏輯,之后再進行諸如FIR 濾波、FFT 運算等數字信號處理。處理后的一些相關信息及運算結果需要通過支持TCP/IP 協議的以太網GE 口、USB、CAN 等接口發送至上位機、存儲單元或其他設備,而支持TCP/IP 協議的以太網GE 口、USB、CAN 等接口都帶有協議解析部分的處理,這在傳統的純FPGA 邏輯內很難實現對這部分協議的解析和處理。在很多對小型化、低功耗等一些設計指標約束條件較高的場合,傳統的單FPGA 架構的方案就會顯得難以適從。

2 SoC FPGA 的特點

CycloneV SoC FPGA 是Intel PSG 推出的一款在單芯片上集成了ARM 雙核Cortex-A9 處理器和FPGA 邏輯的真正意義上的SoC 芯片。它的出現正好能夠解決上述問題,單芯片ARM+FPGA 的架構不僅能夠完成以前FPGA 所擅長的ADC 接口及數字信號處理等功能,還可以通過片上內部的ARM來實現以太網GE 口、USB、CAN 等不太好使用FPGA 去實現的一些接口,不僅如此還能夠利用ARM 運行嵌入式操作系統完成復雜的單板事務流程控制及管理、人機交互界面等。單芯片的SoC 方案對設備小型化、低功耗化的設備發展方向提供了有力的幫助。

SoC FPGA 內部的ARM 側和FPGA 側的數據通信是由3 個橋實現的,分別是H2F_AXI_Master橋,用于完成HPS(即Hard Processor System,HSP 為包含了ARM 雙核Cortex-A9 處理器、FLASH 及SDRAM 控制器及諸多外設接口等在內的一整套完整的硬核CPU 系統)向FPGA 發起數據讀寫操作;F2H_AXI_Slave 橋,用于完成FPGA 向HPS 發起數據讀寫操作;H2F_LW_AXI_Master 橋,用于HPS 向FPGA 發起一些控制指令或較小帶寬數據讀寫。

對于之前提到的典型應用為高速ADC 數據采集及處理來講,需要確保FPGA 側處理完的數據等信息能夠最終送往HPS 側才能讓SoC FPGA 發揮出應有的作用。

3 設計實現

3.1 Avalon MM Master Templates 簡介

Avalon MM Master Templates 實現了Avalon MM Master 功能。通過這個Avalon Master 接口,用戶能夠向對應的Avalon Slave 設備寫入數據,也能夠從對應的Avalon Slave 設備讀出數據。

該Templates 在使用時需要區分讀或寫兩個模式,也就是說在使用時需要指定其工作模式是讀或寫中的一種,一個Instance 無法同時支持讀寫雙向,如果需要讀寫雙向,可以在系統搭建的時候例化兩個Avalon MM Master Templates 并分別指定為讀和寫模式。

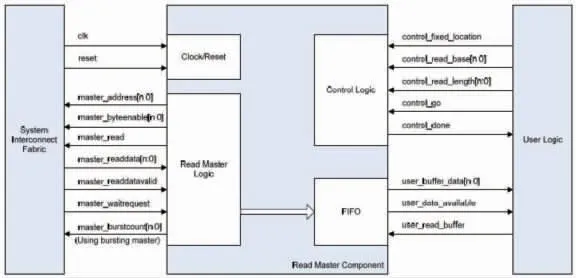

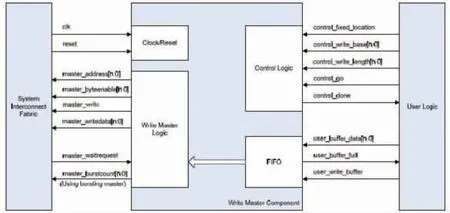

Avalon MM Master Templates 讀和寫模式頂層結構,(如圖1 和圖2 所示):

圖1 Master 讀模式

圖2 Master 寫模式

對于Master Templates 的讀或寫模式來說,都是由四個基本模塊構成的,分別是時鐘復位、讀/寫Master 邏輯、控制邏輯及FIFO 邏輯。

時鐘復位考慮到同步設計一般在Platform Designer 系統中保持與整個HPS 系統一致。

讀/寫Master 邏輯部分的接口是與對應的Slave設備對接的,使用時在Platform Designer 中需要進行連接。

3.2 Platform Designer 系統搭建

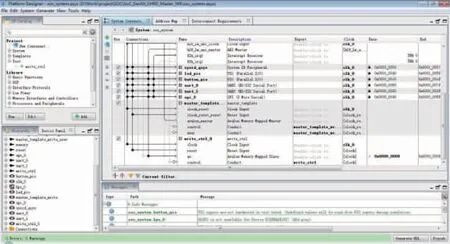

添加Master Templates 到系統并修改其配置參數,需要將Master Direction 設置為“Write”,即FPGA 主動發起寫操作到HPS 側。Data Width 選為32bit,其有8、16、32、64、128、256、512 和1024 共計8 個選項。Address Width 選為32bit,與ARM 位寬匹配。打開burst 使能,并設置最大的burst 長度為128,可以根據實際的數據吞吐量進行設置。按照這個設置,一次burst 最大可以傳輸32×128bit=4096bit的數據。配置FIFO 深度為256,使用memory based方式,即使用FPGA 內部的Block RAM 搭建FIFO,按照這個設置,32×256 會占用FPGA 內部的一個M10K 做FIFO。最后將master_template 的控制端口和FIFO 端口Export 出來,以便用戶進行控制和數據寫入。

為了方便后面的測試,還需要編寫一個Avalon MM Slave的模塊,將該模塊掛在HPS 的h2f_lw_axi_master 這個輕量級總線橋上,在測試過程中可以通過ARM 運行的應用程序來控制master_template 的寫入。該模塊可以設計含有3 個寄存器,分別用于控制master_template 的control_go,control_write_base 及control_write_length。編寫完成的代碼需要在Platform Designer 工具中添加為一個元件進來并掛在h2f_lw_axi_master 這個輕量級總線橋上了。

之后在 Platform Designer 工具中將這個write_ctrl 作為一個模塊添加到HPS 系統中,連接好時鐘及復位信號,將HPS 的h2f_lw_axi_master 連接到該元件的as(即Avalon MM Slave)端口。最終連接好的整個HPS 系統如圖3 所示:

圖3 添加并連接write_ctrl 模塊到HPS 系統

對搭建好的HPS 系統分配基地址,Generate HDL 后得到HPS 部分的HDL 代碼。至此,HPS 側的硬件系統搭建完成。

硬件部分完成后,需要在SoC EDS 工具中生成Linux 軟件和驅動所需包含的hps_0.h 頭文件,該頭文件包含了HPS 側全部的外設及接口IP 寄存器定義等。

其命令為:sopc-create-header-files“./soc_system.sopcinfo”--single hps_0.h--module hps_0

生成設備樹dts 并轉換為Linux 系統啟動所需的dtb。

其命令為:make dtb

由于dtb 文件中包含的信息是與一個具體的Quartus 工程對應的,在啟動時,Linux 操作系統會根據dtb 文件中的硬件描述去初始化FPGA 側添加的各種IP。

3.3 Avalon MM Master Templates 驅動程序設計

開始Linux 應用程序設計之前,需要先為Avalon MM Master Templates 編寫相應的驅動程序,否則Linux 內核無法識別該外設。驅動程序中:

(1)amm_wr_init(viod)為驅動模塊入口,Linux在加載設備驅動時會首先執行該函數并獲取到該設備的主設備號。其中:

①ret=alloc_chrdev_region(&devno,minor,1,"amm_wr");獲取設備號,設備節點命名為"amm_wr"。

②my_kernel_buffer=dma_alloc_coherent(NULL,dma_size,(void *)&(my_kernel_buffer_phy),GFP_K ERNEL);為DMA 內存申請,申請內存大小為dma_size。my_kernel_buffer_phy 為申請到的內存物理首地址,FPGA 使用的就是該實際的物理地址。my_kernel_buffer 為DMA 內存空間虛擬地址指針。

(2)amm_wr_read 函數實現從內核空間讀取數據到用戶空間,copy_to_user (buf,my_kernel_buffer,count)為從my_kernel_buffer 中拷貝count 個數據到用戶空間buf 中。

(3)amm_wr_ioctl 函數是設備驅動程序中對設備的I/O 通道進行管理的函數。所謂對I/O 通道進行管理,就是對設備的一些特性進行控制。put_user(data,(unsigned int *)arg)可將my_kernel_buffer_phy物理地址拷貝到用戶空間。應用程序在調用ioctl 函數時,就能夠得到該物理地址,并通過寫write_ctrl這個Slave 模塊其中的base 寄存器操作,將FPGA發起寫傳輸所需的物理地址告知FPGA。

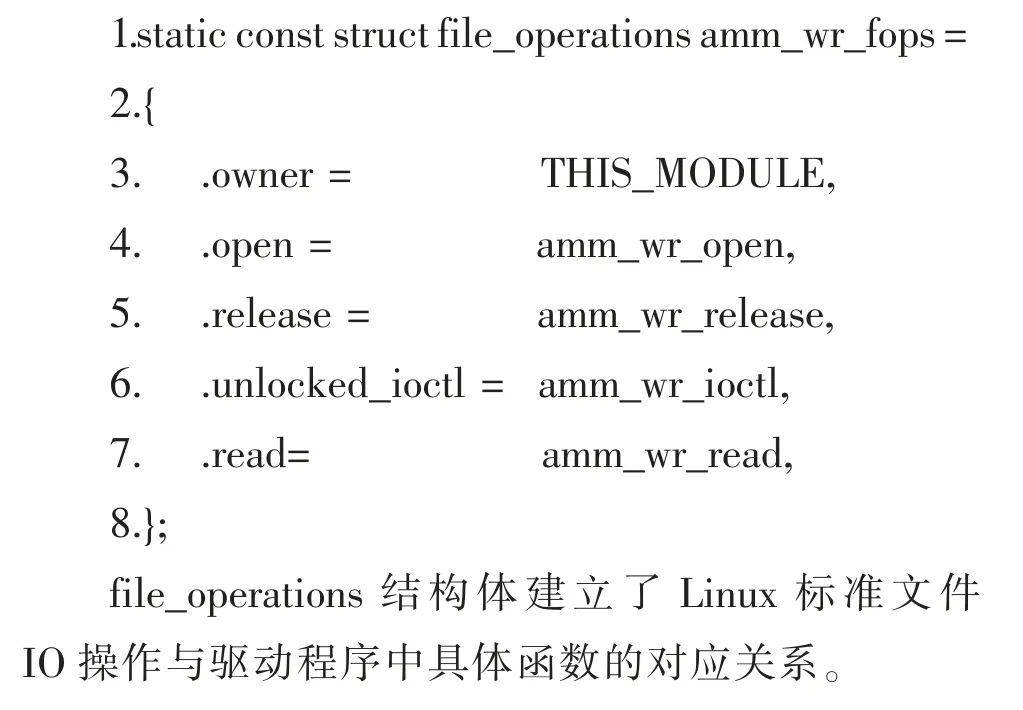

(4)fops 定義部分:

其余部分主要為amm_wr_open 打開函數,amm_wr_release 關閉函數,amm_wr_exit 驅動出口函數及一些聲明等。

將此驅動的源碼上傳至Ubuntu 系統下,使用root 賬戶登錄Ubuntu,設置好處理器架構,設置好交叉編譯工具,并在Makefile 中指定好linux-soc fpga源碼路徑,之后就可以編譯得到后綴為.ko 的驅動模塊文件。應用程序開始執行之前,需要先使用insmod 命令安裝這個驅動模塊。

3.4 Linux 應用程序設計

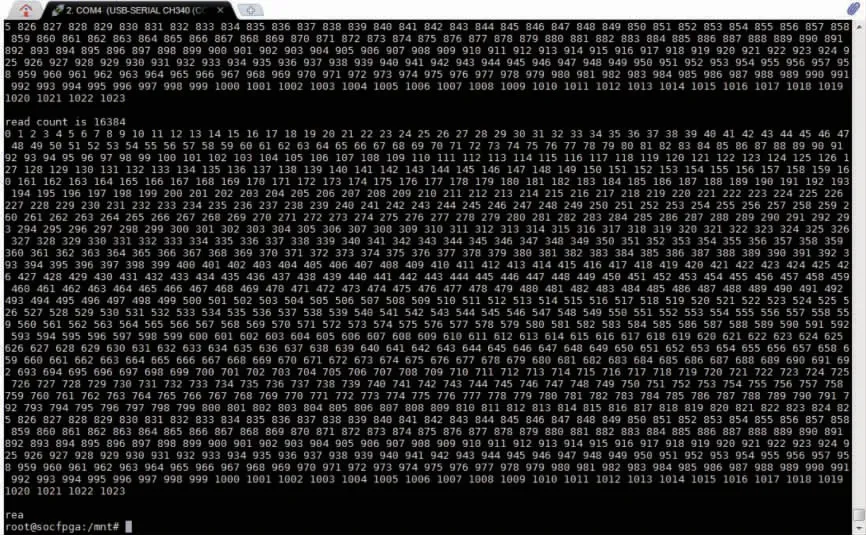

應用程序的功能主要是為了測試整個HPS 底層的硬件系統,檢驗是否能夠完成FPGA 邏輯側的數據寫入HPS 側的DDR 中,并可將最終寫入DDR的數據讀取到Linux 的用戶空間并打印顯示出來。

該應用程序通過寫模式的Avalon MM Master Templates,將FPGA 邏輯代碼生成的16384 個數據從邏輯側寫入到了HPS 側的DDR 中儲存,再通過read 函數讀取到用戶空間的read_buffer 中,最后為了顯示方便,僅打印出了前1024 個數據。

應用程序中:

(1)periph_vir_base=mmap(NULL,HW_REGS_SPAN,(PROT_READ|PROT_WRITE),MAP_SHARED,fd,HW_REGS_BASE);為通過mmap 函數將以地址(HW_REGS_BASE)為起始的一段空間(HW_REGS_SPAN)進行虛擬地址映射,得到了HPS 全部外設的虛擬地址,其中也包括了HPS 側的h2f_lw_axi_master 總線橋的虛擬地址。

(2)write_ctrl_vir_base=periph_vir_base+((unsigned long)(ALT_LWFPGASLVS_OFST+MASTER_CTRL BASE)&(unsigned long)(HW_REGS_MASK));可得到write_ctrl 自定義元件的基地址,其基地址由外設虛擬基地址+h2f_lw 總線橋的偏移地址+write_ctrl 元件相對于h2f_lw 總線橋的偏移地址得到。

(3)int trans_init(void)函數為通過ioctl 系統調用得到申請到的DMA 的一段地址空間,并將這段空間的基地址寫入FPGA 側write_ctrl 元件的寄存器,同樣的方式,也寫入了數據長度參數。FPGA 得到這兩個參數就能夠向這個地址寫入此數據長度的一段數據了。

(4)main 函數內,先對整個系統做了復位,以清除Avalon MM Master Templates 內FIFO 的多余數據,確保FIFO 不會有殘存數據影響本次測試。之后軟件通過寫寄存器的方式向write_ctrl 元件寫入控制指令,控制go 發一次脈沖來啟動傳輸過程。之后調用read 函數將16384 個數據讀取到用戶空間的read_buffer 儲存,最后通過for 循環,將儲存 的16384 個數據打印出來,為了方便顯示,只打印出了前1024 個數據。

(5)程序退出時需要取消虛擬地址映射并關閉打開的文件描述符。

3.5 應用程序測試

在SoC EDS 中輸入“eclipse &”打開DS-5 并新建軟件工程,添加源代碼和必要的文件包含路徑后編譯工程,得到二進制程序文件,再為該文件添加可執行權限。運行應用程序得到的結果(如圖4 所示)。

圖4 應用程序運行結果

4 結束語

從該FPGA to HPS 數據通信系統設計最終的測試結果來看,完全達到了芯片內部FPGA 側到ARM 側的數據通信的目標。如FPGA 邏輯側接的是ADC 數據或是用戶經過數字信號處理運算后的數據,通過此方案就可以達到將數據送往ARM 側的目的。之后再通過相應的嵌入式軟件開發,就可以完成將數據最終通過TCP/IP 協議的GE 口,USB,CAN 等接口送出的任務。故該方案可以成為通用的SoC FPGA 數據交互通信方案,具備較強的參考價值。