SiC MOSFET串聯短路動態特性

張經緯 張 甜 馮 源 宋明軒 譚國俊

SiC MOSFET串聯短路動態特性

張經緯 張 甜 馮 源 宋明軒 譚國俊

(中國礦業大學電氣與動力工程學院 徐州 221116)

在電力電子系統中,因器件擊穿、硬件電路缺陷或系統控制失誤導致碳化硅(SiC)金屬氧化物半導體場效應晶體管(MOSFET)誤開通時,橋臂電流回路中多個器件處于開通狀態,形成串聯短路故障。該文以SiC MOSFET半橋電路為研究對象,詳細介紹SiC MOSFET串聯短路的動態過程,理論分析負載電流、柵極驅動電壓和結溫溫升對SiC MOSFET短路動態特性的影響規律,推導出SiC MOSFET分壓模型,并采用仿真模型進行驗證。實驗基于1 200V/80A SiC MOSFET測試平臺驗證電路參數對短路損耗和結溫分布的影響。理論與實驗結果表明,SiC MOSFET串聯短路分壓特性對電路參數具有較高敏感度,漏極電壓與漏極電流不平衡動態變化會改變器件短路損耗,進而影響結溫溫升,造成串聯短路SiC MOSFET不穩定變化。

SiC MOSFET 串聯短路 分壓特性 結溫分布

0 引言

SiC MOSFET作為新一代功率半導體器件,正處在快速商業化發展階段。SiC MOSFET因其具有高開關速率、低開關損耗、高擊穿電壓、高熱導率等特點,已被廣泛應用于新能源汽車、太陽能、風能變換器、無線電能傳輸等領域[1-5]。但是,SiC MOSFET的挑戰是與優勢共存的[6-8],尤其是在以短路故障為代表的極端故障下,高壓、大電流、高結溫所帶來的沖擊嚴重影響了器件的性能。在高柵極電壓下,SiC MOSFET發生短路故障時產生的短路電流是額定電流的數倍甚至10倍以上。退飽和效應導致的高漏極電壓使得器件結溫在極短的時間內迅速上升,大幅降低SiC MOSFET的短路耐受水平。器件內P基區、N-漂移區的高電場促使高空穴電流注入柵氧化層形成柵極泄漏電流,結溫溫升則進一步增大泄漏電流,造成柵氧化層退化甚至擊穿。由于焊料層與芯片熱膨脹系數不同,高溫度梯度下形成強烈的熱沖擊,產生熱切應力,導致焊料層疲勞,減少功率器件的壽命,給功率變換器的可靠運行帶來極大的挑戰[9-13]。因此,為保證SiC MOSFET器件的可靠運行,有必要對造成器件短路的故障因素及其影響規律進行詳細研究。

依據電流回路電感值將SiC MOSFET短路分為兩種故障形式:硬開關故障(Hard Switching Fault, HSF)和負載短路故障(Fault Under Load, FUL)[14-15]。HSF電流回路的電感極小,器件在開通瞬態便發生短路故障,漏-源極承受高母線電壓;FUL電流回路的電感略高,器件在進入導通狀態后形成短路,漏-源極電壓由導通壓降迅速上升至高電壓。針對SiC MOSFET的短路特性,國內外學者展開一系列研究。文獻[16-19]的分析結果表明,柵極驅動電壓決定了SiC MOSFET短路電流等級,短路電流的上升速率則與驅動參數有關。文獻[20-21]的研究結果表明,SiC MOSFET短路電流在低溫下具有正溫度系數,而在高溫下具有負溫度系數。文獻[22-23]對CREE和ROHM商業1.2kV SiC MOSFET進行短路耐受能力檢測,結果表明高母線電壓及高環境溫度下,器件在3ms短路時間內便會出現明顯的柵極泄漏電流,說明SiC MOSFET的短路耐受時間極短。

上述關于SiC MOSFET短路特性的研究是基于單個器件進行的,其短路特點在于SiC MOSFET漏源極幾乎承受全部母線電壓。然而在功率變換系統運行過程中,因硬件電路缺陷或控制失誤導致SiC MOSFET誤開通時,上、下橋臂器件將同時短路。采用半橋電路進行短路實驗時發現,短路回路中的SiC MOSFET會出現動態分壓行為,其分壓特性易受電路參數和結溫的影響。

本文首先介紹SiC MOSFET串聯短路工作特性。分別針對負載電流、驅動電壓和結溫對SiC MOSFET串聯短路分壓特性的影響規律進行理論分析。選取羅姆公司的BSM080D12P2C008 SiC MOSFET半橋模塊作為測試對象進行仿真驗證并對串聯器件耐受水平進行評估。最后通過實驗分析并驗證電路參數變化對器件損耗及結溫的影響。

1 SiC MOSFET串聯短路動態過程

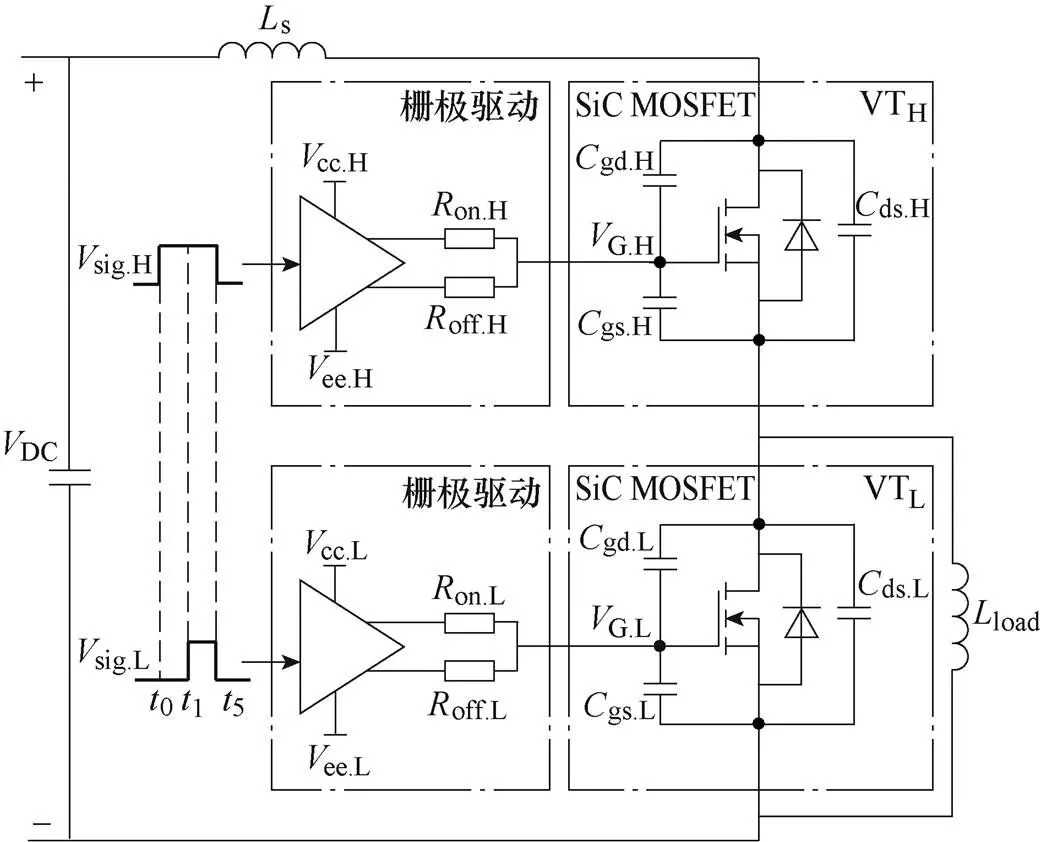

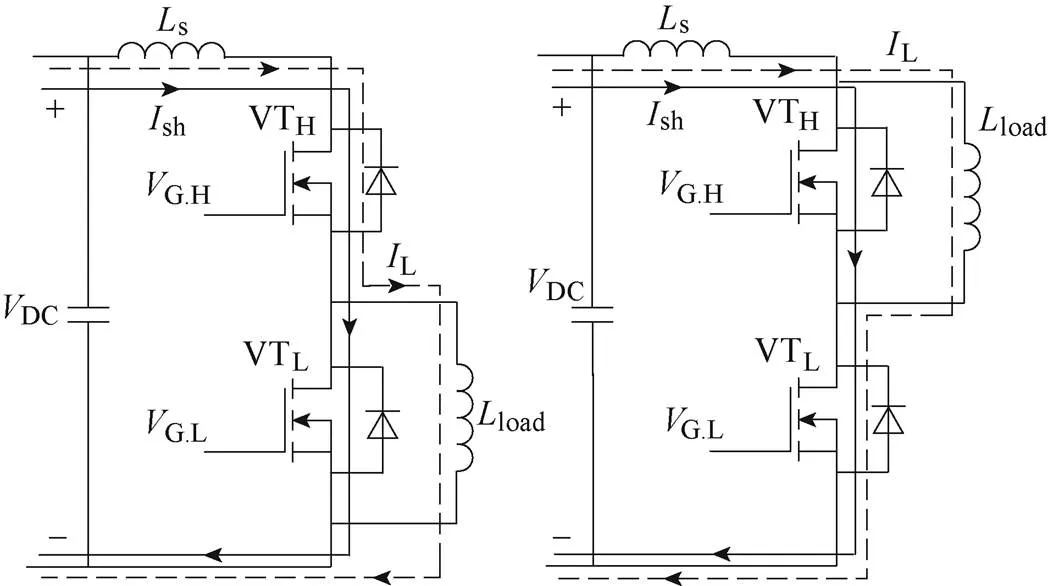

SiC MOSFET半橋串聯短路故障電路原理如圖1所示。VTH與VTL為待測SiC MOSFET器件。柵極驅動器在接受到開關信號sig.x(=H, L)后,向SiC MOSFET柵極提供正驅動電壓cc.x和負驅動電壓ee.x實現器件的開通和關斷。on.x為柵極開通電阻,off.x為柵極關斷電阻,s為等效雜散電感,DC為母線電壓,負載電感load與VTL并聯。gs.x、gd.x、ds.x為器件的結電容。

圖1 SiC MOSFET串聯短路故障電路原理

串聯短路故障的測試原理為:首先在0時刻,sig.H轉換為高電平,柵極驅動開通VTH,DC通過VTH向負載load充電,產生負載電流L。隨后在1時刻,sig.L轉換為高電平,驅動開通VTL,形成串聯短路。L的大小可通過改變0~1的時間間隔進行調節,在極短的時間間隔內L≈0A。最后在經過設定好的短路時間后,同時關斷VTH與VTL。

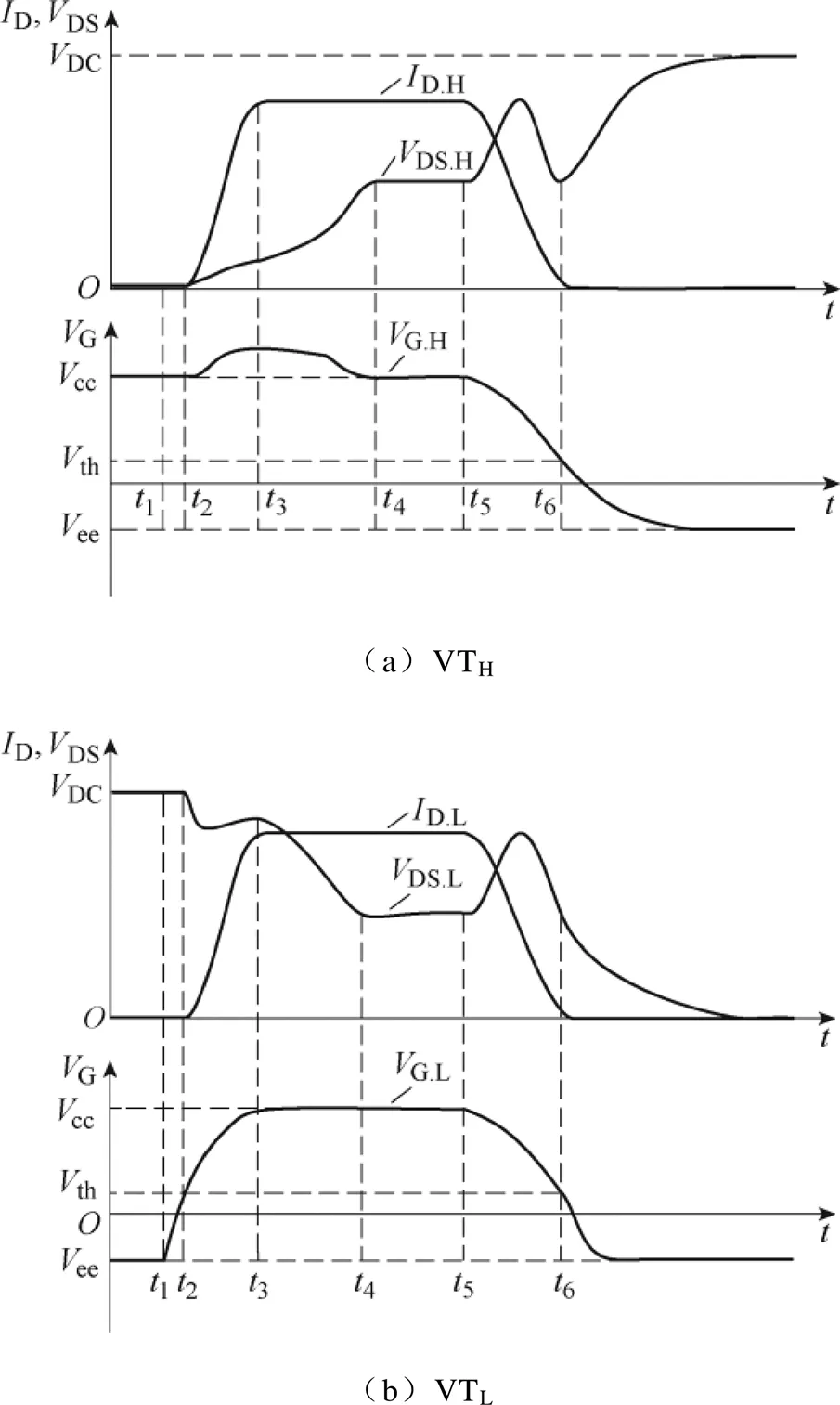

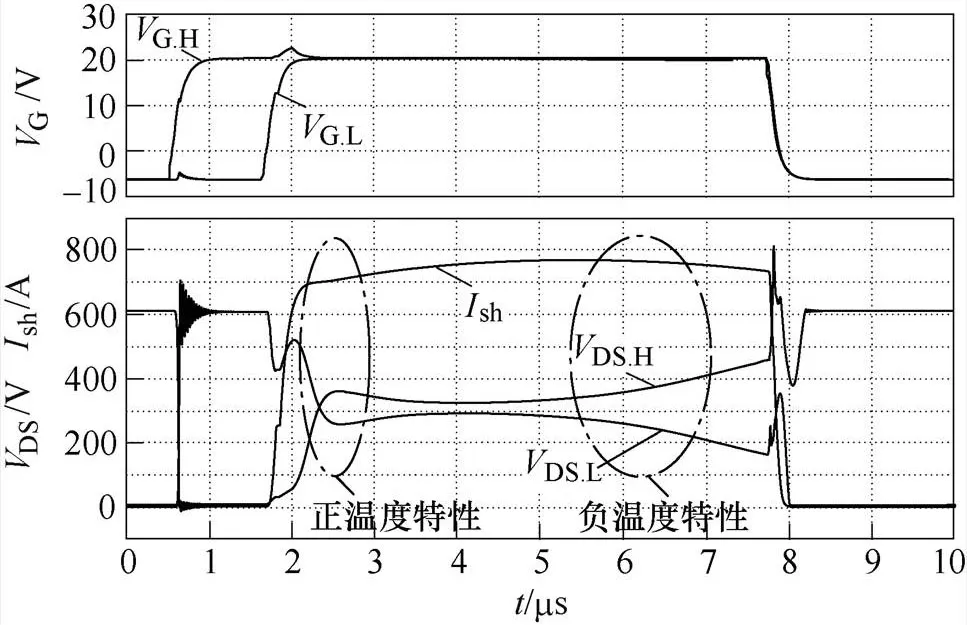

理想情況下,VTH與VTL開通時驅動參數相同,即cc.H=cc.L,on.H=on.L,off.H=off.L。VTH與VTL的短路動態過程由1時刻開始,分為四個階段,串聯短路波形示意圖如圖2所示。

圖2 串聯短路波形示意圖

1)開通延遲階段[1,2]

在1時刻,VTL的柵極電壓G.L開始上升,VTH和VTL的工作狀態保持不變。此刻,VTH為正常導通狀態,柵極電壓G.H=cc,漏極電流DS.H=L≈0A。VTL為關斷狀態,漏源極電壓DS.L=DC,漏極電流DS.L=0A。

2)電流上升階段[2,3]

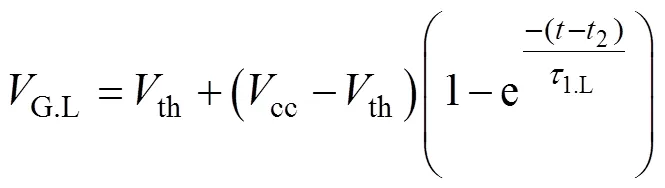

在2時刻,G.L上升至閾值電壓th,短路電流sh迅速上升,VTL的柵極電壓G.L表示為

式中,1.L為VTL柵極時間常數,1.L=on.Lgs.L。

在3時刻,G.L基本上升至cc,短路電流建立完畢。在電路理論上,該階段所建立的柵極電路模型為阻容串聯電路,其穩定時間約為3倍的柵極時間常數,即

可以看出,在外加柵極電阻和柵極電容不變的情況下,該階段時間保持不變。

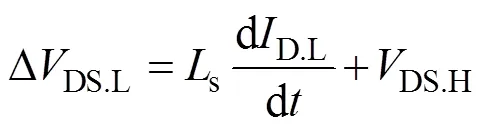

短路電流的上升使得VTH的導通壓降上升,相應的VTL漏源極電壓有所降低。受短路電流回路等效雜散電感s的影響,VTL出現電壓缺口DDS.L為

此外VTH導通壓降通過柵-漏極電容gd.H向柵極充電,導致柵極電壓G.H>cc,形成柵極過電壓尖峰DG.H,即

式中,iss.H為VTH輸入電容,iss.H=gs.H+gd.H。

3)分壓階段[3,5]

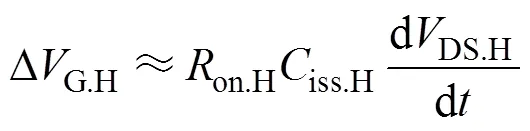

在短路電流建立后,VTH與VTL形成串聯直通,母線電壓將由這兩個器件共同承擔,VTH與VTL出現動態分壓現象。DS.H開始快速上升,相應地,DS.L開始下降,在忽略結溫溫升的理想情況下,VTH與VTL在4時刻均分母線電壓,在動態分壓的過程中,VTH的柵極通過on.H放電,最終柵極電壓尖峰DG.H消失,即

此外,在分壓過程中,VTH與VTL均承受高電壓,該階段漏極電流D.H和D.L表示為

式中,sh為短路電流;為溝道夾斷系數;ni為溝道載流子遷移速率;ch為溝道長度;ch為溝道寬度;ox為柵氧化層等效電容。

然而在實際串聯短路現象中,VTH與VTL不同短路狀態下漏極電壓差異導致損耗上升速率不同。在損耗差異的影響下,VTH與VTL的結溫出現了偏差。飽和電流受到器件結溫差異的影響而發生變化,漏極電壓也發生動態變化,分壓效果變得不穩定。

4)關斷階段[5,6]

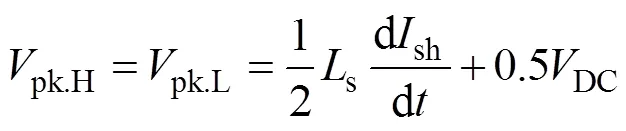

在5時刻將VTH與VTL同時關斷。短路電流sh立即下降,受雜散電感的影響,VTH與VTL的漏極電壓出現過電壓尖峰,理想狀態下,VTH過電壓尖峰pk.H與VTL過電壓尖峰pk.L一致,即

在6時刻G.H與G.L下降至閾值電壓th,短路電流降為0A。由于負載電感load與VTL并聯,DS.H上升至全母線電壓。此刻VTH與VTL已經處于關斷狀態,漏極電壓的變化速率取決于負載電感的大小,即負載電感越大,漏極電壓變化越緩。

2 SiC MOSFET串聯短路分壓特性影響因素分析

本節將分析負載電流、驅動電壓以及結溫溫升對串聯短路分壓特性的影響,建立器件分壓模型,并進行仿真分析。

2.1 負載電流IL的分壓影響

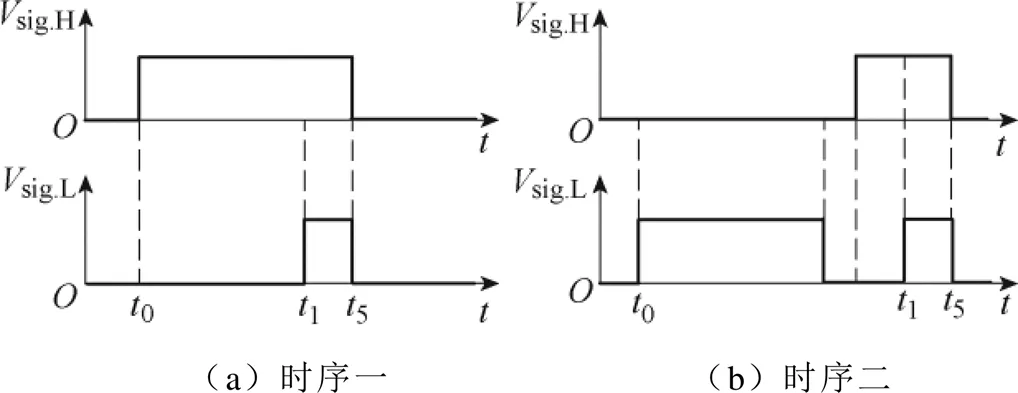

串聯短路時負載電流的存在使得流過VTH與VTL的漏極電流D.H和D.L不相等。在測試中為了產生正、反向的負載電流L,需要對VTH與VTL的開關脈沖進行調整,形成正、反向負載電流的開關時序如圖3所示。時序脈沖形成的短路電流sh與負載電流L路徑如圖4所示。

圖3 形成正、反向負載電流的開關時序

圖4 短路電流Ish與負載電流IL路徑

在圖3a所示的時序脈沖一中,延長0~1的時間使L上升,并從半橋中性端流出,設為正向電流。當L達到預定值后,再將VTL開通。在圖3b所示的時序脈沖二中,需要將負載電感與VTH并聯,如圖4b所示。首先將VTL開通,母線電壓向負載充電,L流入半橋中性端,設為反向電流。同樣延長0~1的時間,當負載電流達到預定值后,將VTL關斷,隨后將VTH開通,當VTH完全導通后,在1時刻,將VTL再次開通。有負載電流時VTH和VTL的輸出特性如圖5所示。

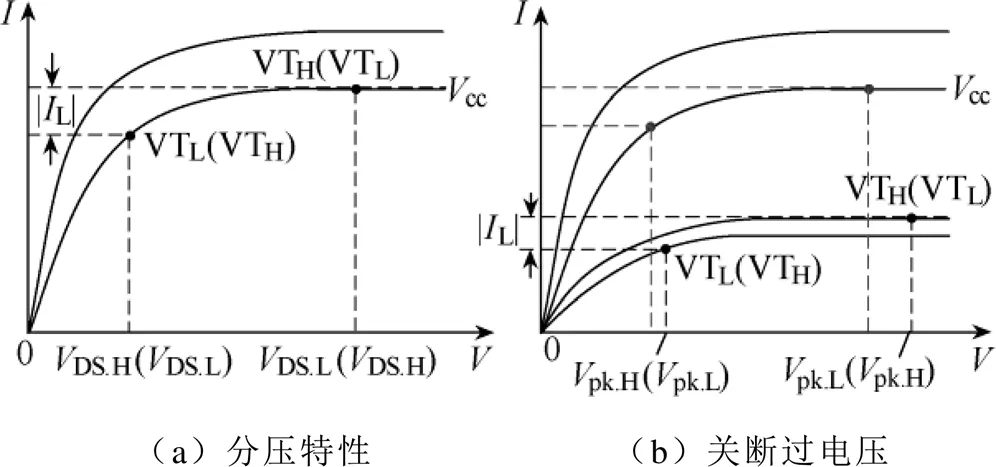

圖5 有負載電流時VTH和VTL的輸出特性

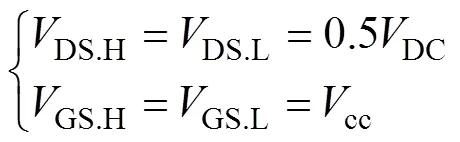

由于負載電感過高,在極短的短路過程中負載電流基本保持不變。負載電流的存在使得VTH與VTL漏極電流不同,D.H和D.L的關系為

由式(6)和式(8)計算VTH與VTL分壓穩定后DS.H與DS.L分別為

其中

由式(9)可知,當L=0A時,DS.H=DS.L=0.5DC,即VTH與VTL均分母線電壓;當L>0A時,DS.H>DS.L,即VTH承受更多的母線電壓;而當L<0A時,分壓情況正好相反。其分壓特性表現在SiC MOSFET輸出特性時如圖5a所示,在相同的柵極電壓下,漏極電流大的器件分擔更多的母線電壓,導致VTH與VTL無法均壓。隨著L的增大,不均壓程度惡化。

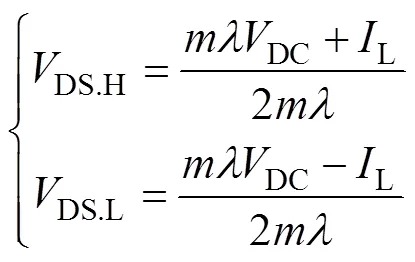

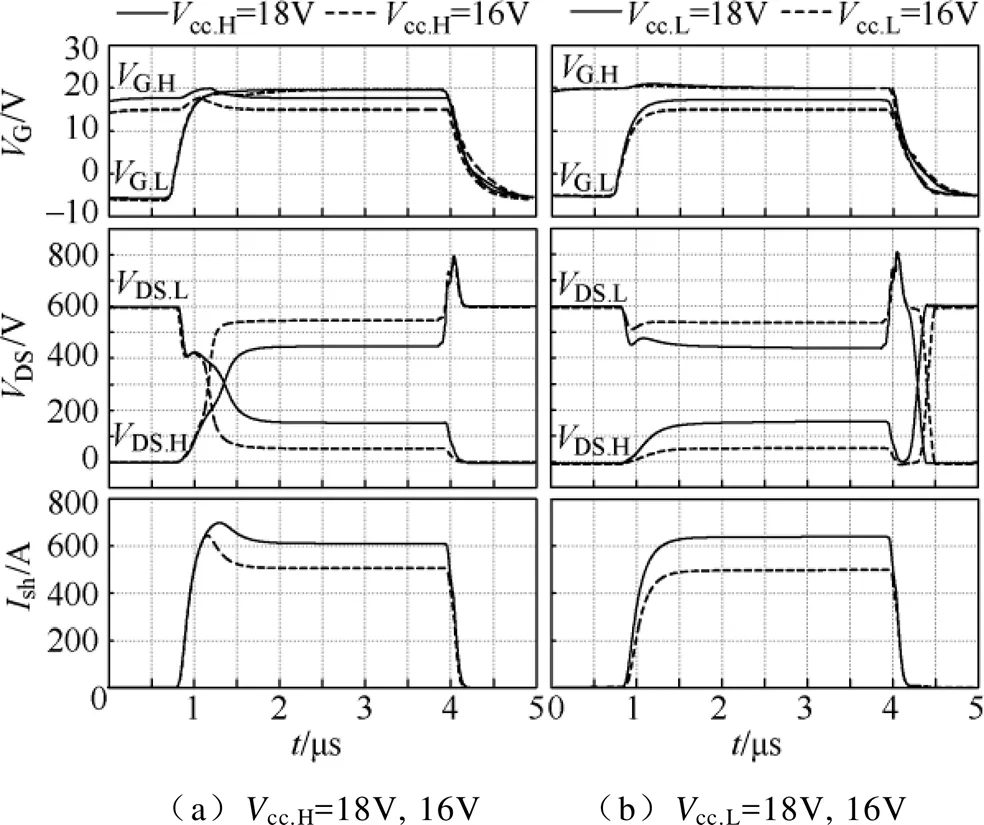

正、反向負載電流對串聯短路影響仿真波形如圖6所示。正向負載電流下SiC MOSFET串聯短路仿真波形如圖6a所示,L依次為40A、80A、160A和240A。在電流上升階段,VTL驅動參數不變,D.L上升速率不受影響。在分壓階段,D.L隨負載電流的增加而下降至sh-L,D.H基本保持sh不變,由于VTH承擔更多的母線電壓,DS.H由導通壓降上升至高于半母線電壓的過程中與DS.L出現交叉,交叉點位于半母線電壓處。在關斷過程中,隨著G.H的降低,由于D.H>D.L,VTL柵極電壓G.L下降速率快于VTH柵極電壓G.H。由圖5b可知,在電流下降過程中,VTH承擔更高的電壓尖峰。需要注意的是,當負載電流較大時,VTH過電壓尖峰會超過母線電壓,較大雜散電感下,增加了VTH過電壓擊穿的風險。

圖6 正、反向負載電流對串聯短路影響仿真波形

當L為反向電流時,VTH與VTL的分壓效果與正向電流時相反,如圖6b所示。L分別為-40A,-80A,-160A和-240A。在電流上升階段,D.L上升至sh后保持穩定,D.H則上升至sh-L。在進入分壓階段,由于D.L>D.H,VTL分擔更多的母線電壓,因而VTH與VTL漏極電壓無交叉點。在關斷過程中,G.L下降速率慢于G.H,VTL承受更高的電壓尖峰,因而在較大雜散電感下,會增加VTL過電壓擊穿的風險。

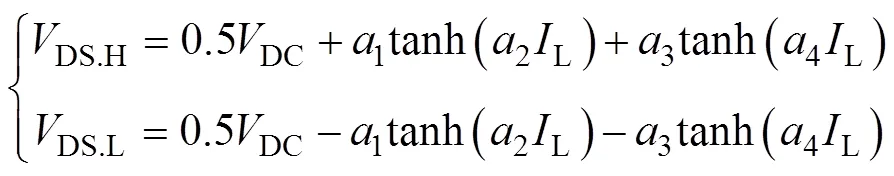

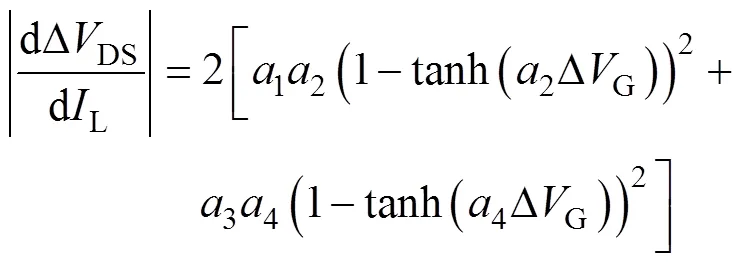

分壓階段DS.H和DS.L受負載電流影響曲線如圖7所示。變化趨勢呈雙曲正切函數,擬合曲線可設為

式中,1~4為擬合系數,在本文仿真條件下,1= 135,2=0.006,3=80,4=0.02。

設VTH與VTL的漏極電壓差DDS為

則DVDS隨負載電流IL的變化速率為

圖7所示的DDS的變化表明,在發生串聯短路時,VTH與VTL的分壓特性對負載電流的敏感度較高。

在功率變換系統中,由于負載電流多為正弦變化,當發生串聯短路時,VTH與VTL無法均壓,其中一個器件會分擔更多的母線電壓,在負載電流過高時,該器件將承受絕大部分母線電壓。

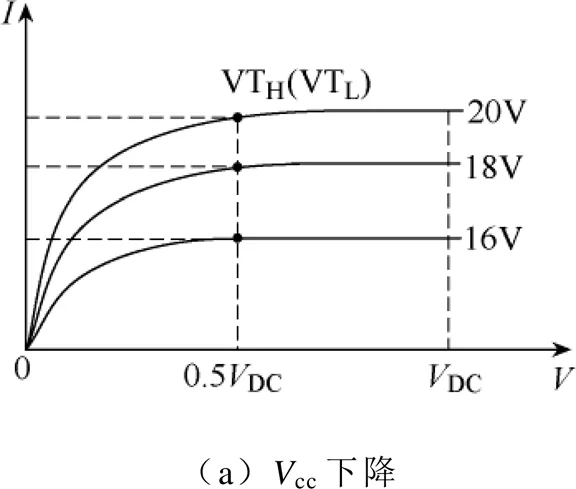

2.2 驅動電壓Vcc.x的分壓影響

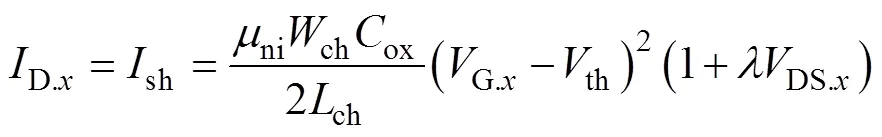

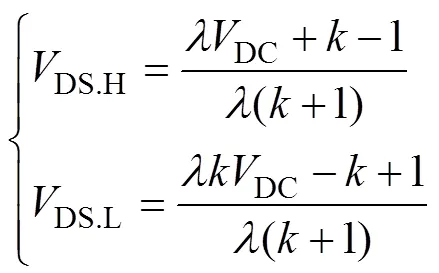

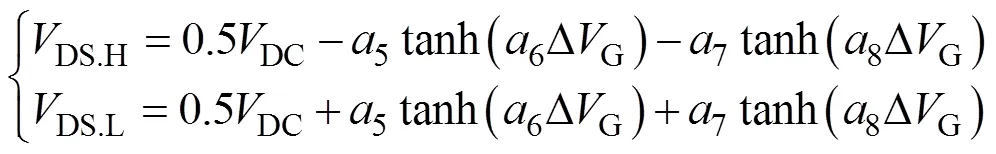

SiC MOSFET的飽和電流由柵極電壓決定,因而在驅動電壓降低時,短路電流隨之減小。當VTH與VTL出現驅動電壓差異時,同樣會影響串聯短路分壓特性。將式(6)中的G.x分別用cc.H和cc.L代替,計算出VTH與VTL的漏極電壓分別為

其中

由式(13)可知,當同時降低VTH與VTL驅動電壓并保證驅動電壓一致時,=1,DS.H=DS.L= 0.5DC;當僅降低cc.H時,<1,DS.H分擔更多的母線電壓;而僅降低cc.L時,>1,DS.L分擔更多的母線電壓。

驅動電壓變化下VTH與VTL輸出特性如圖8所示,在驅動電壓cc下降時,由圖8a可知,sh會隨之降低,但因cc.H=cc.L,VTH與VTL仍會保持均壓狀態。當VTH與VTL驅動電壓不一致時,由圖8b可知,柵極電壓較小的器件決定了sh的大小,并分擔較多的母線電壓。隨著驅動電壓差DG(DG=G.H-G.L)的增大,VTH與VTL不均壓程度將惡化。

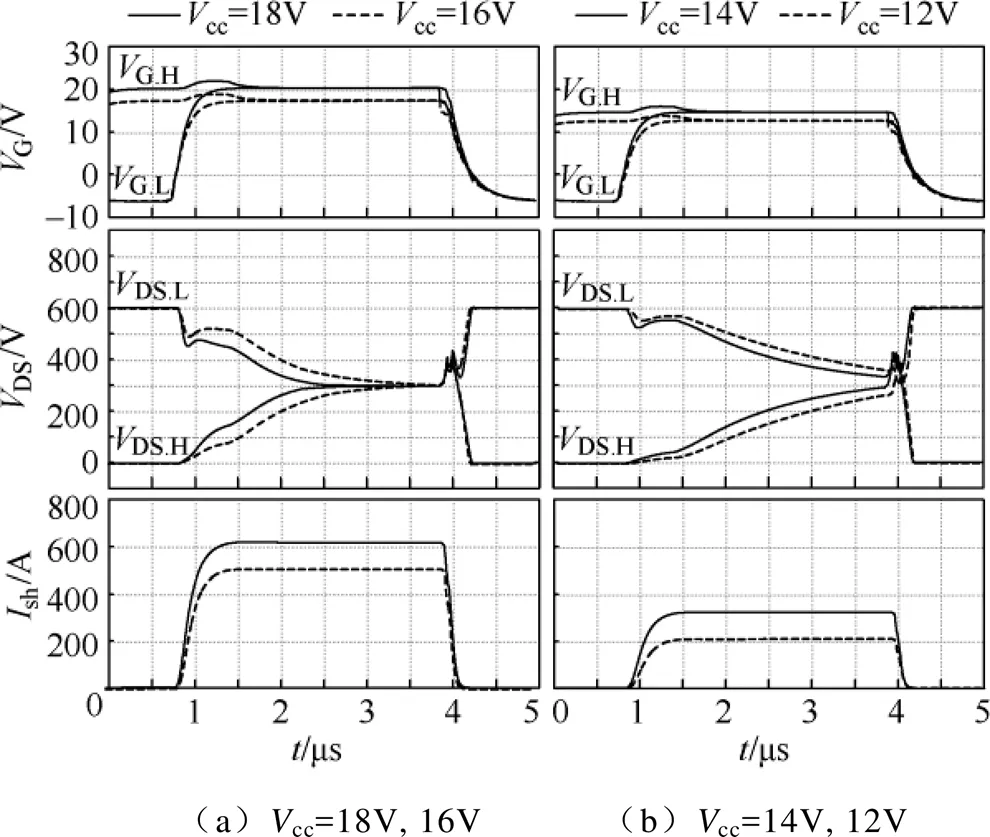

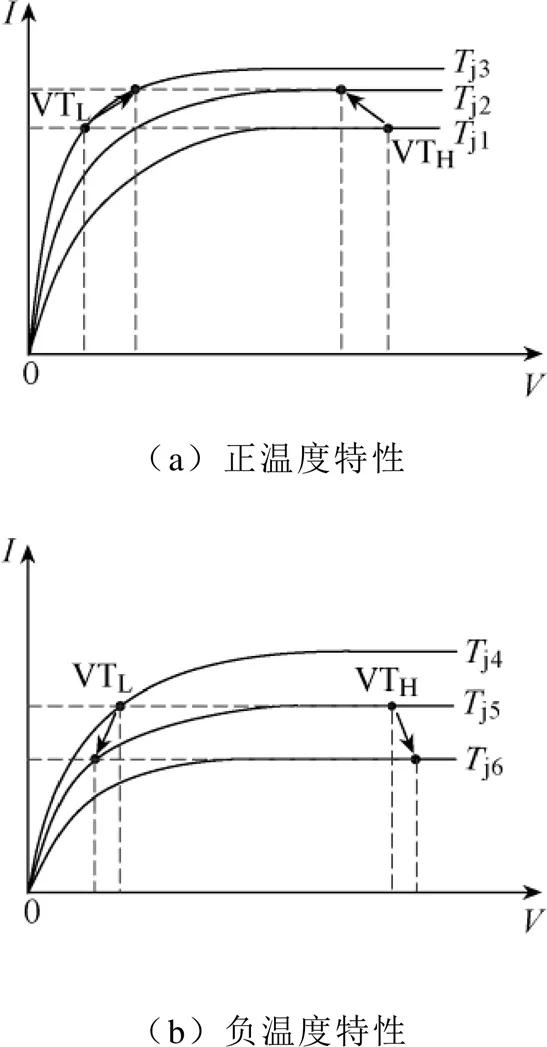

圖9為驅動電壓cc對串聯短路影響仿真波形。cc依次設為18V、16V、14V和12V。由于VTL的柵極時間常數不變,cc的減小不會影響電流上升階段的時長,但因柵極電壓上升減緩,漏極電流與電壓變化速率降低。sh上升速率的減小,使得雜散電感s的感應電動勢與VTH導通壓降下降,VTL的電壓缺口有所減小。在分壓階段,漏極電壓變化速率的減緩,導致VTH與VTL達到半母線電壓的時刻向后推遲。在分壓結束后,VTH與VTL仍會保持均壓狀態,但若驅動電壓過低,即當cc=12V或10V時,分壓完成時刻超過短路時間,VTH與VTL還沒有完成分壓,短路便已結束。

圖9 驅動電壓Vcc對串聯短路影響仿真波形

cc.H與cc.L對串聯短路影響仿真波形如圖10所示。cc.H依次設為18V和16V,cc.L保持為20V。由于cc.H<cc.L,sh受到cc.H的抑制而減小。在電流上升階段,VTH柵極過電壓尖峰暫時提高了最大飽和電流,形成短路電流尖峰,隨后在分壓階段,短路電流迅速下降,VTH將分擔更多的母線電壓,導致VTH與VTL的漏極電壓出現交叉。此外在關斷過程中,VTH將承受過高的過電壓尖峰,甚至超過了母線電壓,在高雜散電感下增加了VTH過電壓擊穿的風險。

圖10 Vcc.H與Vcc.L對串聯短路影響仿真波形

降低驅動電壓cc.L至18V和16V,cc.H保持為20V時,sh受cc.L的抑制,其分壓特性與降低cc.H時正好相反。由于cc.L<cc.H,VTL將始終分擔較多的母線電壓,因而VTH與VTL漏極電壓無交叉點。同樣在關斷過程中,VTL產生過高的過電壓尖峰,在高雜散電感下增加了VTL過電壓擊穿的風險。

VTH與VTL的漏極電壓隨驅動電壓差DG的變化曲線如圖11所示,DS.H和DS.L與DG呈雙曲線函數關系,其擬合曲線設為

式中,5~8為擬合系數,在本文仿真條件下,5= 146,6=0.4,7=142,8=2.8。

VTH與VTL漏極電壓差DDS隨柵極電壓差DG的變化速率表示為

圖11 驅動電壓差DVG與VDS.x關系曲線

隨著DG的增大,DDS增加幅度逐漸減小。同時在DG較小的情況下,DG略微增加都會導致VTH與VTL嚴重的分壓不均。該曲線說明串聯短路時VTH和VTL的分壓特性對驅動電壓差有較高的敏 感度。

2.3 結溫Tj的分壓影響

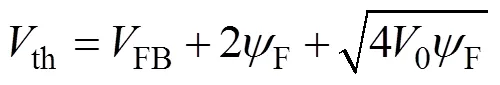

上述分析在不考慮結溫溫升的理想條件下進行,有利于展現電路參數對串聯短路分壓特性的影響。然而實際串聯短路過程中,高電壓大電流產生的耗散功率在數ms內全部加在芯片上,導致結溫j迅速上升,改變器件的工作特性。溫度影響短路特性的主要因素為閾值電壓th和溝道遷移率ni的溫度相關性。閾值電壓th的表達式為

式中,FB為平帶電壓;0為常數,由半導體中摻雜質量分數和氧化層厚度決定;F為費米勢,是半導體禁帶中間能級和費米能級之間的電勢差,隨著溫度的升高,費米能級逐漸向禁帶中線靠攏,導致形成反型層所需能帶彎曲表面勢2F降低,因而th具有負溫度特性。

對于N型SiC MOSFET,溝道自由電子在運輸過程中受到體晶格散射、聲光子散射、表面粗糙度散射和庫倫散射的影響[12],形成四種不同的載流子遷移率。其中庫倫散射形成的載流子遷移率具有正溫度系數,聲子散射形成的載流子遷移率具有負溫度系數。在短路初期,j較低,溝道載流子遷移率主要受庫倫散射的影響。由式(6)可知,低溫下ni與th的溫度效應共同導致短路電流增大,此時SiC MOSFET呈正溫度特性。隨著j的繼續上升,聲子散射所占的比重增加,弱化了庫倫散射正溫度效應,短路電流上升幅度減小甚至開始下降,SiC MOSFET轉為負溫度特性。

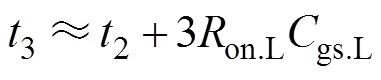

由圖12所示的正、負溫度效應下輸出特性曲線可知,當器件呈正溫度特性時,sh由結溫較低的器件決定,該器件承受較高的母線電壓,但隨著VTH與VTL結溫同時上升,器件分壓不均程度減弱。當器件呈負溫度特性時,sh由結溫較高的器件決定,該器件承受較高的母線電壓,且隨著器件結溫的上升,器件分壓不均程度惡化。

圖12 正、負溫度效應下輸出特性曲線(Tj1<Tj2<Tj3<Tj4<Tj5<Tj6

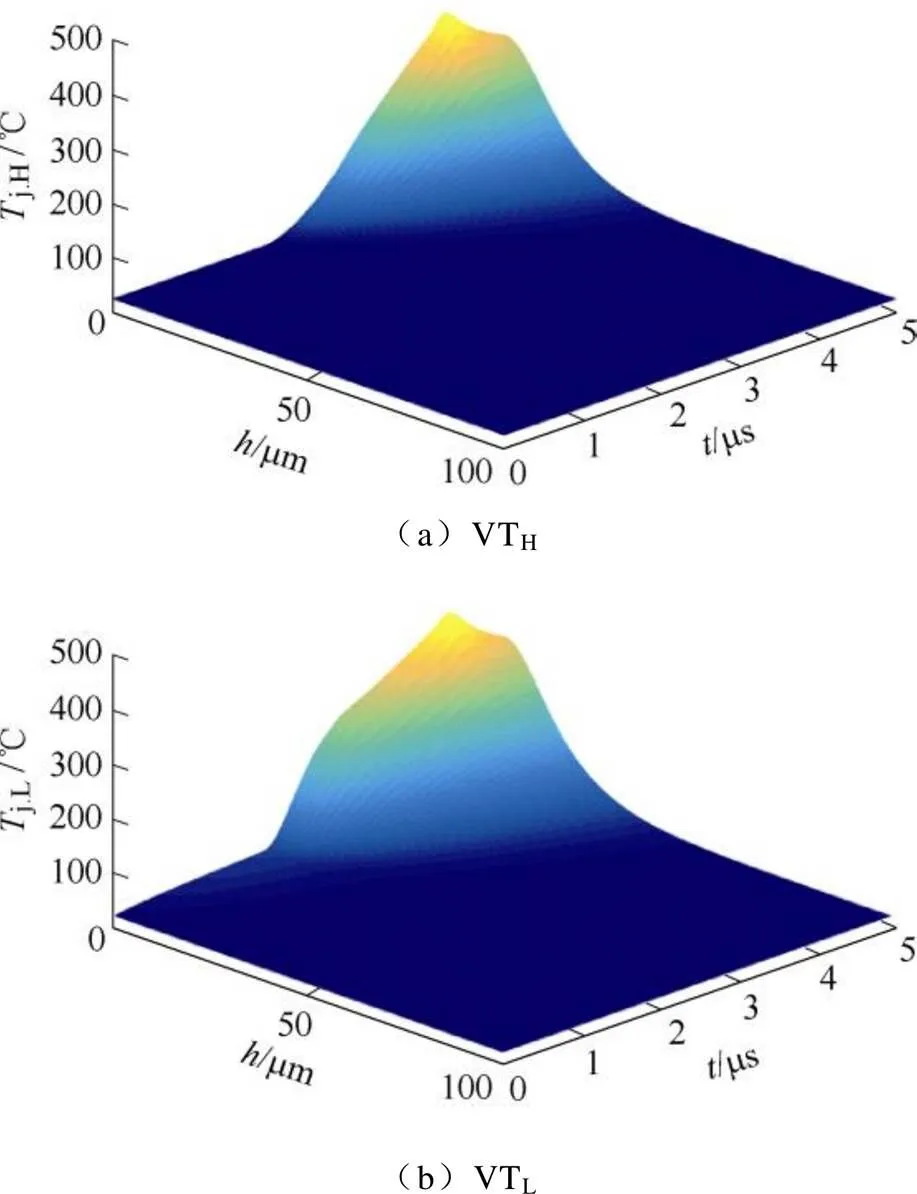

結溫j對串聯短路影響仿真波形如圖13所示,在電流上升階段,受漏極電壓的主要影響,VTH與VTL的結溫出現偏差,使得器件載流子遷移速率不同。在結溫較低時,sh呈正溫度系數。由于電流上升階段VTL承受絕大部分母線電壓,VTH的結溫j.H小于VTL的結溫j.L,因而短路電流由VTH決定。在進入分壓階段,由于j.H<j.L,VTL承擔較少的母線電壓,VTH與VTL漏極電壓到達交叉點后,DS.L將繼續下降。隨后,由于DS.L<DS.H,VTH與VTL的結溫差Dj(Dj=|j.H-j.L|)開始縮小,DS.H與DS.L在達到波峰或波谷之后向半母線電壓合攏。

隨著短路時間的推移,當結溫較高時,sh逐漸趨向于負溫度特性,短路電流隨著溫升由上升轉為下降狀態,VTH與VTL的漏極電壓發生反向變化,仿真中DS.H上升,DS.L逐漸減小,進一步擴大了器件的結溫差。若短路時間繼續增加,DS.H承受大部分母線電壓,且因結溫過高產生的泄漏電流對器件造成嚴重的損傷。

圖13 結溫Tj對串聯短路影響仿真波形

3 SiC MOSFET串聯短路耐受水平分析

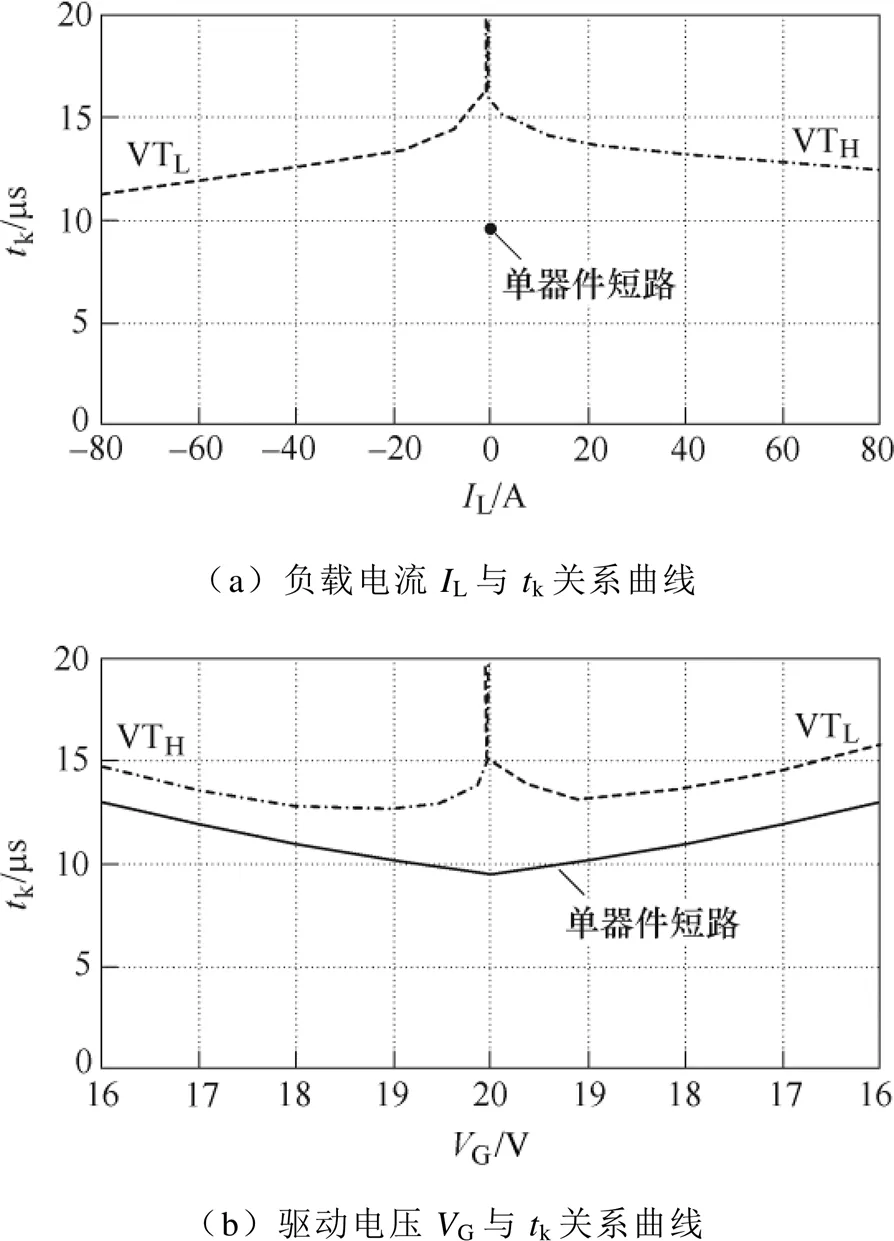

在研究SiC MOSFET單器件的短路特性時,由于待測器件承受全母線電壓,大短路電流下,結溫極速上升,待測器件在極短的時間內達到臨界溫度,表現出低短路耐受水平。相對于SiC MOSFET串聯短路特性,由第2節的分析可知,VTH與VTL敏感的分壓特性會使串聯短路損耗被分解,減緩了結溫溫升。由于在不同初始條件即負載電流或驅動電壓下,串聯器件的動態分壓變化較大,導致短路耐受水平呈現出不固定性。通常當短路器件結溫上升至1 000℃左右時可能對該器件造成損傷[22],因而本文以j=1 000℃為結溫節點作為評價短路耐受水平參考值,在不同初始條件下,k為VTH與VTL上升至該節點的短路時間,初始條件對串聯短路器件耐受水平影響如圖14所示。

受短路電流負溫度特性的影響,VTH與VTL僅有其中一個能夠達到該結溫節點。在L=0A,cc.H=cc.L=20V的條件下,VTH達到了該結溫,短路時間為15.2ms,高于相同驅動條件下單器件短路仿真結果的9.6ms,主要原因在于短路初期VTH與VTL較好的均壓效果減緩了結溫的溫升,從而提高了器件的短路耐受時間。在圖14a中,隨著負載電流正向增加,短路時間有所減小,在L=80A時,k降至12.4ms。而當負載電流為反向電流時,結溫節點轉移至VTL,短路時間同樣隨著負載電流反向增加而減小,在L=-80A時,k降至11.2ms。當改變驅動電壓時,在圖14b中,結溫節點出現在驅動電壓較小的器件上。當VTL與VTH驅動電壓差|DG|<1V時,短路前期均壓效果變差導致k有所降低,而隨著|DG|持續增大,短路電流大幅降低,k反向上升。與圖中實線所示單器件驅動電壓降低的短路仿真結果相比,串聯器件的短路時間仍然較長,主要原因在于,驅動電壓較高的器件承受數十伏的導通電壓,在一定程度上分擔了短路損耗。

圖14 初始條件對串聯短路器件耐受水平影響

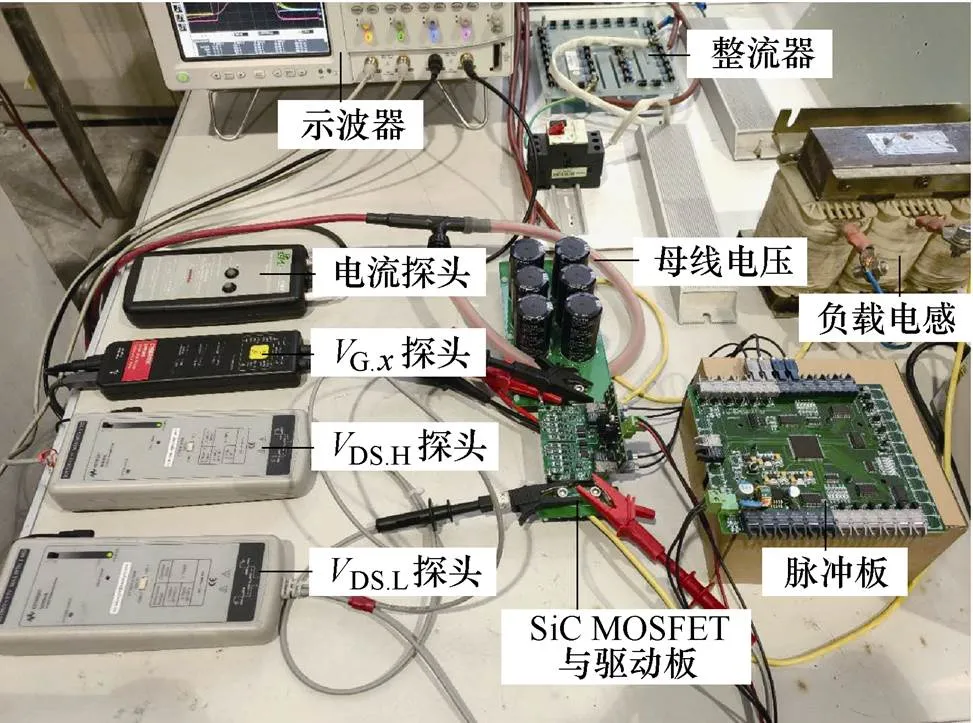

4 實驗驗證

搭建SiC MOSFET串聯短路實驗平臺如圖15所示,采用SiC MOSFET半橋模塊BSM080D12P2C008為實驗對象,實驗初始條件為cc.x=20V,ee.x=-5V,on.x=10W,off.x=20W,DC=600V,load=300mH。

圖15 SiC MOSFET串聯短路實驗平臺

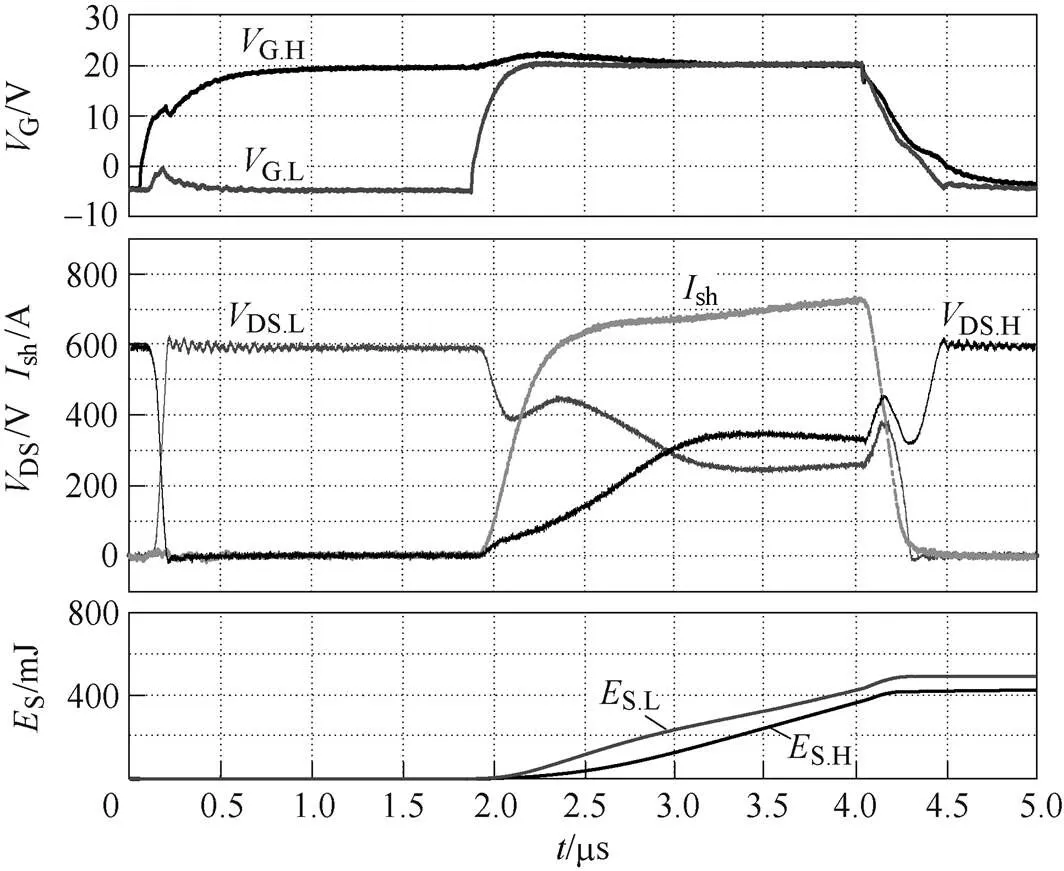

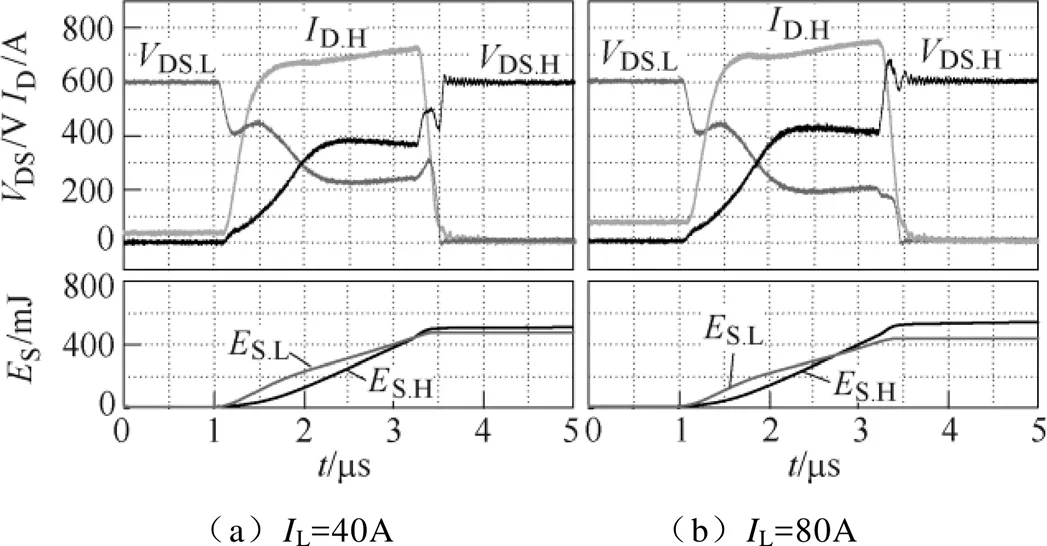

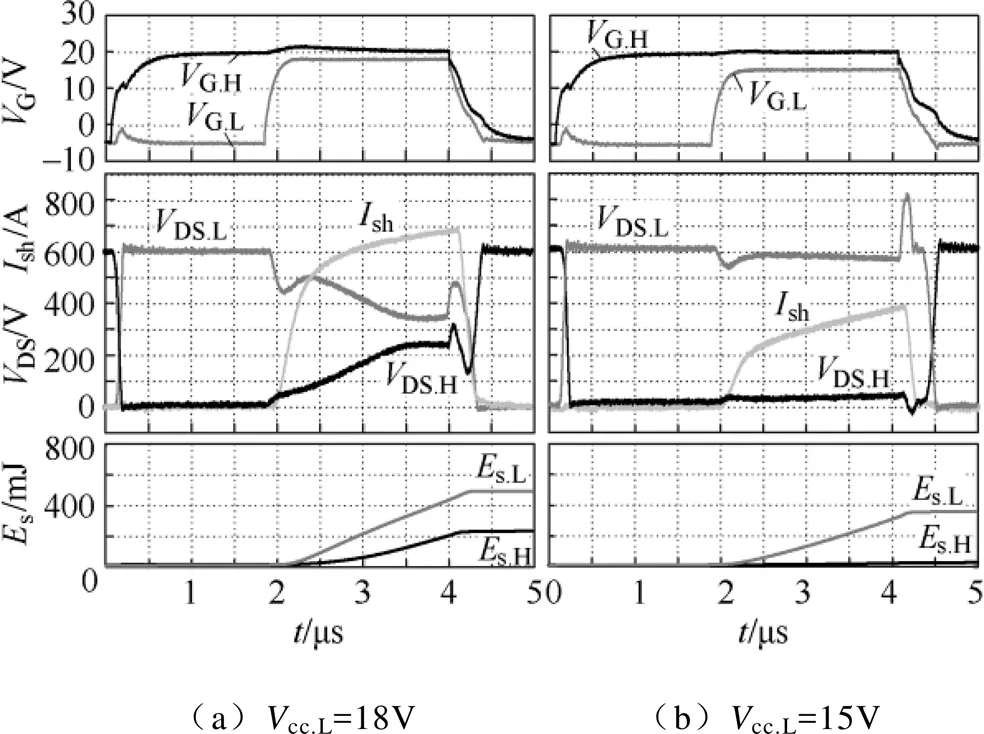

為了保護SiC MOSFET模塊不被損壞且可重復使用,將短路檢測時間設置為2ms。利用FPGA脈沖分配板產生時序脈沖控制SiC MOSFET的開通與關斷。SiC MOSFET串聯短路實驗波形如圖16所示。短路電流上升至680A后進入分壓階段,受VTH與VTL正溫度特性影響,短路電流隨著短路持續時間的增加而緩慢上升。在短路初期DS.L>DS.H,VTL短路損耗S.L上升速率較高。在短路故障發生約1ms時,DS.H與DS.L出現交叉點,隨后DS.L<DS.H,S.L上升速率將小于VTH短路損耗S.H上升速率,結溫溫差逐漸縮小。在短路故障發生1.4ms時,DS.L降到波谷240V,相應地,DS.H上升至波峰360V。由于結溫差的縮小,VTH與VTL的漏極電壓開始朝半母線電壓合攏。最終在關斷后,S.H和S.L分別為430mJ和490mJ。

圖16 SiC MOSFET串聯短路實驗波形

在短路運行過程中,器件很難通過實驗直接測得結溫的瞬態變化。為了分析串聯短路器件結溫溫升特性,采用文獻[22]的基于傳熱學非穩態熱傳導原理,建立關于SiC MOSFET芯片的熱電模型。通過熱電模型的計算,VTH與VTL內部結構縱向結溫分布如圖17所示,圖中,為SiC MOSFET耗盡層縱向分布,參考零點為P基區與N-漂移區的PN結,P基區耗盡層距離零點為負值,N-漂移區耗盡層距離零點為正值。整個短路期間,待測器件的溫度分布非常集中,溫度最高值一直處于PN結附近,此處電場強度最大,對應的熱激勵密度最高,因而將該處的溫度作為待測器件的結溫。隨著的增加,器件溫度急劇下降,當>60mm時,熱傳導過程幾乎可以忽略。

圖17 內部結構縱向結溫分布

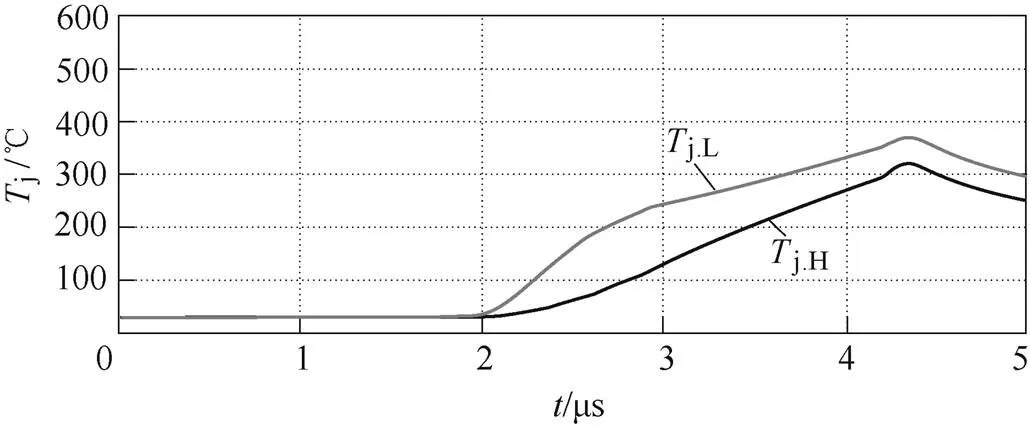

VTH與VTL計算結溫隨時間的變化曲線如圖18所示。在器件關斷后,j.H和j.L分別為324℃和378℃,結溫差Dj=54℃。相對于對單個功率器件的短路實驗,VTH和VTL的分壓特性大幅降低了器件的結溫溫升,因而在常規的短路保護時間內器件受到的短路沖擊大幅減小。

圖18 VTH和VTL的計算結溫溫升

4.1 負載電流IL的實驗影響

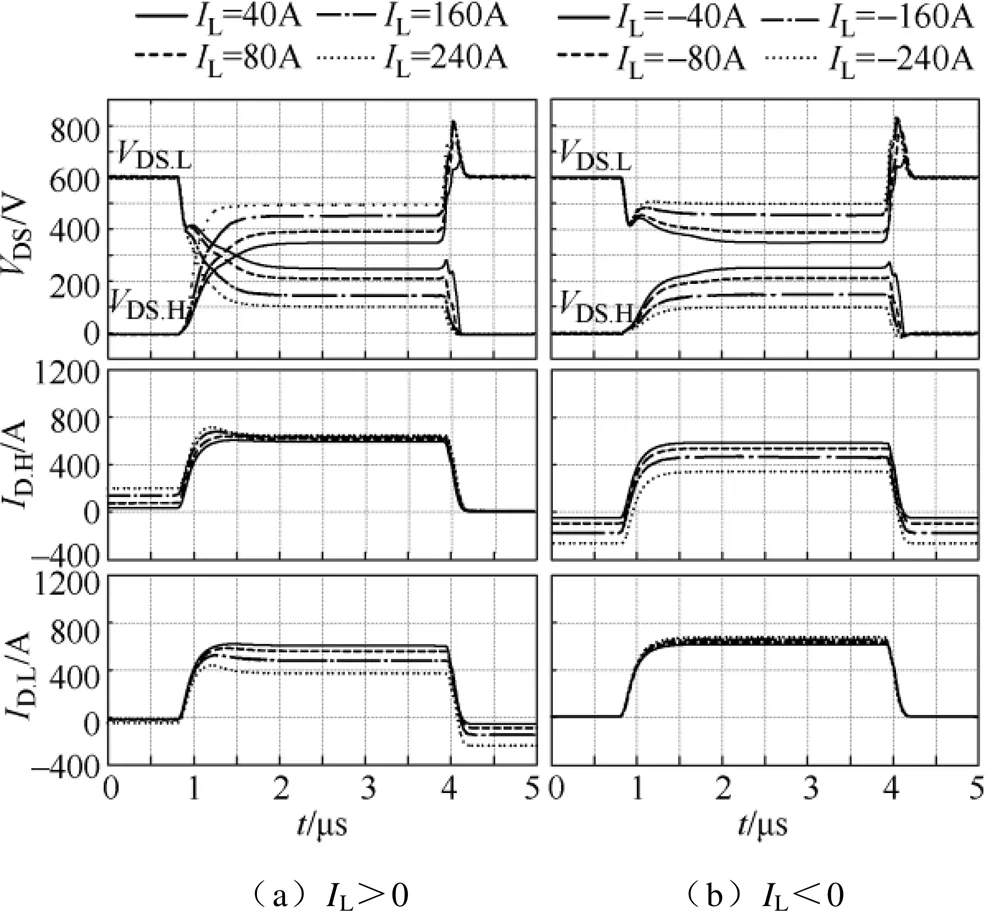

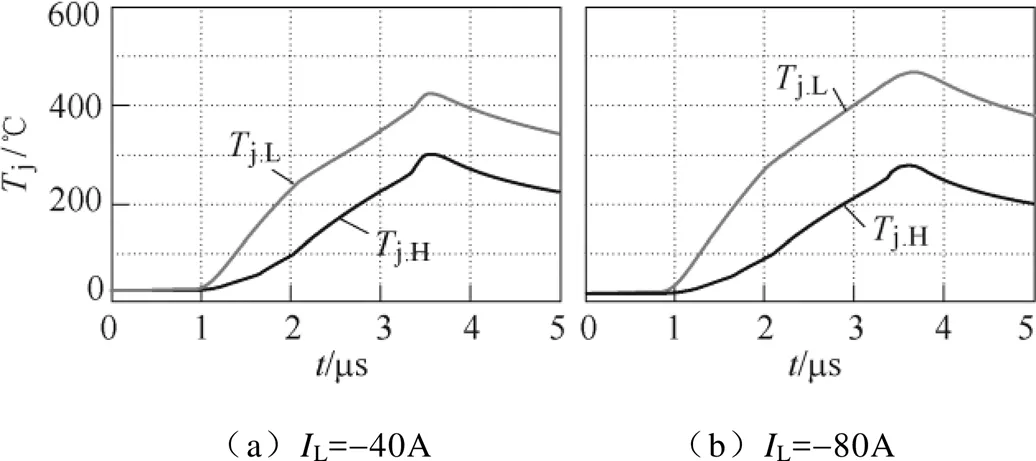

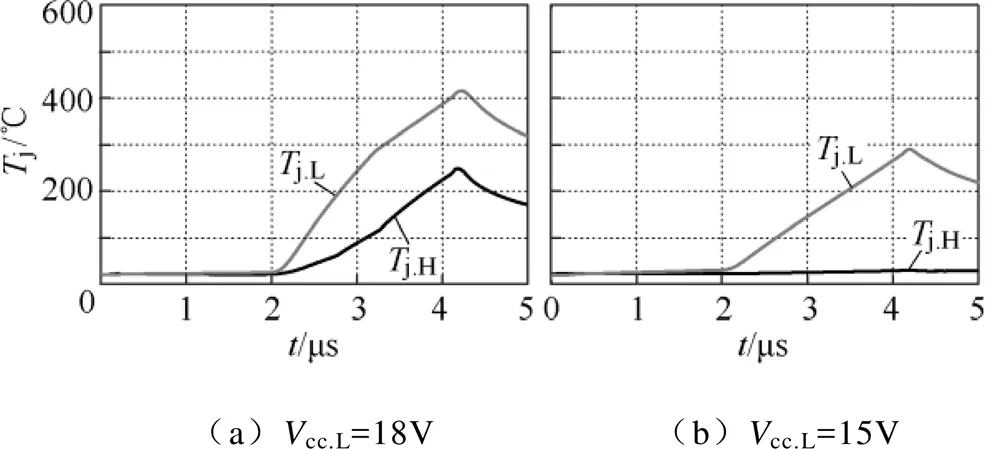

正向負載電流L對串聯短路影響的實驗波形如圖19所示,實驗選取負載電流絕對值為40A和80A。與圖16的L=0A進行比較,當負載為正向電流時,VTH承擔更多的母線電壓,與理論分析一致。在分壓過程中,DS.L的下降導致S.L上升速率減小,相應地,S.H上升速率增大。當L=40A時,S.L降低至473mJ,略小于S.H的505mJ,此時DS很小。正向負載電流L對串聯短路結溫影響計算波形如圖20所示。從圖20可知,VTH與VTL的結溫差Dj較小,在關斷時刻j.H與j.L分別為382℃和364℃。而當L=80A時,S.L進一步降低至431mJ,S.H則上升至533mJ,導致Dj增大,由圖20可得,在關斷時刻j.H與j.L分別為407℃和322℃,Dj上升至85℃。

圖19 正向負載電流IL對串聯短路影響的實驗波形

圖20 正向負載電流IL對串聯短路結溫影響計算波形

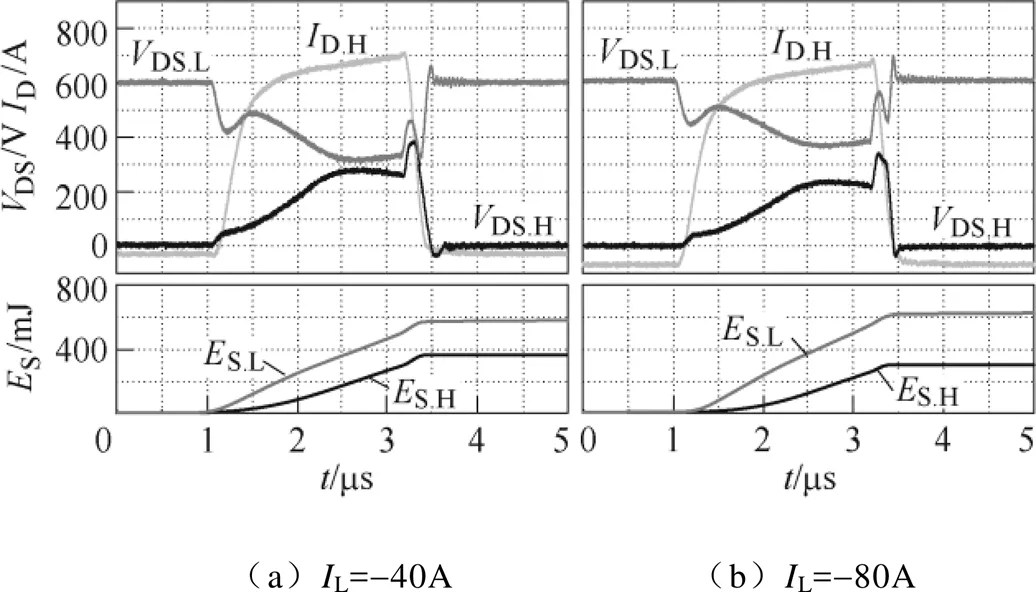

當負載流過反向電流時,反向負載電流對串聯短路影響的實驗波形如圖21所示,VTH與VTL漏極電壓變化幅度減小,因而無交叉點,與理論分析一致。由于VTL的漏極電壓與漏極電流都高于VTH,導致S.L上升速率始終高于S.H。當L=-40A時,S.L增大至583mJ,則S.H減小至372mJ,DS大幅增加。反向負載電流L對串聯短路結溫影響的計算波形如圖22所示。從圖22可知,在關斷時刻j.H與j.L分別為304℃和435℃,Dj增大至131℃。當L=-80A時,S.L進一步上升至610mJ,S.H減小至290mJ,在圖22中,j.L上升至472℃,j.H下降至276℃,Dj進一步增大至204℃。

由上述分析可以看出,反向負載電流導致VTH與VTL損耗不均恒性要比正向負載電流嚴重,且VTL的結溫遠高于VTH,VTL因結溫過高,短路耐受能力將大幅減弱。

圖21 反向負載電流對串聯短路影響的實驗波形

圖22 反向負載電流IL對串聯短路結溫影響的計算波形

4.2 驅動電壓Vcc的實驗影響

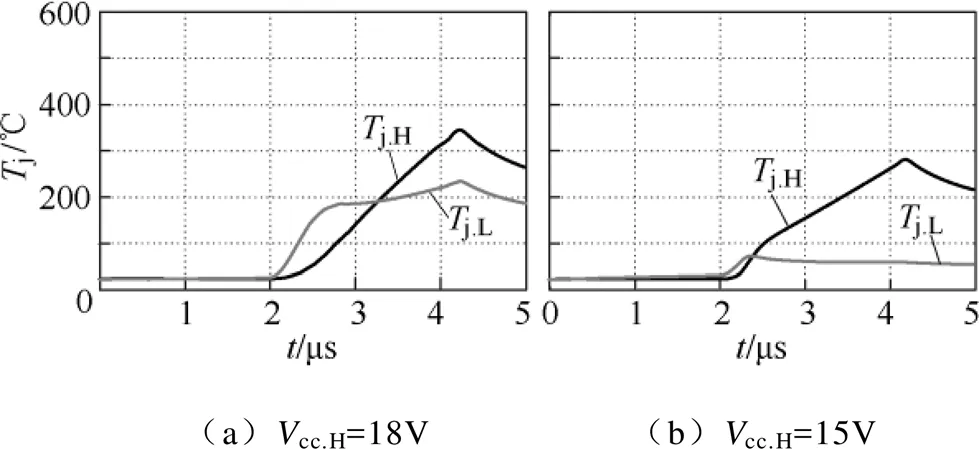

圖23為同時降低VTH與VTL驅動電壓cc的實驗波形。選取cc為18V和15V進行實驗。與圖16的cc=20V進行比較,驅動電壓的下降使得短路電流明顯減小。當cc=18V時,短路電流sh下降了約100A。sh上升速率降低導致VTL電壓缺口和VTH導通壓降減小,在電流上升階段,S.L上升速率有所提高。而在分壓階段,由于sh的減小,VTH與VTL損耗上升速率減緩,S.H和S.L的損耗分別下降至365mJ和412mJ。當cc=15V時,sh下降了約360A,S.H和S.L大幅降低至171mJ和213mJ。驅動電壓cc對串聯短路結溫影響的計算波形如圖24所示。由圖24可以看出,短路電流的大幅下降,導致了VTH與VTL的結溫溫升大幅降低,當cc=18V時,j.H與j.L分別下降至293℃和315℃;當cc=15V時,j.H與j.L的結溫進一步降至156℃和172℃。且Dj在逐漸減小。

若VTH與VTL驅動電壓不同,首先降低VTH驅動電壓cc.H,選取cc.H為18V和15V,驅動電壓cc.H對串聯短路影響的實驗波形如圖25所示。與圖16的cc.H=20V進行比較,cc.H的降低使VTH與VTL漏極電壓變化幅度大幅增加。當cc.H=18V時,sh以及DS.L的下降,使得S.L大幅下降至330mJ。S.H則由于DS.H的上升與sh的下降相互抵消而略微上升至450mJ。當cc.H=15V時,VTH承受了絕大部分母線電壓,在短路電流大幅減小的影響下,S.L極小,S.H則下降至380mJ。若進一步降低cc.H,S.H將因短路電流的下降進一步降低,而S.L的變化忽略不計。通過熱電模型計算的驅動電壓cc.H對串聯短路結溫影響的計算波形如圖26所示。sh和DS.L的降低導致j.L大幅下降,當cc.H=18V時,j.H略微上升至354℃,在進入分壓階段后,j.L上升速率明顯變緩,最終降為242℃,Dj增大至112℃。當cc.H=15V時,由于短路電流的大幅下降,j.H下降至301℃,而j.L在電流上升階段略微升高后,在進入分壓階段,由于漏極電壓急速下降,結溫上升非常緩慢,并受溫度傳導特性的影響開始緩慢下降,最終j.L降至約50℃,Dj進一步增大至287℃。

圖23 驅動電壓Vcc對串聯短路影響的實驗波形

圖24 驅動電壓Vcc對串聯短路結溫影響的計算波形

當僅降低VTL驅動電壓cc.L時,驅動電壓cc.L對串聯短路影響的實驗波形如圖27所示。選取cc.L為18V和15V進行實驗。與圖16的cc.L=20V進行比較,由于VTL開通速率減緩,VTH與VTL的分壓過程變得十分緩慢,VTL承受了較多的母線電壓,增大了器件的損耗差。當cc.L=18V時,短路電流的下降以及VTH分壓的減小使得S.H的損耗大幅下降至240mJ,VTL則因漏極電壓的上升而增加至550mJ。當cc.L=15V時,VTL幾乎承受了全部的母線電壓,由于短路電流大幅減小,S.L下降至380mJ,S.H的變化忽略不計。VTH與VTL的結溫溫升如圖28所示。cc.L的降低大幅減小了VTH的結溫,當cc.L=18V時,j.L上升至417℃,j.H上升速率明顯變緩,最終結溫降為259℃,Dj增大至158℃。當cc.L=15V時,j.L下降至297℃,而j.H溫升忽略不計。

圖25 驅動電壓Vcc.H對串聯短路影響的實驗波形

圖26 驅動電壓Vcc.H對串聯短路結溫影響的計算波形

圖27 驅動電壓Vcc.L對串聯短路影響的實驗波形

圖28 驅動電壓Vcc.L對串聯短路結溫影響的計算波形

由上述分析可以看出,驅動電壓差的增大,會加劇器件結溫不平衡分布,但短路電流的降低減小了短路損耗與結溫溫升,降低了短路故障對器件的沖擊。

5 結論

本文以SiC MOSFET半橋模塊為研究對象,對發生串聯短路時SiC MOSFET的分壓特性進行詳細分析。區別于單一器件短路時承受全母線電壓,串聯短路時上、下橋臂器件共同分擔母線電壓。建立串聯短路分壓模型,結合仿真詳細分析負載電流、驅動電壓和結溫溫升對短路分壓特性的影響,結合實驗分析電路參數對短路器件損耗與結溫的影響。理論分析、仿真和實驗結果表明,器件串聯短路特性尤其是分壓特性極易受外部電路參數的影響,反向負載電流、驅動電壓差的增加會造成上、下橋臂器件結溫不平衡,影響器件的可靠性。

[1] 周林, 李寒江, 解寶, 等. SiC MOSFET的Saber建模及其在光伏并網逆變器中的應用和分析[J]. 電工技術學報, 2019, 34(20): 4251-4263.

Zhou Lin, Li Hanjiang, Xie Bao, et al. Saber modeling of SiC MOSFET and its application and analysis in photovoltaic grid-connected inverter[J]. Transactions of China Electrotechnical Society, 2019, 34(20): 4251-4263.

[2] She Xu, Huang A Q, óscar L, et al. Review of silicon carbide power devices and their applications[J]. IEEE Transactions on Industrial Electronics, 2017, 64(10): 8193-8205.

[3] 盛況, 郭清, 張軍明, 等.碳化硅電力電子器件在電力系統的應用展望[J]. 中國電機工程學報, 2012, 32(30): 1-7.

Sheng Kuang, Guo Qing, Zhang Junming, et al. Development and prospect of SiC power devices in power grid[J]. Proceedings of the CSEE, 2012, 32(30): 1-7.

[4] Laird I, Yuan Xibo, Scoltock J, et al. A design optimization tool for maximizing the power density of 3-phase DC-AC converters using silicon carbide (SiC) devices[J]. IEEE Transactions on Power Electronics, 2019, 33(4): 2913-2932.

[5] 莊桂元, 張興, 劉威, 等. 帶飛跨電容的三電平拓撲中SiC MOSFET過電壓與過電流保護[J]. 電工技術學報, 2021, 36(2): 341-351.

Zhuang Guiyuan, Zhang Xing, Liu Wei, et al. Over- voltage and overcurrent protection of SiC MOSFET in three-level topology with flying capacitor[J]. Transa- ctions of China Electrotechnical Society, 2021, 36(2): 341-351.

[6] 陳杰, 鄧二平, 趙子軒, 等. 不同老化試驗方法下SiC MOSFET失效機理分析[J]. 電工技術學報, 2020, 35(24): 5105-5114.

Chen Jie, Deng Erping, Zhao Zixuan, et al. Failure mechanism analysis of SiC MOSFET under different aging test methods[J]. Transactions of China Electro- technical Society, 2020, 35(24): 5105-5114.

[7] 王莉娜, 馬浩博, 袁愷, 等. SiC MOSFET半橋電路開關瞬態過電流、過電壓建模與影響因素分析[J]. 電工技術學報, 2020, 35(17): 3652-3665.

Wang Lina, Ma Haobo, Yuan Kai, et al. Modeling and influencing factor analysis of SiC MOSFET half- bridge circuit switching transient overcurrent and overvoltage[J]. Transactions of China Electrotechnical Society, 2020, 35(17): 3652-3665.

[8] 李輝, 黃樟堅, 廖興林, 等. 一種抑制SiC MOSFET橋臂串擾的改進門極驅動設計[J]. 電工技術學報, 2019, 34(2): 275-285.

Li Hui, Huang Zhangjian, Liao Xinglin, et al. An improved SiC MOSFET gate driver design for crosstalk suppression in a phase-leg configuration[J]. Transactions of China Electrotechnical Society, 2019, 34(2): 275-285.

[9] Zhou Xintian, Su Hongyuan, Wang Yan. Investiga- tions on the degradation of 1.2kV 4H-SiC MOSFETs under repetitive short-circuit tests[J]. IEEE Transa- ctions on Electronic Devices, 2016, 63(11): 4346- 4351.

[10] Reigosa P D, Luo Haoze, Francesco I. Implications of ageing through power cycling on the short circuit robustness of 1.2kV SiC MOSFETs[J]. IEEE Transa- ctions on Power Electronics, 2019, 34(11): 11182- 11190.

[11] Nguyen T, Ahmed A, Thang T V, et al. Gate oxide reliability issues of SiC MOSFETs under short-circuit operation[J]. IEEE Transactions on Power Electronics, 2015, 30(5): 2445-2455.

[12] Zhou Yuming, Liu Hangzhi, Mu Shilu, et al. Short- circuit failure model of SiC MOSFET including the interface trapped charges[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 90-98.

[13] Sun Jiahui, Wei Jin, Zheng Zheyang, et al. Short circuit capability and short sircuit inducedthinstabi- lity of a 1.2kV SiC power MOSFET[J]. IEEE Journal of Emerging and Selected Topics in Power Elec- tronics, 2019, 7(3): 1539-1546.

[14] Ji Shiqi, Marko L, Huang Xingxuan, et al. Short circuit characterization and protection of 10kV SiC MOSFET[J]. IEEE Transactions on Power Electronics, 2019, 34(2): 1755-1767.

[15] 吳海富, 張建忠, 趙進, 等. SiC MOSFET短路檢測與保護研究綜述[J]. 電工技術學報, 2019, 34(21): 4519-4528.

Wu Haifu, Zhang Jianzhong, Zhao Jin, et al. Review of short-circuit detection and protection of silicon carbide MOSFETs[J]. Transactions of China Electro- technical Society, 2019, 34(21): 4519-4528.

[16] 王占擴, 童朝南, 黃偉超. SiC MOSFET短路特性及過流保護研究[J]. 中國電機工程學報, 2020, 40(18): 5751-5760.

Wang Zhankuo, Tong Chaonan, Huang Weichao. Reasearch on short-circuit characteristics and over- current protection of SiC MOSFET[J]. Proceedings of the CSEE, 2020, 40(18): 5751-5760.

[17] 高勇, 喬小可, 孟昭亮, 等. SiC MOSFET的短路特性[J]. 半導體技術, 2019, 44(5): 342-348.

Gao Yong, Qiao Xiaoke, Meng Zhaoliang, et al. Short-circuit characteristics of SiC MOSFETs[J]. Semiconductor Technology, 2019, 44(5): 342-348.

[18] Sadik D P, Colmenares J, Tolstoy G, et al. Short- circuit protection circuits for silicon-carbide power transistors[J]. IEEE Transactions on Industrial Elec- tronics, 2016, 63(4): 1995-2004.

[19] Wang Jun, Jiang Xi, Li Zongjian, et al. Short-circuit ruggedness and failure mechanisms of Si/SiC hybrid switch[J]. IEEE Transactions on Power Electronics, 2019, 34(3): 2771-2780.

[20] 秦海鴻, 徐克峰, 王丹, 等. SiC MOSFET短路特性[J]. 南京航空航天大學學報, 2018, 50(3): 348-354.

Qin Haihong, Xu Kefeng, Wang Dan, et al. Short-circuit characteristics of SiC MOSFETs[J]. Journal of Nanjing University of Aeronautics & Astronautics, 2018, 50(3): 348-354.

[21] Eni E P, B?czkowski S, Munk-Nielsen S, et al. Short- circuit degradation of 10kV 10A SiC MOSFET[J]. IEEE Transactions on Power Electronics, 2017, 32(12): 9342-9354.

[22] Wang Zhiqiang, Shi Xiaojie, Tolbert L M, et al. Temperature-dependent short-circuit capability of silicon carbide power MOSFETs[J]. IEEE Transa- ctions on Power Electronics, 2016, 31(2): 1555-1566.

[23] Kadavelugu A, Aeloiza E, Belcastro C. Short-circuit performance of multi-chip SiC MOSFET modules[C]// IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, 2017: 285- 290.

Dynamic Characterization Assessment on Series Short-Circuit of SiC MOSFET

(School of Electrical and Power Engineering China University of Mining and Technology Xuzhou 221116 China)

In power electronic systems, when SiC MOSFET is turned on incorrectly due to breakdown devices, hardware circuit defects or system control errors, at least two devices work in the short-circuit current loop, forming series short-circuit faults. Based on the half-bridge structure, the switching principle of SiC MOSFETs in short-circuit was introduced in detail. To study the influence mechanism of load current, gate drive voltage and junction temperature, the short circuit test was carried out under different experimental situations. The drain-source voltage sharing model of SiC MOSFET was derived and verified by simulation. The changes of short-circuit loss and junction temperature distribution caused by circuit parameters were compared on the 1 200V/80A SiC MOSFET experimental bench. The results show that the dynamic characteristics of SiC MOSFET are highly sensitive to circuit parameters in series short-circuit. The unbalanced dynamic change of drain-source voltage and drain current affect the short-circuit loss of devices, which in turn changes the junction temperature distribution.

SiC MOSFET, series short-circuit, voltage dividing characteristic, junction tem- perature distribution

TM46

10.19595/j.cnki.1000-6753.tces.201432

國家重點研發計劃子課題資助項目(2016YFC0600804)。

2020-11-01

2021-02-02

張經緯 男,1991年生,博士研究生,研究方向為SiC器件特性分析與驅動設計。E-mail: tb19130011b4@cumt.edu.cn

譚國俊 男,1962年生,教授,博士生導師,研究方向為電力電子與電力傳動。E-mail: gjtan_cumt@163.com(通信作者)

(編輯 陳 誠)