基于Verilog 的有限狀態機編程方式及研究

(西安電子科技大學微電子學院,陜西西安 710126)

0 引言

Verilog HDL[1]是一種常用的硬件描述語言,可以從系統級、電路級、門級到開關級對電路進行設計和驗證工作。采用Verilog HDL設計電路并進行仿真實驗,具有方便快捷的特點。

有限狀態機FSM(Finite State Machine)的基本結構由狀態寄存器和組合邏輯電路組成,通過對觸發器輸入端輸入信號,并由狀態寄存器對狀態完成保持或轉換,最后通過組合電路完成特定的輸出。分為以下兩種情況:

(1)Moore型有限狀態機:輸出的信號只與當前狀態有關。(2)Mealy型有限狀態機:輸出信號不僅與當前狀態有關,而且與輸入信號有關。

傳統的狀態機設計方法需要繁瑣的狀態分配、繪制狀態表、化簡次態方程等步驟[2],而使用Verilog語言可以大大簡化這一過程。

1 有限狀態機的設計流程

有限狀態機處于工作狀態時,內部的狀態寄存器保持現有狀態。

根據工作原理,將有限狀態機的設計分為以下幾個步驟[3]:

(1)確定采用Moore型狀態機還是Mealy型狀態機。(2)列出狀態機的所有狀態,并對每一個狀態進行狀態編碼。(3)根據狀態轉移關系畫出狀態圖。(4)采用硬件描述語言對狀態機進行描述。

每一步的選擇都會導致編程風格的不一樣,更會導致有限狀態機性能上各方面的差異。

2 有限狀態機的狀態編碼選擇

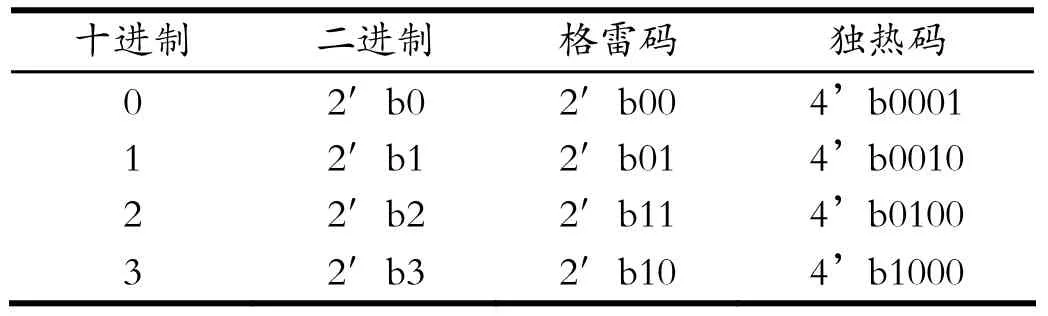

狀態編碼確定維持狀態所需的觸發器的數量并影響實現下一個狀態和輸出時所用的組合邏輯的復雜度[4]。Verilog中常用的狀態編碼方式有二進制碼,格雷(Gray)碼和獨熱(One-hot)碼,如表1所示:

表1 Verilog 的常用狀態編碼方式Tab.1 Verilog's common state encoding methods

通過比較,可以發現二進制編碼和格雷碼所用的狀態向量最短。但對于二進制編碼,在狀態寄存器進行狀態轉換時,如果狀態從2’b2翻轉到2’b3即從2’b01至2’b10這樣會產生多個狀態的翻轉。而格雷碼在變化時,實現了僅一位的改變,這樣,格雷碼在實際應用中減少了電路相鄰物理信號線同時變化的情況,從而減少電路中的電噪聲[5],若使用獨熱碼,則X 個狀態就需要X 個狀態寄存器,這將使狀態轉換過程更加嚴謹,并且電路的容錯性將更好。盡管使用了更多的觸發器。但是由于狀態解碼簡單,可以減少組合邏輯[6]。因此,獨熱碼常常在硬件資源豐富的情況下使用。

3 有限狀態機的編程方式及其優缺點

通過分析有限狀態機的工作方式,可以得到單進程式,雙進程式和三進程式三種編程方法。

這幾種編程方式的優缺點主要從電路的毛刺、延遲、面積、功耗及速度等方面進行考量。毛刺的產生[7]一方面由于狀態機中的組合邏輯對時鐘邊沿信號的影響,另一方面由于狀態向量通過多條電路傳輸,形成競爭;延遲存在于當前信號改變到下一級電路信號改變時中間經歷的時間,延遲的疊加會導致電路的不靈敏;面積和速度不能同時優化,有時為了速度需要犧牲面積。

3.1 單進程式描述方式

單進程式描述方式只有一個always過程塊。這種情況下,如果均采用非阻塞語句賦值,電路不會產生毛刺。由于一段式的描述方法是為STATE本身分配一個值,因此會引入一個周期的延時,在設計中需要通過“預計算”將其考慮在內[8]。如果遇到狀態較多的情況,編程本身極易出錯,且代碼冗長,因此,在任何情況下,都不推薦單進程式編程。

3.2 雙進程式描述方式

雙進程式描述方式有兩個always過程塊。第一個過程塊描述了狀態的轉移,第二個過程塊描述了由輸入確定的當前狀態以及組合邏輯控制的輸出。這種方式使編譯器優化效果明顯,可以獲得非常理想的速度和資源占用率,是目前使用最廣泛的狀態機描述風格[9]。

3.3 三進程式描述方式

三進程式描述方式有三個always過程塊。它由當前狀態及輸入確定下一級狀態,將對輸出的選擇用單獨的一個always過程塊描述,從而將組合邏輯電路分離開,使電路不會產生毛刺,可靠性高,并且代碼條理清晰,更易維護。

4 實例

用有限狀態機實現簡易“110”序列檢測器,要求避免毛刺、冗余現象,有較快速度。

4.1 狀態選擇

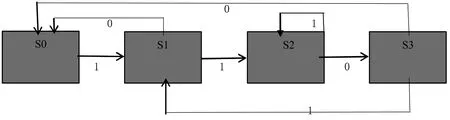

采用Moore型狀態機,即輸出的信號只與當前狀態有關。確定狀態轉移圖如圖1 所示:

圖1 “110”序列檢測器的狀態轉移圖Fig.1 State transition diagram of "110" sequence detector

4.2 編碼選擇

因為要實現簡易狀態機,故選擇向量長度較短的編碼方式,故考慮二進制碼和格雷碼這兩種編碼方式。因為格雷碼降低了冗余,故選用格雷碼進行編碼。

4.3 編程風格選擇

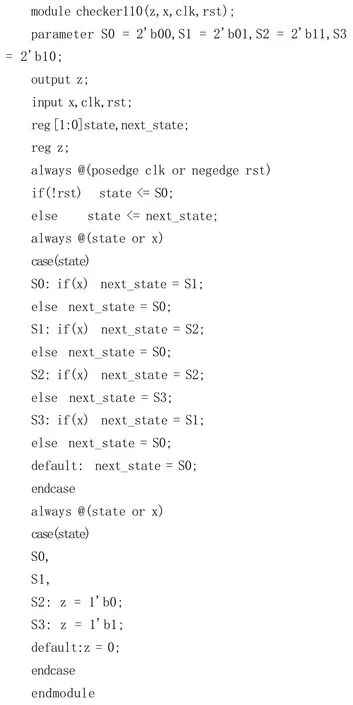

由于要求較快速度,則應通過寄存器進行輸出,故選用三段式編程方式,這里是犧牲面積,減小延遲,提高速度。

4.4 條件語句選擇

選用case語句不需要考慮優先級且編程簡潔方便,不會產生鎖存器。

4.5 編寫程序

4.6 仿真結果

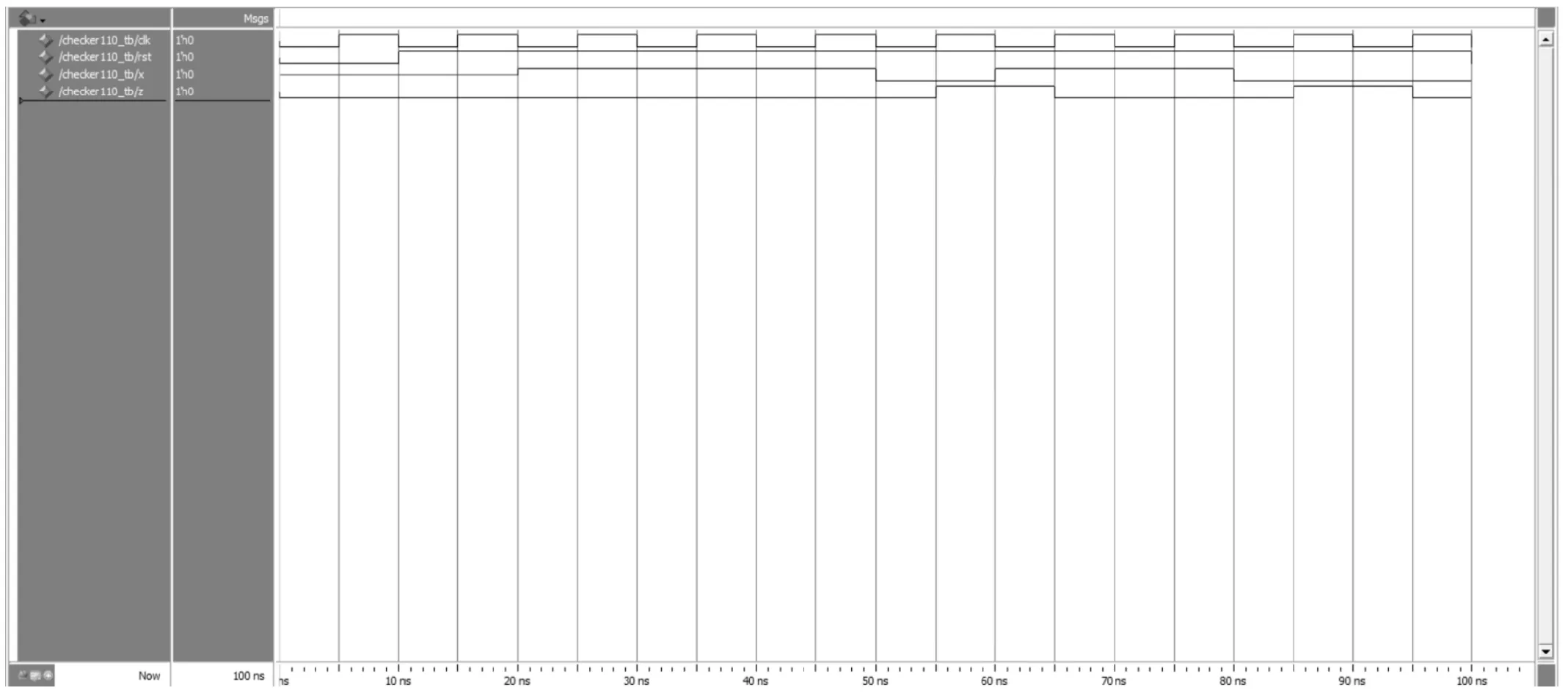

本例通過ModelSim SE 10.6d進行仿真。前10ns對有限狀態機實現復位功能,清除上一次運行結果,在第10ns拉高復位信號,啟動有限狀態機。之后每過10ns對有限狀態機輸入一個有效信號x,分別為1、1、1、0、1、1、0作為測試序列。通過仿真可以發現,在第一個零(50ns)以及第二個零(80ns)出現之后的時鐘沿輸出1。運行100ns后,仿真結果如圖2所示:

圖2 ModelSim 仿真結果Fig.2 ModelSim simulation results

5 結語

有限狀態機在集成電路設計中有著重要的作用,選用Verilog 語言進行編程有著方便、簡潔等特點。利用Verilog語言編寫有限狀態機時,編碼的選擇、編程方式的選取均會影響到有限狀態機的性能。對于精確度要求較高的電路可以選用格雷碼或者獨熱碼。編程方式盡量選擇二進程式或者三進程式。編寫條件語句時,要注意清除鎖存器。