美國國防部可信微電子戰(zhàn)略和舉措演進研究

張 倩,劉馨陽,聶國健,周軍連

(工業(yè)和信息化部電子第五研究所,廣東廣州 510610)

為保障武器裝備用微電子器件的安全,美國國防部自2003 年起逐步建立起“可信供應”能力。隨著微電子器件產(chǎn)品供應鏈的持續(xù)全球化和先進制造能力不斷向亞洲聚集,美國國防部要求加大對商用技術和產(chǎn)品的使用力度,并于2017 年提出“技術實現(xiàn)可信”的新安全框架[1]。2020 年5 月,美國國防部國防研究和現(xiàn)代化工程主任馬克·路易斯表示,國防部將采取“零信任”方式購買微電子器件產(chǎn)品,即假設所購產(chǎn)品均不安全,必須通過驗證后才可使用,并表示已經(jīng)研制出達到該目標的技術[2]。通過分析新安全框架及其所匹配項目的研究成果,可以證實美國國防部已打下了良好的可信技術保障能力。

1 美國國防部一直擔心微電子器件的安全和持續(xù)供應

美國武器裝備用邏輯電路只有約10% 來自國防部的定制化制造,其他則依賴商用現(xiàn)貨(Commercial-off-the-shelf,COTS)[3]。在供應鏈全球化的背景下,微電子器件在裝入武器裝備前可能會被倒手十余次[4],而且亞洲掌握著最先進的微電子制造和封測能力,美國非常擔心武器裝備用微電子器件在制造和流轉(zhuǎn)過程中的安全,具體體現(xiàn)在以下四個方面:

敏感信息丟失。通過潛入設計和制造環(huán)節(jié)或?qū)嵤┠嫦蚬こ痰仁侄危杀I取微電子器件產(chǎn)品中的敏感或關鍵信息、知識產(chǎn)權(Intellectual Property,IP)等,還可了解器件結構和功能,以及發(fā)現(xiàn)漏洞,為后續(xù)功能復制或發(fā)起攻擊做好準備。

植入惡意功能。通過修改微電子器件規(guī)格、設計和掩膜版等手段,可植入缺陷或硬件木馬,使系統(tǒng)性能降低甚至失效,或獲取系統(tǒng)訪問和控制權,進而實施攻擊。2011 年7 月,美國國土安全部在給國會的報告中指出,已發(fā)現(xiàn)銷往美國的電子元器件被國外組織預置了間諜軟件、惡意及損害安全的部分[5]。

混入偽冒產(chǎn)品。將質(zhì)量不合格和偽冒的微電子器件再次引入國防供應鏈,包括克隆偽造、廢棄再回收、打磨翻新、為改變質(zhì)量等級而重新打標、未經(jīng)許可的超量生產(chǎn)等。在美國國防部2010 年前后開展的系列調(diào)查中顯示[6-7],偽冒電子元器件已影響美國國防電子供應鏈的40%,涉及海陸空八大武器裝備。根據(jù)國際電子經(jīng)銷商協(xié)會(Electronic Resellers Association International,ERAI)2020 年 統(tǒng) 計 數(shù) 據(jù),2018 年偽冒電子元器件預計給美國半導體制造商造成了約75 億美元的損失;其中69.9%為集成電路[8]。

供應鏈條斷裂。原因包括技術升級或商業(yè)壓力迫使供應商停止生產(chǎn)、供應商倒閉或被收購、地緣政治沖突或自然災害導致生產(chǎn)和交付中斷等,嚴重威脅關鍵武器系統(tǒng)的維護和升級。

2 美國國防部從2003 年開始建立“可信供應”能力

2003 年,美國國防部制定了《國防可信集成電路戰(zhàn)略》,要求建立能為國防關鍵武器、情報系統(tǒng)提供可靠微電子器件的國防工業(yè)基礎。2004 年初,國防部發(fā)布《專用集成電路(Application Specific Integrated Circuit,ASIC)可信供應商臨時指南》,將“可信”定義為“通過評估國防安全用重要器件設計、生產(chǎn)、制造、分銷等環(huán)節(jié)中人員和流程的完整一致性,確定其具備保障國家安全的能力”;指出可信是國防系統(tǒng)的最低要求,明確必須由可信代工廠制造的器件類型[9]。

2.1 國防部希望為微電子器件提供“端到端”的全面安全保障

2004 年,美國國防部與國家安全局開展“可信代工廠”項目,并與美國IBM 公司簽署了一份為期10 年、總金額6 億美元的可信代工線共建合約,以滿足關鍵軍事和情報核心系統(tǒng)所需硅ASIC 的制造[10]。2007年“可信代工廠”項目增加“可信供應商”,采取認證方式,將微電子器件可信服務范圍從制造擴展至包括設計、掩模、封裝、測試等在內(nèi)的全產(chǎn)業(yè)鏈,并覆蓋砷化鎵、氮化硅等更多材料,更好保障ASIC設計和制造過程的完整性和保密性,以及滿足軍方多樣化發(fā)展需求。此后出臺的5 200.44、5 200.39 等多個國防法令中也持續(xù)強調(diào)可信的重要性[3]。

美國國防部和國家安全局各出資50%支持“可信代工廠”項目[11]。國防部在2004—2019 年間累計投入7.31 億美元,歷年投資情況見表1。由于數(shù)據(jù)不允許公開,國家安全局的投資情況不得而知。資金主要用于IBM/格芯(Global Foundry,GF)公司可信代工廠的改造和升級、可信供應商的認證、停產(chǎn)斷檔ASIC IP 和停產(chǎn)設備的購買、產(chǎn)品原型試樣和小批量生產(chǎn)方法研究等。國防部未來每年將繼續(xù)投入8 000~9 000 萬美元。截止2020 年6 月26日,可信供應商數(shù)量79 家,包括21 條制造工藝線,覆蓋主要類別微電子器件(含抗輻射器件)及部分光電器件,工藝及所對應特征尺寸如表2 所示[12]。

表1 國防部對“可信代工廠”項目歷年投資情況單位:萬美元

表2 美國現(xiàn)有可信制造能力

表2 (續(xù))

2.2 現(xiàn)有模式存在缺陷且日益無法滿足最先進制造能力需求

2014 年8 月,IBM 公司宣布出售微電子制造能力,美國國防部旋即針對無法獲取先進微電子器件可能帶來的風險、有無合適替代方案等內(nèi)容與產(chǎn)業(yè)界和國防部官員進行了討論[13],內(nèi)容因敏感未公開,結論是,短期內(nèi)沒有隸屬于美國且掌握先進制造技術的美國境內(nèi)/外的代工廠可進行替代,長期啟動研究和驗證具備替代能力的制造技術及新建所有權歸政府的代工線等也有相應的風險和限制。

2015 年7 月,格芯公司完成對IBM 公司微電子制造能力的收購。盡管格芯公司位于美國但由阿聯(lián)酋100%持有,還是引發(fā)了美國政府的擔心。同年10 月,美國政府問責署發(fā)布報告表示,盡管美國已在十多年前采取行動,但在保障可信先進微電子器件制造能力方面仍存在重大缺陷:一是防范手段單一,只有可信代工廠項目這一個手段;二是供應源單一,IBM 公司一直是先進微電子制造能力的唯一來源,隨著IBM 公司出售微電子制造業(yè)務,可信供應能力進一步惡化,但國防部無明確有效的應對措施[13]。從2015 年10 月開始的可信供應商名單中,原由IBM 公司提供的先進制造能力仍僅由格芯公司提供,且最先進制造能力僅為65 納米CMOS 工藝和32 納米SOI 工藝,遠落后于商用最先進技術數(shù)代。

3 美國國防部提出“技術實現(xiàn)可信”新安全框架

3.1 國防部要求加大對商用技術的使用

商用和軍用技術發(fā)展呈現(xiàn)“冰火兩重天”。美國國防部認為,特征尺寸的不斷減小帶來微電子器件研發(fā)和制造成本快速攀升,遠超國防部的承擔能力,如10 納米ASIC 的設計成本近4.2 億美元,是130 納米ASIC 設計費用的17~20 倍[14],只有需求量巨大的商用產(chǎn)品才能平攤高昂設計成本,也正因此牽引元器件企業(yè)投入到獲利更高和更快的商用市場,忽視甚至拒絕服務費時、費力、收益小的軍用市場,導致商用技術發(fā)展加速迭代,軍用技術發(fā)展舉步維艱。

先進商用技術能帶來武器裝備性能的巨大提升。美國國防部認為,微電子先進商用制造技術、商用IP、安全技術等可大幅提升武器裝備性能,以及增加逆向工程、偽造和克隆的難度,有助于保持超越競爭對手的優(yōu)勢。美國國防高級研究計劃局(Defense Advanced Research Projects Agency,DARPA)近年已研制出多款采用先進技術的微電子器件,證實先進技術可帶來性能的大幅提升,如以手機電池電量即可支撐180 個小時射頻信號識別和以64G/s 速度捕獲和分析超大量射頻數(shù)據(jù)的數(shù)據(jù)處理芯片,具備10倍高動態(tài)范圍的任意波形發(fā)生器,可獲取全戰(zhàn)域感知能力的單個可重構芯片,可支持實時機器學習的小型平臺,可高速智能捕獲、識別和分析數(shù)據(jù)的單個攝像頭等[15]。國防部也證實,對采用90 納米鰭形晶體管(FinFET)結構的ASIC 進行逆向工程需要1 年時間[16]。

可信供應模式不能滿足需求。美國國防部認為,“可信供應”運行機制相對封閉,國防部可獲得的商業(yè)IP 和設計資源非常有限,不能立刻享用技術發(fā)展所帶來的性能優(yōu)勢。2017 年2 月,美國國防科學委員會發(fā)布報告指出,國防部要與最先進商業(yè)微電子制造能力合作,而不是投資一個國防部所擁有的先進制造廠,這樣才具備資金可行性,以及滿足未來自動化和智能化發(fā)展新需求;同時應加強防篡改技術的研發(fā)及采取拆分制造和跟蹤流程等策略,多舉措保證安全[17]。

為此,美國國防部提出建立新安全框架,要求既能靈活使用商業(yè)技術和制造能力,又能保證高度安全,保障未來十年最有可能推動軍事能力發(fā)展的電子元器件的來源、安全和可靠。

3.2 DARPA提出“技術實現(xiàn)可信”框架和系列保障方法

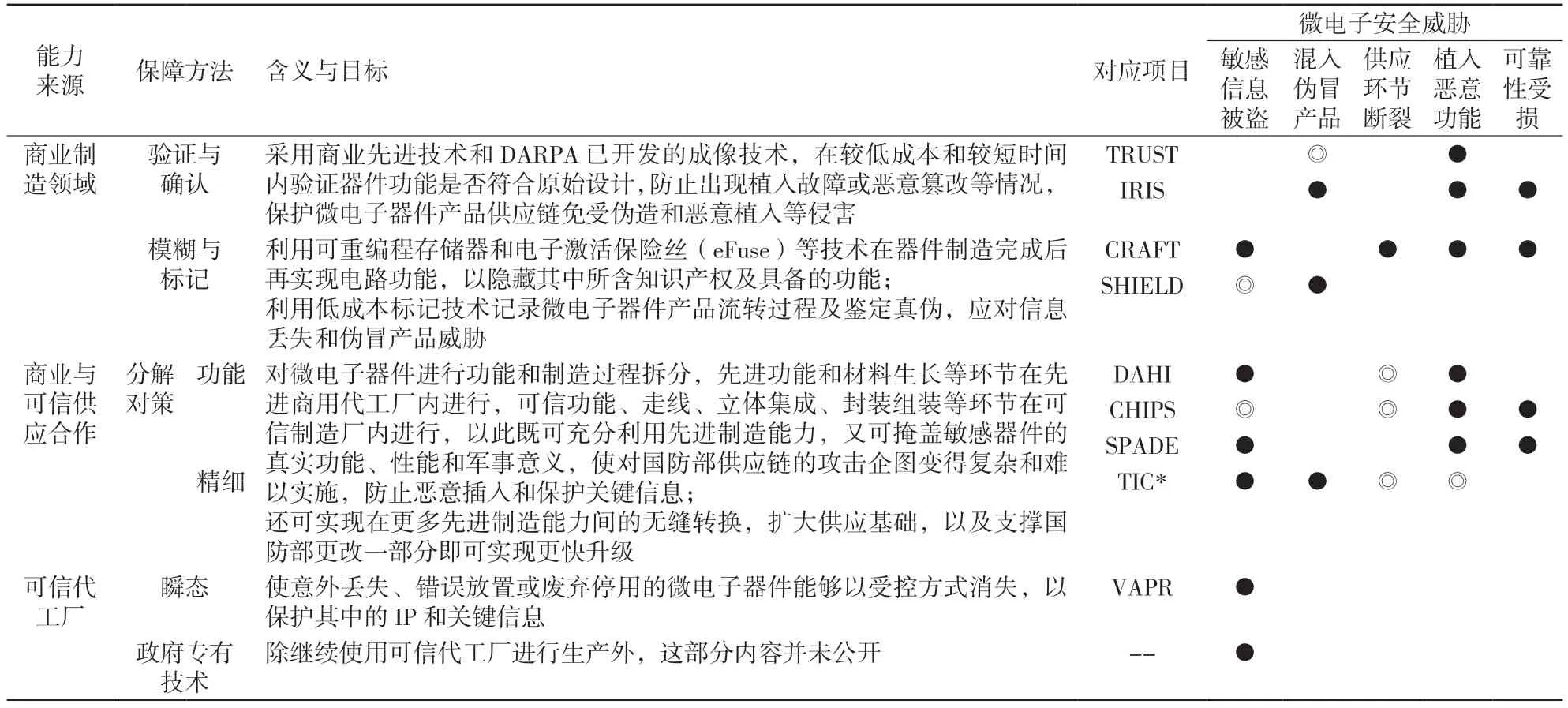

基于“可信供應”模式和已開展項目,DARPA提出“技術實現(xiàn)可信”新安全框架和多個保障方法,包括驗證和確認、模糊和標記、功能分解和精細分解、瞬態(tài)、政府專有解決方案等,可達到掩蓋器件功能、驗證器件來源和功能、保護敏感信息和IP、擴大國防供應基礎等目的[1]。各保障方法含義、對應項目和可應對威脅如表3 所示。

表3 各保障方法對應項目及可應對威脅

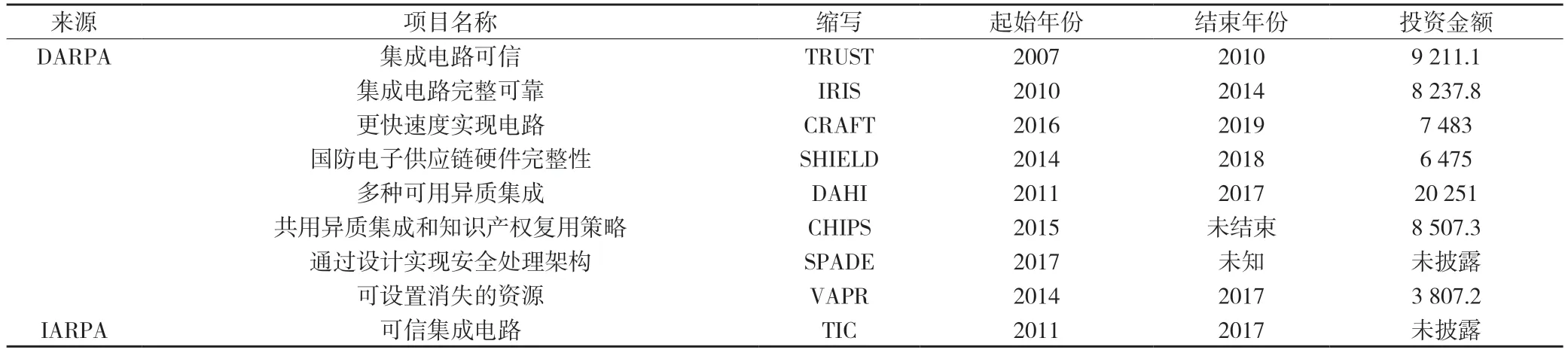

4 美國國防部匹配九個項目以建設體系化可信能力

新安全框架包含9 個項目,但并非新設項目,是對DARPA 和IARPA 對此前和正在開展項目的一次統(tǒng)籌。部分項目已經(jīng)完成并取得顯著成就,部分項目仍在進行中,項目起止時間和已投資金額如表4 所示。以下對各個項目的研究內(nèi)容和主要成果分別進行論述。

表4 “技術實現(xiàn)可信”框架下9 個項目的起止時間和投資金額 單位:萬美元

4.1 TRUST項目

DARPA 認為美國并未具備足夠能力來證明其武器裝備用微電子器件中不包含惡意的電路,為此于2007 年啟動TRUST 項目。

研究內(nèi)容。項目希望徹底摒棄傳統(tǒng)方法,開發(fā)出可根據(jù)測試概率與虛警概率得出可信度量的公式,驗證在非可信條件下設計和制造的軍用集成電路的可信程度,以及減少驗證所需的成本和時間,為識別遭惡意攻擊的集成電路提供了一個條明確防范途徑,測試對象包括商用ASIC 和現(xiàn)場可編程門陣列(Field Programmable Gate Arrays,F(xiàn)PGA)[18]。

主要成果。項目歷時四年,總投資9 211.1 萬美元,歷年投資情況如表5 所示[19-24]。項目研制出了系列技術,可通過對已制造出的ASIC 進行自動聚焦離子束(Focused Ion beam,F(xiàn)IB)分層、掃描電子顯微鏡(Scanning Electron Microscope,SEM)成像和圖像處理,重建對應版圖(GDS Ⅱ),可判斷制造過程是否符合原始設計;可自動檢查從寄存器傳輸列表(Register-Transfer Level,RTL)到網(wǎng)表再到GDSⅡ的器件設計全流程;可將ASIC 和FPGA 中第三方IP 中的未知邏輯單元庫與IP 功能特性進行關聯(lián),驗證IP 的完整性;開發(fā)出能準確地代表RTL 所描述的原始設計的比特流,及可驗證FPGA 的物理不可克隆(Physically Unclonable Functions,PUF)技術;可在240 小時內(nèi)完成對采用45 納米工藝、包含100 萬個晶體管的ASIC、FPGA 的驗證[19-24]。

表5 TRUST 項目歷年投資情況 單位:萬美元

成果應用。項目研發(fā)出FPGA 和ASIC 功能邏輯驗證工具和IP 驗證工具,已分別被美國國防微電 子 處(Defense Microelectronics Activity,DMEA)和空軍研究實驗室(Air Force Research Laboratory,AFRL)所采用[25]。

4.2 IRIS項目

TURST 項目結束后,DARPA 于2011 年啟動了IRIS 項目,進一步推進深亞微米CMOS 電路成像和器件識別技術的研究。

研究內(nèi)容。IRIS 項目最初名為“ 探索”(DISCOVER),2012 年更名為IRIS。項目將研究對象拓展為“電路設計規(guī)則和功能未知”的ASIC,重點研究可在僅知道有限性能指標的前提下非破壞性地識別出數(shù)字、模擬和混合信號集成電路功能的技術,可清楚確定該集成電路是否被惡意修改;還將加強對負偏壓溫度不穩(wěn)定(Negative Bias Temperature Instability,NBTI)、熱載流子注入(Hot Carrier Injection,HCI)、時間依賴性介電擊穿(Time Dependent Dielectric Breakdown,TDDB)和 電 遷 移(Electro Migration,EM)等ASIC 老化機制的研究,創(chuàng)新器件建模方法及分析和測試技術,實現(xiàn)可從物理層面判斷芯片壽命,大幅減少可靠性檢測所需樣品數(shù)量[26]。

主要成果。項目歷時五年,總投資8 237.8 萬美元,歷年投資情況如表6 所示[22-24,27-30]。在功能檢查方面:開發(fā)出可進行無損成像、電路提取和功能推導的方法和工具,可在晶體管級看到有關芯片制造和電路功能的信息;可對基礎元器件(晶體管、電容、電阻)、存儲器和互連進行非破壞性成像識別和提取網(wǎng)表;可對45 納米CMOS 數(shù)字和混合信號IC、ASIC 和FPGA 中第三方IP 進行功能推導;將逆向工程的時間從數(shù)月減少至數(shù)周。在可靠性評估方面:結合成像、電路提取和可靠性建模分析,可識別測試IC 樣品中的異常及確定其對可靠性的影響,顯著提升可靠性分析的準確性、功能性和有效性;可對90 納米CMOS 數(shù)字IC 和130 納米CMOS 混合信號IC 做基于少量樣品的可靠性推導;開發(fā)出可模擬電路性能并解決器件老化問題的模型,能夠檢測出為了促進早期失效而承受應力的IC 或在丟棄后重新引入供應鏈的偽冒產(chǎn)品[22-24,27-30]。

表6 IRIS 項目歷年投資情況 單位:萬美元

成果應用。項目承研方雷神(Raytheon)公司在某軍事硬件上驗證功能推導準確性為99.4%。項目還研發(fā)出可用于防范偽冒電子元器件的掃描光學顯微鏡(ASOM)技術。美國海軍水面作戰(zhàn)中心采用了該技術,并進一步建立了“虛擬實驗室”,可對器件全生命周期的各種缺陷進行檢測,保障嵌入國家關鍵軍事武器和網(wǎng)絡空間系統(tǒng)的器件的功能、完整性和可靠性[25]。

4.3 CRAFT項目

2016 年,DARPA 啟動CRAFT 項目,提出研發(fā)“面向?qū)ο笤O計”(Object-Oriented Design,OOD)的軟件工具,希望能顯著減少先進節(jié)點設計和制造的過高成本。

研究內(nèi)容。一是通過自動生成器實現(xiàn)大部分設計任務的自動化,實現(xiàn)從高級OOD 語言到原理圖的直接轉(zhuǎn)化,減少現(xiàn)有流程所需的大量驗證工作,如圖1 所示[16],將軍事所需高性能ASIC 的設計和制造周期縮短為之前的1/5,如將28 納米ASIC 的研制由2.5 年減少為0.6 年;二是創(chuàng)建知識貯藏庫,歸檔國防部關鍵軍用ASIC 設計中涉及的文檔和IP,使IP 庫復用率達50%以上,大幅降低設計工作量;三是提升IC 設計在不同代工線、不同工藝節(jié)點上遷移的靈活性,將遷移的工作量減少80%,擴大先進制造能力供應來源;四是研究電子激活保險絲(eFuse)等可掩蓋敏感信息的技術,當IC 制造完成后再通過保險絲來改變內(nèi)部連接實現(xiàn)電路功能[31]。

圖1 面向?qū)ο笤O計與傳統(tǒng)設計流程對比

主要成果。項目歷時四年,總投資為7 483 萬美元,歷年投資情況如表7 所示[30,32-36]。項目已完成OOD 方法的設計流程,建立了一個包含完成OOD流程所需的知識產(chǎn)權、方法和工具的知識庫;形成向所有國防承包商開放的(multiply project wafers,MPW)服務能力,具體指標為中國臺灣臺積電公司的300 毫米晶圓、16 納米FinFET 工藝,芯片面積不超過2.5×2.5 平方毫米,單次單個用戶成本為5萬美元,并完成了實驗性設計和3 次MPW 流片。模擬集成電路和數(shù)字集成電路的設計時間分別壓縮為原來1/11 和1/8;將數(shù)字和混合信號ASIC 遷移至格芯16nm 工藝的所需工作量分別減少為原來的1/5.3和1/4.3[37]。研制的原型芯片包括多應用電子戰(zhàn)/雷達用芯片、多應用可重置數(shù)字信號處理器、計算機視覺加速器、高性能數(shù)字接收機、無人駕駛車輛感知/決策芯片等[16,30,32-36]。

表7 CRAFT 項目歷年投資情況 單位:萬美元

4.4 SHIELD項目

為了加強對微電子器件產(chǎn)品流通過程的管控,DARPA 于2014 年啟動了SHIELD 項目,希望研發(fā)出能隨時隨地確認器件真實性的技術。

研究內(nèi)容。重點研發(fā)小晶片(dielet)及配套技術,包括可感知X 射線、可見光、高溫等使用環(huán)境及捕捉對芯片進行成像、去膠、去帽等行為的無源傳感器,以檢測和記錄試圖偽冒、非法訪問和逆向破解等行為;采用不易破解的加密算法和抗逆向工程技術,以保障密鑰安全;可實現(xiàn)無線供電的射頻供能技術;采用可進行短時間大數(shù)據(jù)交換的通信技術;在遭到被整體移除等試圖篡改等行為時變得易碎等。小晶片將作為硬件標識與被保護元器件一同封裝,但相互之間沒有電連接且產(chǎn)生影響;支持大批量、集中、快速、低成本檢測;可幫助國防部預防、檢測和應對偽冒產(chǎn)品入侵國防電子供應鏈。小晶片結構如圖2(a)所示[38-39]。

圖2 SHIELD 項目

主要成果。項目歷時5 年,總投資6 475 萬美元,歷年投資情況如表8 所示[27-29,31-34]。項目已研發(fā)出小晶片,采用14 納米的CMOS 工藝,面積為100 微米×100 微米、厚度為10 微米、成本小于1 美分、如圖2(b)所示[16,28-30,32-35]。國防部還建立了一個在線數(shù)據(jù)庫,記錄每一個小晶片的狀態(tài)和位置。在檢測中,首先采用手持式或自動探頭靠近小晶片進行掃描,再使用手機等便宜通用設備將序列號上傳至服務器。該服務器將向小晶片發(fā)送未加密的問題,小晶片將從無源傳感器發(fā)送回帶有篡改指示的加密答案和數(shù)據(jù),以比對真?zhèn)危ぷ鬟^程如圖2(c)所示。

表8 SHIELD 項目歷年投資情況 單位:萬美元

4.5 DAHI項目

為了充分利用各種材料和工藝帶來的性能優(yōu)勢,DARPA 在“硅上化合物半導體材料”(Compound Semiconductor Materials on Silicon,COSMOS)等項目實現(xiàn)磷化銦(InP)晶體管與硅CMOS 電路集成的基礎上,于2011 年啟動了DAHI 項目,全力推動更多材料異質(zhì)集成技術的發(fā)展。

研究內(nèi)容。主要研究在同一硅襯底上的多種材料異質(zhì)集成工藝、高產(chǎn)量制造能力、新型電路設計與構架。項目擬實現(xiàn)集成的材料和器件包括:(1)硅基CMOS 的模擬和數(shù)字IC;(2)氮化鎵(GaN)基高功率、高電壓和低噪聲放大器;(3)基于砷化鎵(GaAs)和磷化銦(InP)異質(zhì)結雙極晶體管(HBT)和高電子遷移率晶體管(HEMT)的高速/高動態(tài)范圍、低噪聲電路;(4)基于銻基化合物半導體的高速、低功耗電子器件;(5)用于直接帶隙光子源和探測器的化合物半導體光電器件,以及硅基調(diào)制器和波導等;(6)傳感器、執(zhí)行器和射頻諧振器用微機電(MEMS)器件;(7)熱管理結構。項目將構建出真正的片上系統(tǒng)并大幅降低尺寸、重量和體積。研究成果將轉(zhuǎn)移到國防部的可信制造廠中,推進技術的持續(xù)迭代,并供國防部實驗室、聯(lián)邦政府投資的研發(fā)中心、學術界和工業(yè)界使用[40-41]。

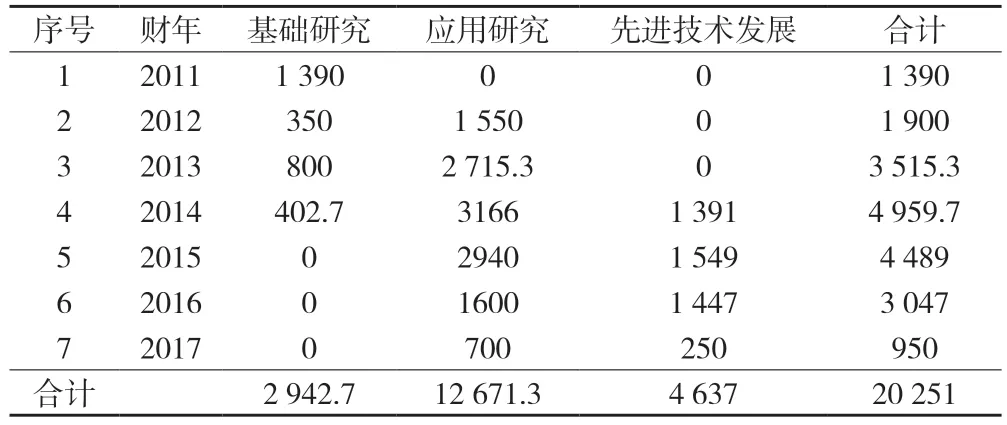

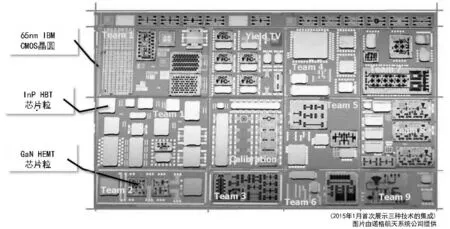

主要成果。項目歷時7年,總投資2.025 1億美元,DARPA 在基礎研究、應用研究和先進技術發(fā)展三部分預算都給予了資金支持,歷年投資情況如表9 所示[23-30,32-34]。項目最終開發(fā)了一個高產(chǎn)量、高良品率、高可靠性、可轉(zhuǎn)移至代工廠持續(xù)運行的異質(zhì)集成工藝。為了演示和驗證研究成果,項目實現(xiàn)了低噪聲放大器、高速跟蹤和保持電路、射頻數(shù)模轉(zhuǎn)換器和可調(diào)諧帶通濾波器等異質(zhì)集成射頻/混合信號電路,低噪聲激光器、光射頻信號源、成像陣列芯片和片上激光雷達等光電器件,實現(xiàn)集成多相發(fā)射機和壓控振蕩器-放大器鏈,可滿足雷達、電子戰(zhàn)和通信等下一代系統(tǒng)使用需求[23-30,32-34]。2015—2016 年,項目以MPW 方式進行了三次流片。圖3 為2015 年1 月硅、InP 和GaN 三種材料制成的小芯片(chiplet)的異質(zhì)集成的首次展示[42]。

表9 DAHI 項目歷年投資情況 單位:萬美元

圖3 硅、InP 和GaN 三種材料所制造的小芯片的首次異質(zhì)集成

4.6 CHIPS項目

2014 年,DAHI 項目在執(zhí)行過程中開發(fā)出了三種基于小芯片的異質(zhì)集成工藝中。DARPA 從2015年啟動CHIPS 項目,著重研發(fā)可用于異質(zhì)集成的小芯片,顛覆傳統(tǒng)單片集成電路的設計和制造方式。

研究內(nèi)容。CHIPS 原名“快速和大型混合信號設計”(Fast and Big Mixed-Signal Designs,FAB),2017 年更名為CHIPS。主要研究四個領域:(1)研制大量具備多種功能、可高度復用的小芯片,重點是將現(xiàn)有一系列數(shù)字、模擬、射頻電子系統(tǒng)和器件模塊化,并不研發(fā)新的器件技術和電路結構;(2)建立一套通用數(shù)字、模擬接口標準,重點是在現(xiàn)有龐大的接口標準中篩選并建立最小接口標準集,并不主動制定新結構標準;(3)研發(fā)可實現(xiàn)異質(zhì)集成、模塊化設計的設計工具,簡化小芯片的設計開發(fā);(4)研發(fā)配套的集成和組裝方法[43]。這些小芯片已預先設計好并物理實現(xiàn),可在通用架構下通過通用接口,以快速組裝方式實現(xiàn)各種功能和更新?lián)Q代,解決復雜IC 的設計難題,并大幅降低研制成本和交付周期,如將IC 的研發(fā)成本從現(xiàn)在的500~1 000萬美元降到200 萬美元,研發(fā)時間從21 個月減少到7個月。這種模塊化新范式不僅為美國國防部實施“微系統(tǒng)”戰(zhàn)略提供技術路徑,更可能對現(xiàn)有電子元器件設計和制造流程進行重組,不再需要設計、驗證和制造等環(huán)節(jié),如圖4 所示[44]。

圖4 CHIPS 項目將重組電子元器件供應鏈

主要成果。項目原定研發(fā)周期為四年,目前仍在進行中,已累計投入8 507.3 萬美元,歷年和未來兩年投資情況如表10 所示[29-30,32-36]。CHIPS 項目成果的報道不多,可知的有美國英特爾公司在2018 年發(fā)布了開放源碼AIB 協(xié)議[45],是一種時鐘轉(zhuǎn)發(fā)并行數(shù)據(jù)傳輸機制,主要針對英特爾的嵌入式多芯片互連橋接(Embedded Multi-Die Interconnect Bridge,EMIB)封裝技術。2020 年3 月,美國Ayar公司通過AIB 接口用其高效光信號接口(I/O)電路TeraPHY 小芯片替代了FPGA 傳統(tǒng)接口電路,并通過EMIB 實現(xiàn)了與英特爾公司FPGA 產(chǎn)品的共同封裝[46]。由于小芯片和異構集成正好成為應對摩爾定律發(fā)展受阻及需求多樣化的最好解決方案,受到了整個半導體產(chǎn)業(yè)界的高度關注。英特爾、AMD 和臺積電等公司積極研發(fā)先進集成技術和推出了小芯片產(chǎn)品。

表10 CHIPS 項目歷年投資和未來兩年預算 單位:萬美元

4.7 SPADE項目

DARPA 于2017 年3 月 啟 動SPADE 項目[47],并表示其是“電子復興計劃”(Electronics Resurgence Initiative,ERI)的研究基礎之一,但未公開SPADE 項目的研究目標、內(nèi)容及資金預算等信息,只能在零星資料中得出以下內(nèi)容。項目建議,在可信代工廠內(nèi)生產(chǎn)為關鍵數(shù)據(jù)和算法提供加密和保障的可信器件,并與最先進商業(yè)芯片共同安全封裝。這些可信器件的功能主要分為兩部分,一是保存敏感信息、秘鑰等,執(zhí)行敏感邏輯控制功能;二是主動監(jiān)測進出商業(yè)芯片的所有數(shù)據(jù)、控制指令、狀態(tài)和權限等,一旦發(fā)現(xiàn)后者受到攻擊,立刻實施隔離以減少風險[42]。

4.8 VAPR項目

DARPA 一直關注并投資支持可自分解電子元器件的基礎性研究[48-49],并于2013 年底啟動了VAPR 項目,正式提出“瞬態(tài)電子”這一全新概念并全面推進發(fā)展。

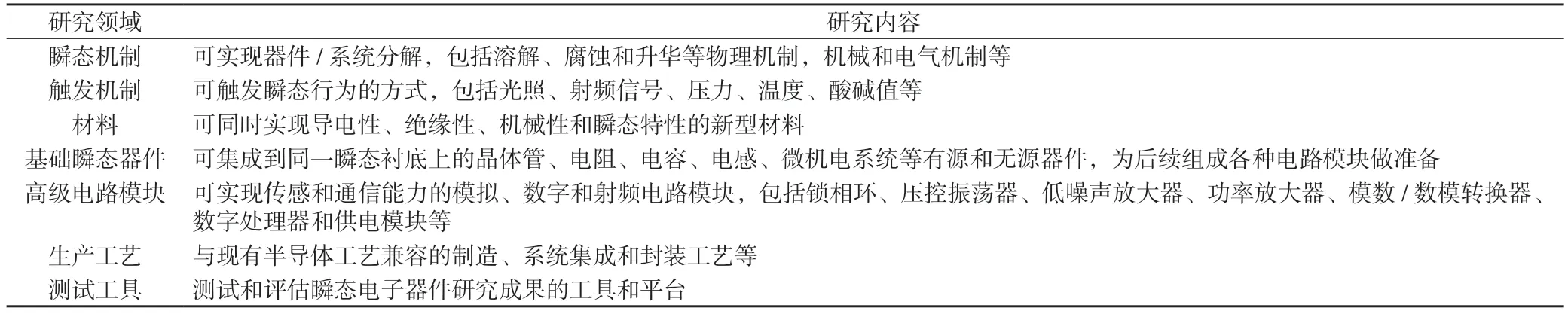

研究內(nèi)容。瞬態(tài)電子器件能夠具備多種功能,只在一個非常短和已經(jīng)確定好的時間段內(nèi)工作,在光、熱和液體中等條件瞬態(tài)觸發(fā)后迅速或以設定的速度自分解和消失。項目將開發(fā)和建立一套瞬態(tài)機制、支撐材料、器件和模塊、配套工藝等,具體如表11 所示。開發(fā)出的瞬態(tài)電子器件性能可與COTS相比,瞬態(tài)特性則可預先編程、實時調(diào)整、根據(jù)命令觸發(fā)和/或?qū)Νh(huán)境敏感。瞬態(tài)電子器件除了可減少對環(huán)境的污染、使病人不再經(jīng)受醫(yī)療設備從體內(nèi)移除之苦,重要的是可保證軍事秘密和先進技術不落入敵手[50-52]。

表11 VAPR 項目研究內(nèi)容

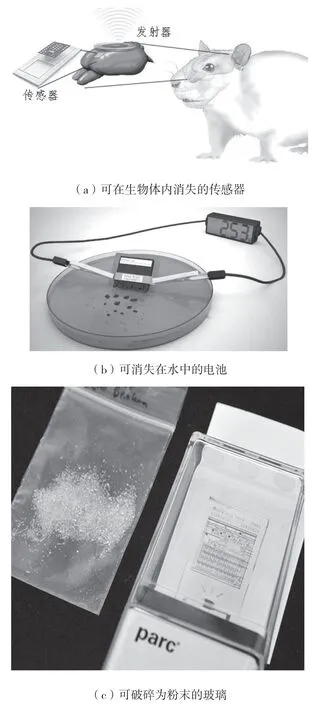

主要成果。項目歷時四年,總投資3 807.2 萬美元,DARPA 基礎研究和應用研究都給予了資金支持,歷年投資情況如表12 所示[28-30,31-34]。項目研發(fā)出了快速蝕刻、溶解、升華和碎裂等多種瞬態(tài)機制;可預測瞬態(tài)效應的力學、應力、腐蝕速率建模工具;聚碳酸酯基材料、應力工程基底、水凝膠等可將電子特性和瞬態(tài)特性結合起來的新材料;瞬態(tài)器件的制造方法,可實現(xiàn)具有射頻、存儲器、數(shù)字邏輯、電源等關鍵功能的瞬態(tài)電子器件的制造[28-30,31-34,52]。

表12 VAPR 項目歷年投資情況 單位:萬美元

成果舉例。在該項目支持下,美國伊利諾斯大學香檳分校等聯(lián)合開出米粒大小的全新微小超薄電子傳感器,可植入頭部監(jiān)控頭骨內(nèi)壓力和溫度等參數(shù),測量精度與傳統(tǒng)設備相當,可在不需要時完全無害地溶解到生物體內(nèi)的液體中[53],如圖5(a)所示;美國愛荷華州立大學研究出可自分解鋰離子電池,尺寸為5×6×1 立方毫米,可提供2.5V 電壓,為桌面型計算器供電15分鐘,在置入水中30分鐘內(nèi)消失,是首個展現(xiàn)出具有實用價值電量、穩(wěn)定性和壽命的瞬態(tài)電池[54],如圖5(b)所示;美國帕洛阿爾托研究中心(Palo Alto Research Center,PARC)研發(fā)出應力工程玻璃基板,可在收到自毀電流信號將其上的芯片一同碎裂為圖5(c)中左側(cè)的粉末[55]。

圖5 VAPR 研究成果示例

4.9 TIC項目

2011 年,為使國家情報部門也能利用先進制造能力制造所需集成電路及保障其中信息安全,IARPA 在DARPA TRUST 項目的基礎上另辟蹊徑,提出將制造過程拆分的新思路,并啟動了TIC 項目。

研究內(nèi)容。項目重點研究將微電子器件制造過程拆分為前道(Front-End-of Line,F(xiàn)EOL)和后道(Back-End-of Line,BEOL)的技術及可行性。前道在海外的先進制造工廠實現(xiàn)基礎材料的生長,后道在美國的可信代工廠內(nèi)進行可信金屬化等來實現(xiàn)功能,如圖6 所示,以此實現(xiàn)隱藏功能、保證安全、保護IP[56-57]。研究領域包括:制造過程的安全拆分,可在FEOL 階段隱藏電路功能的技術,電路性能驗證及表征,新的晶體管/電路設計及新堆疊方法等。研究對象是8 寸及以上晶圓,0.25 微米及以下特征尺寸的高性能微電子器件。

圖6 TIC 項目拆分制造過程示意

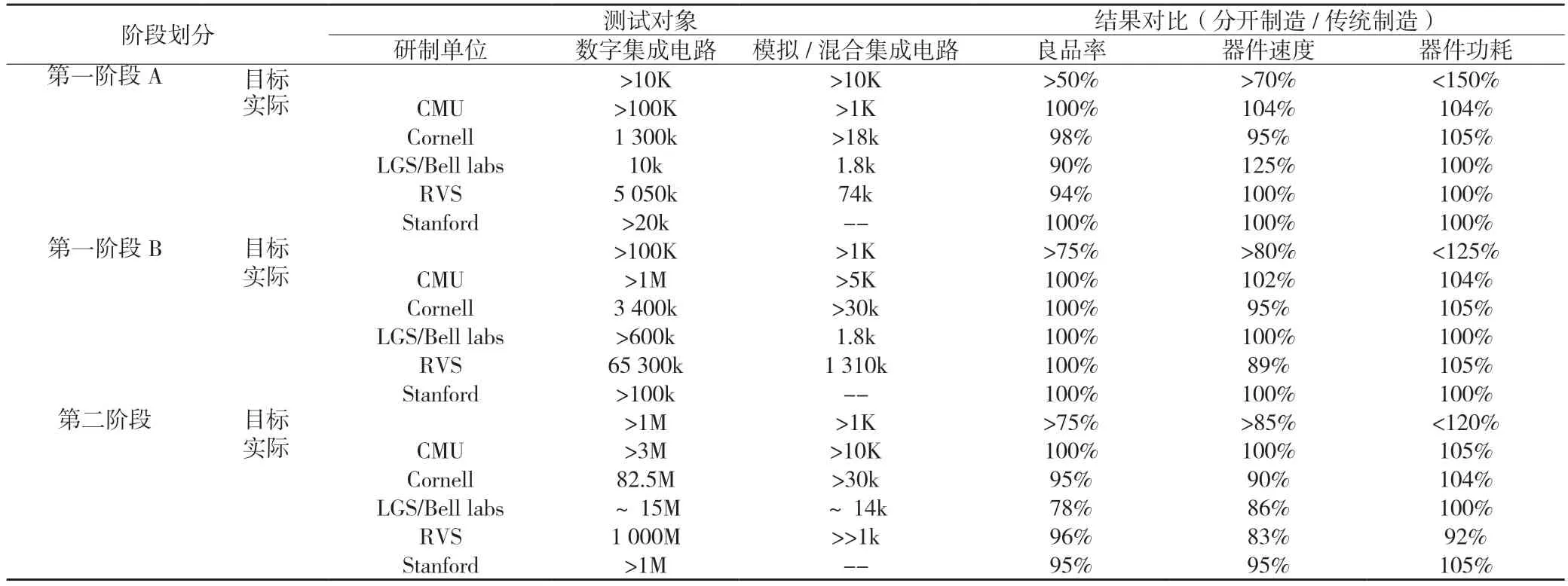

研究成果。TIC 項目歷時6 年,由于美國國家情報項目(National Intelligence Program,NIP)的預算不公開,所以TIC 的資金投入情況未知[58]。在項目的第一、二階段,IARPA 分別采用130 納米、65 納米和28 納米工藝及MPW 形式,對卡納基梅隆大學(CMU)、康奈爾大學(Cornell)、LGS/貝爾實驗室(LGS/Bell labs)、雷聲視覺系統(tǒng)公司(RVS)、斯坦福大學(Stanford)共5 家承研單位設計的數(shù)字集成電路和模擬/混合集成電路芯片,分別采取了傳統(tǒng)制造和分開制造的方式,選取器件的良品率、器件速度和功耗三個指標,以分開制造方式所得芯片性能指標除以傳統(tǒng)制造所得芯片相應指標作為衡量分開制造效果的比對數(shù)據(jù)。傳統(tǒng)制造、分開制造的FEOL 和BEOL 所選廠商及地點如表13 所示。第一階段A、第一階段B 和第二階段的比對數(shù)據(jù)如表14 所示。可以看出,除了雷聲公司一款采用28 納米制造的器件在速度指標上略低于預期目標,在其他指標中是否分開制造并無顯著差異[57][59]。

表13 TIC 項目各階段制造地選擇詳情

表14 TIC 項目研究成果對比

5 做法借鑒和預警

5.1 圍繞發(fā)展主線和已有基礎建立體系化能力

發(fā)展思路一脈相承,實現(xiàn)器件整體能力提升。在國防部提出新安全發(fā)展需求時,DARPA 并沒有設置新的項目,而是積極引入此前項目的研究成果,并與為應對“摩爾定律趨緩”而發(fā)展的芯片模塊化和異質(zhì)集成的發(fā)展思路保持同步,如CHIPS、DAHI、CRAFT 三個項目也是DARPA 著名“電子復興計劃”的研究基礎,以此在最快時間、用最低成本完成安全保障能力的構建,并更好地融入美國國防部所提出的“微系統(tǒng)”發(fā)展大戰(zhàn)略中。

分階段逐步推進,及時調(diào)整和完善。在TRUST項目啟動之初,DARPA 曾野心勃勃地設置了三個方向以應對安全問題,第一是開發(fā)可快速分析微電子器件版圖的技術和工具。第二是將復雜IC 拆分為較小的子電路,再進行堆疊或單片集成。第三是研發(fā)為IC 添加“硬件保護套”的新技術,可監(jiān)視IC性能并在出現(xiàn)未預期操作時報警。但隨著項目的進行,DARPA 將TRUST 項目研究集中在第一個方向,后兩者則是待相關技術成熟后通過另設CHIPS 和SHIELD 等項目來完成。

項目設置體系化,強調(diào)從研到用。上述九個項目都是為解決具體問題而設,具有剛性應用要求,為此DARPA 通過體系化設置研究內(nèi)容來保障該目標的達成。如多個項目都強調(diào)了對材料、模型、電路結構和體系架構、制造工藝、測試樣品、標準和規(guī)范、配套設計流程和軟件工具等的全方位研究;同時注重與現(xiàn)有產(chǎn)業(yè)基礎的融合,以降低產(chǎn)業(yè)界接受的門檻,獲取最大生態(tài)系統(tǒng)支持。

5.2 美國可能利用技術優(yōu)勢對我發(fā)起攻擊和形成壓制

首先,美國已具備微電子器件產(chǎn)品供應鏈流轉(zhuǎn)跟蹤能力,以及針對多種攻擊的檢驗檢測能力,美國完全有可能變守為攻,以極低成本,通過植入缺陷、嵌入惡意木馬、投入偽冒和質(zhì)量不合格產(chǎn)品等各種方式,對我國各領域用電子元器件發(fā)起全面攻擊,而無誤傷自己之虞。由于元器件在整個電子信息產(chǎn)業(yè)中的核心和基礎地位,所造成的影響勢必會呈指數(shù)級放大。而且,美國還有可能為此前美國多次宣稱“中國監(jiān)聽、監(jiān)視、攻擊美國”的蓄意抹黑提供一個“確鑿的證據(jù)”[5]。

其次,美國國防部正轉(zhuǎn)向采用更通用、低成本和已就緒的通用電路,僅通過改編軟件就可使電路實現(xiàn)所需的專用性能,還將加大對先進商用技術的使用力度,軍用微電子器件的性能和開發(fā)效率都將得到顯著提升,將極大地促進美國下一代武器裝備的研發(fā)和提升現(xiàn)有裝備實力。再加之美國對我國半導體產(chǎn)業(yè)的全力打壓,不僅將限制我國半導體產(chǎn)業(yè)整體技術水平的提升,還有可能對我國形成軍事壓制。

5.3 我國也應加強小芯片和安全技術的發(fā)展布局

小芯片和先進集成技術正帶來新發(fā)展范式,成為半導體產(chǎn)業(yè)的爭奪熱點。小芯片的研發(fā)和制造、在系統(tǒng)中的復用和協(xié)同,以及配套的仿真和制造工具,將共同構建出一個全新生態(tài)系統(tǒng),美國已展開了全面布局并加速取得進展。小芯片提供了區(qū)別于傳統(tǒng)摩爾定律的另外一條發(fā)展道路,但并不是我國“彎道超車”的機會,相反是對我國半導體設計、制造、封測各環(huán)節(jié)技術實力的一次“大考”,每個環(huán)節(jié)都需要在多年不斷的積累和沉淀上不斷創(chuàng)新。我國也必須重視小芯片的發(fā)展,持續(xù)推進在小芯片研制和性能檢測、標準起草、設計工具的研制、先進異構集成技術等領域的研究,以跟上產(chǎn)業(yè)發(fā)展的步伐。

我國所使用的電子元器件大量依賴進口,并廣泛地應用于國防、電力、交通、金融等國家關鍵設施和重大任務系統(tǒng),存在極大安全隱患。我國也必須加強安全技術的研究,不僅可以更好地保障我國所用電子元器件具備所需的性能和可靠性,避免出現(xiàn)存在漏洞、缺陷、偽冒等情況,也是防范他國在元器件層面對我國發(fā)起攻擊的必要前提。