一種低功耗的容軟錯誤鎖存器設計

徐輝 施峰

(安徽理工大學,安徽 淮南232001)

一、引言

電路可靠性已成為現代納米電子器件中的主要問題。隨著CMOS技術快速發展,節點的供電電壓和電容也在不斷地降低。電路節點存儲的關鍵電荷減小,增加了輻射環境中對于外部噪聲的敏感性。當一個帶有高能量的粒子(比如α粒子或者中子)轟擊組合電路中的敏感節點時,可能會產生一個電流脈沖,該脈沖被稱為單粒子瞬態(single event transient,SET)[1]。SET會通過組合電路下游傳播,在下一個時序電路鎖存,從而造成軟錯誤;當一個高能粒子轟擊鎖存器或者觸發器中的內部節點時,粒子轟擊產生的沉積電荷大小超過了臨界電荷時,就會導致存儲值發生翻轉,這種現象稱為單粒子翻轉(single event upset,SEU)[1]。半導體行業協會路線圖(The Semi-conductor Industry Association Roadmap)表明SEU效應已經成為未來電子系統的可靠運行主要威脅因素之一[2]。

目前,國內外眾多學者對軟錯誤的研究,提出了一些有效的措施。對于存儲單元,通常選擇成本較低的糾錯碼技術進行軟錯誤防護。在一般的應用中,存儲元件已不再是研究的重點了。抗輻射加固技術主要集中在鎖存器的設計上,對于鎖存器電路SEU防護的加固方法可以被分成三類。第一類是有內部互鎖反饋回路的鎖存器,例如文獻[5]中提到的DICE(Dual Interlocked Storage Cell)鎖存器;第二類,鎖存器具有通過使用C單元或者三模冗余(TMR)的方式過濾和屏蔽SEU的能力,例如文獻[15]中提到的FERST(Feedback redundant SEU-tolerant latch)鎖存器;第三類,鎖存器通過增加晶體管尺寸來增強敏感節點的電容,例如文獻[11]中含有施密特觸發器的鎖存器。這些加固方法的性能都是通過提升SEU容忍能力、面積、速度和功耗進行評估。

針對軟錯誤對鎖存器帶來的影響,本文提出一種低功耗的抗SEU/SET鎖存器。鎖存器由3個互相鎖存的C單元構成,通過采用高電平信號控制時鐘反相器的方法構建內部反饋回路。透明期狀態時,回路處在關斷狀態,從而降低鎖存器的功耗。提出的鎖存器是基于異構的雙模冗余互鎖設計。當鎖存器內部節點受到高能粒子轟擊從而發生翻轉,其輸出節點的邏輯值依然保持正確的邏輯值。受到影響的內部節點,很快在下一個透明期到來被恢復。除此之外,通過在一路添加延遲單元,可以很好地過濾從上游組合電路傳播過來的SET脈沖,對于輸出不受影響。

二、現有的加固鎖存器設計

(一)靜態鎖存器

圖1所示為標準靜態鎖存器,由2個傳輸門和3個反相器構成。通過使用反相器INV3和傳輸門TG2組成反饋回路存儲數據[3]。由參考文獻[16]實驗結果測得可知,鎖存器內部節點(圖1中節點B,C或Q)關鍵電荷非常低,易受到瞬態故障的影響,使得輸出節點邏輯值發生偏轉,并且不能恢復。

圖1 標準靜態鎖存器

(二)TMR鎖存器

圖2所示為基于三模冗余的TMR鎖存器。TMR鎖存器是將靜態鎖存器復制成三份(latch1,latch2,latch3),每一個靜態鎖存器的輸出都和表決電路的輸出相連。當任意一個靜態鎖存器中的內部節點受到瞬態故障影響時,TMR鎖存器都會保證有正確的邏輯值輸出。雖然TMR鎖存器對單粒子翻轉全免疫,但是成本開銷較大。

圖2 TMR鎖存器

(三)LSEH-1鎖存器

圖3所示為文獻[14]提出的LSEH-1鎖存器,該鎖存器包含三個反饋回路(A,B,C)和1個C單元構成。當其中任意一個反饋回路受到粒子轟擊后,使得節點發生翻轉。另外兩個反饋回路沒有受到影響,并且糾正受到影響的節點。另外,LESH-1鎖存器利用時間偏移原理,能夠過濾從上游組合電路傳播過來SET脈沖。

圖3 LSEH-1鎖存器

(四)FERST鎖存器

圖4所示為文獻[15]提出的FERST鎖存器。該鎖存器能夠過濾N1、N2、N3、N4和Q節點上的瞬態故障,對SEU完全免疫。但是,由于采用了多個C單元,使得數據通過鎖存器的延遲時間大大增加,且該結構不適用于門控時鐘電路。

圖4 FERST鎖存器

(五)STI鎖存器

圖5所示為文獻[11]提出的STI鎖存器。該鎖存器由時鐘控制的反相器,施密特觸發器和電壓比較器組成。STI鎖存器利用施密特觸發器的時間滯后特性提供全節點保護,避免軟錯誤發生。由于該鎖存器采用了施密特觸發器,使得該鎖存器傳播延遲比較大。

圖5 STI鎖存器

三、提出的加固鎖存器設計

(一)電路結構與容SEU原理

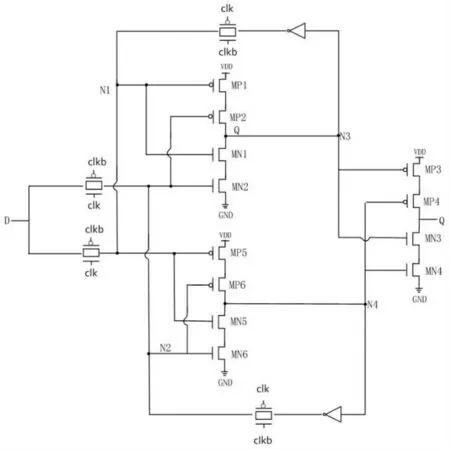

本文提出了一種基于雙模冗余下的低功耗加固鎖存器,電路結構如圖6所示。鎖存器中的每一個C單元輸出狀態都是由另外兩個C單元輸出控制,三個C單元之間相互形成了互鎖的結構。其中,D和Q是鎖存器的輸入和輸出節點,CLK和CLKB分別為系統時鐘和反系統時鐘。該結構包含3個傳輸門(TG1,TG2,TG3),4個反相器(INV1,INV2,INV3,INV4),2個時鐘反相器(GINV1,GINV2),3個二輸入的C單元(CE1,CE2,CE3)。

圖6 提出的加固鎖存器

當CLK=1,CLKB=0時,鎖存器進入透明狀態,傳輸 門TG1和TG2打開,TG3關閉,時鐘反相器GINV1,GINV2關閉,反饋回路Loop1和Loop2處于斷開狀態。內部節點N3、N4分別通過傳輸門TG1和TG2與輸入節點D連接,N3和N4一方面分別通過反相器INV1和INV2把數據寫入到N1和N2節點;N1和N2作為CE3單元的輸入,通過CE3單元把數據寫入到Q節點。另一方面N3和N4分別通過反相器INV4和INV3把數據寫入到N5和A節點,N5和A作為CE1和CE2的輸入。在透明期時,TG3和反饋回路關閉,降低鎖存器工作時的功耗。

當CLK=0,CLKB=1時,鎖存器進入鎖存狀態,傳輸門TG1和TG2關閉,內部節點N3和N4與輸入節點D之間斷開,TG3打開,晶體管MN11和MN13打開,使得時鐘反相器GINV1,GINV2打開,反饋回路Loop1和Loop2處于導通。此時,輸出節點Q通過傳輸門TG3,與時鐘反相器GINV1直接相連。Loop1反饋回路導通,使得CE1單元正常工作,并保持N3節點的邏輯值;Loop2反饋回路的導通,使得B節點的電荷通過時鐘門GIV2被節點N3補充。B點驅動的晶體管MP4和MN3與A點驅動晶體管MP3和MN4一起工作保持N4節點的邏輯值。因此,三個C單元(CE1,CE2,CE3)之間相互形成互鎖的結構,使得輸出節點一直都存在邏輯值。圖7所示為鎖存器在透明期和鎖存期時,內部每個節點仿真波形圖。

圖7 本文提出的鎖存器的仿真波形

鎖存器中對SEU敏感的節點有N3、N5、A、B、NQ、C、Q、N1、N2、N4。節點N3或C,N5、A、B和NQ,N1和N2發生瞬態故障情形相同,只需分析其中一個節點的瞬態故障即可。因此,SEU影響鎖存器的情形從N3、N5、Q、N1和N4這5種情況討論。

1.當N3節點發生瞬態故障時,內部節點N5、N1、B會發生翻轉,N4保持高阻態,節點N3的翻轉不會影響輸出節點Q的邏輯值。根據C單元的特性,兩個輸入信號不同時,輸出端將保持高阻態,依然保持了正確的輸出值。

2.當N5節點發生瞬態故障時,輸出節點Q的邏輯值沒有影響,依然保持了正確的輸出值。在鎖存階段,當N5節點短暫的發生翻轉,由于單元CE1的屏蔽功能,N3節點處在高阻態,通過驅動晶體管MP7和MN7把N5恢復至正確的邏輯值。

3.當Q節點發生瞬態故障時,由于節點NQ和輸出節點Q通過時鐘門GIV1相連,節點NQ也將受到影響,會發現翻轉。其他內部節點沒有受到影響(N5節點不變,使得N3節點處在高阻態),N2和N1節點保持不變,通過驅動CE3單元快速恢復節點Q的邏輯值。

4.當N1節點發生瞬態故障,CE3單元的兩個輸入不相同,由于單元CE3的屏蔽功能,輸出節點Q的邏輯值不受影響。由于N3節點未受到瞬態故障影響,通過反相器INV1把N1恢復至正確的邏輯值。

5.當N4節點發生瞬態故障時,由于節點N4和節點A通過反相器INV3相連,A節點也將受到影響,會發生翻轉。在另一條異構的路徑中,N3節點沒有受到影響,與N3節點類似,Q節點處在高阻態。

綜上所述,該鎖存器對SEU完全免疫。

(二)容SET原理

本文提出的防護SET鎖存器結構如圖6所示。通過在輸入節點D2和傳輸門TG2之間添加延遲單元,使得鎖存器的兩個輸入D1和D2之間產生時間偏移[4],在利用末端C單元的屏蔽能力過濾傳入的SET。

當CLK=1,CLKB=0時,鎖存器進入透明期。此時,時鐘反相器GINV1和GINV2,傳輸門TG3,兩個反饋回路Loop1和Loop2均關閉。輸入被分成兩條獨立的路徑應用在C單元上,一路是直接通過N3節點的D1路徑,另一路是從D2到N4帶有延遲單元的D2路徑,通過兩條數據路徑和C單元過濾從上游組合電路中的SET。

(三)SEU故障注入實驗

本文利用Hspice仿真工具對提出的鎖存器進行SEU故障注入,以評估提出鎖存器的抗SEU能力。實驗條件為:45nm的PTM工藝模型[5],1.0V供電電壓、時鐘頻率為500MHz、環境溫度為25℃。采用文獻[6]中雙指數電流源模型模擬粒子轟擊所產生的瞬態脈沖[6]。其中,雙指數電流源的數學公式為:

其中,I(t)為節點收集的電荷引起的電流,Q為受到高能粒子轟擊后節點收集的臨界電荷量,τ1和τ2是與工藝相關的時間常數[7]。考慮到讓實驗的數據更加充分,實驗分別在低電平和高電平的情況下對鎖存器中的節點進行故障注入,仿真結果如圖8和圖9所示。

圖8 各節點邏輯為“1”時的故障注入

圖9 各節點邏輯值“0”時的故障注入

由圖8、圖9可知,對內部節點N3注入SEU,正如之前描述一樣,N5和N1會發生翻轉,但是N2保持不變,并沒有影響Q節點的輸出。當對N1和N5節點注入SEU時,Q節點的邏輯值保持高阻態,并且N1和N5恢復到之前的正確邏輯值。當對節點N4注入SEU時,Q節點保持不變,受到影響的N4節點在下一個透明期恢復過來。對于鎖存器的輸出節點Q注入SEU,節點Q會在鎖存期間發生翻轉,并且在一定時間內恢復到初始邏輯值狀態。

(四)SET故障注入實驗

從圖10中可知,當鎖存器處在透明階段時,分別在時間4.2ns,對輸入D1和D2施加電壓信號為1.0V,寬度為300ps的脈沖。由于D2輸入中存在延遲單元,實驗中延遲的時間設置為200ps。因此,時間在4.4ns時,D2輸入中出現了和D1輸入中相同的脈沖信號。輸出端Q只產生很小的波動,幾乎可以忽略。因此,該鎖存器具有過濾從上游組合邏輯傳播來的SET脈沖的能力。

圖10 透明時期輸入D出現SET故障

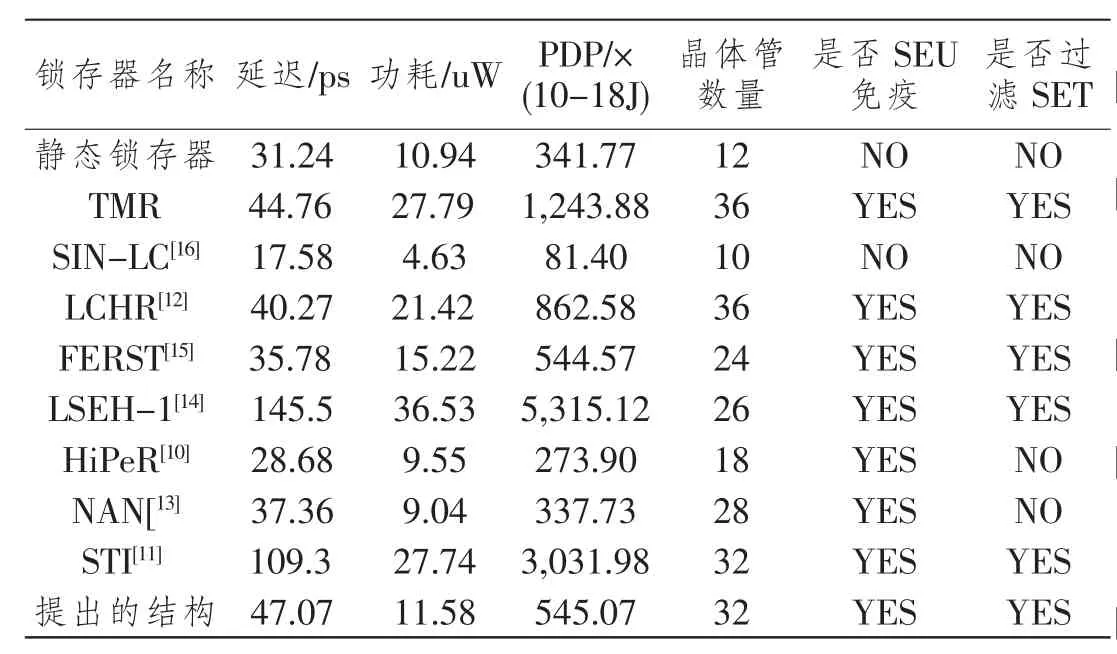

四、鎖存器的性能比較

為了便于對已有加固鎖存器充分的比較,表1所示為本文提出的鎖存器與已有的鎖存器的各個參數比較結果。第2列為鎖存器透明期工作時,輸入D至輸出Q的傳播時間,決定了鎖存器的速度,是重要的性能評估指標。第3列為功耗開銷,是在輸入切換活動率為50%的條件下測出。第4列為功耗延遲積(Power Delay Product,PDP),可以綜合的預估鎖存器的速度和功耗。第5列為面積開銷,根據文獻[8]中提到的方法計算面積開銷(使用晶體管數量代替面積開銷)。第6列為對SEU都全免疫,只有SIN-LC和靜態鎖存器對SEU不免疫,輸出節點易受到影響。第7列為是否過濾上游組合電路傳播來的SET。從表2中可以看出,文獻[11,12,14,15],TMR和提出的結構均可以屏蔽組合邏輯中的SET。雖然提出的結構在晶體管數目上沒有優勢,延遲處于中等水平,但在同時抗SEU/SET的鎖存器中,功耗是最小的。PDP損耗與FERST相當,小于TMR、LCHR、LSEH-1、STI鎖存器。

表1 提出的鎖存器與已有的鎖存器的參數比較

另外,本文提出的鎖存器相比于已有的鎖存器的參數相對比較結果如表2所示。

鎖存器的參數相對比計算公式:

表2 提出的鎖存器相比于已有的鎖存器的參數相對比

從表2中可以看出,本文鎖存器的延遲、功耗和PDP下降的趨勢較明顯。其中,面積開銷平均增加了3.90%,延遲平均下降37.34%,功耗平均下降55.01%,PDP平均下降75.22%。

五、結論

本文提出了一種低功耗、全免疫的加固鎖存器。該鎖存器的內部節點和輸出節點不僅完全容忍SEU,而且還具有過濾從上游組合電路傳播過來的SET脈沖能力。HSPICE仿真實驗結果表明相比于TMR、FERST、LCHR、STI、LESH-1鎖存器,本文提出的鎖存器功耗平均55.01%,PDP平均下降了75.22%,延遲下降了37.34%。