動態隨機存儲器的故障溯源

2020-05-25 09:11:28TaeYeonOh

軟件和集成電路

2020年4期

Tae Yeon Oh

多種來源的漏電流和寄生電容會引起DRAM的故障,在DRAM開發期間,工程師需仔細評估這些故障模式,當然也應該考慮工藝變化對漏電流和寄生電容的影響。

從20nm技術節點開始,漏電流一直都是動態隨機存取存儲器(DRAM)設計中引起器件故障的主要原因。即使底層器件未出現明顯的結構異常,DRAM設計中漏電流造成的問題也會導致可靠性下降。漏電流已成為DRAM器件設計中至關重要的一個考慮因素。

DRAM存儲單元(如圖1(a))在電源關閉時會丟失已存儲的數據,因此必須不斷刷新。存儲單元在數據丟失前可存儲數據的時間,即保留時間,是DRAM的一個關鍵特性,保留時間的長短會受到漏電流的限制。

有兩種重要的漏電機制會影響DRAM的數據保留時間。

第一種是單元晶體管漏電。DRAM中的單元晶體管漏電主要由于柵誘導漏極泄漏電流(GIDL)(如圖1(b)),它是由漏結處高電場效應引起的漏電流。在負柵偏置下,柵極會產生一個耗盡區(N+漏極區),該耗盡區進而在區域中產生一個增強電場,這個電場造成的能帶彎曲則導致了帶間隧穿(BTBT)。此時,在柵極移動的電子和少數載流子可以穿過隧道進入漏極,從而產生不必要的漏電流。

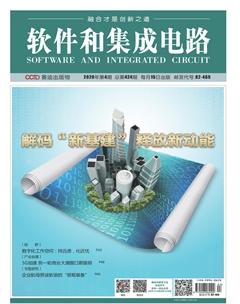

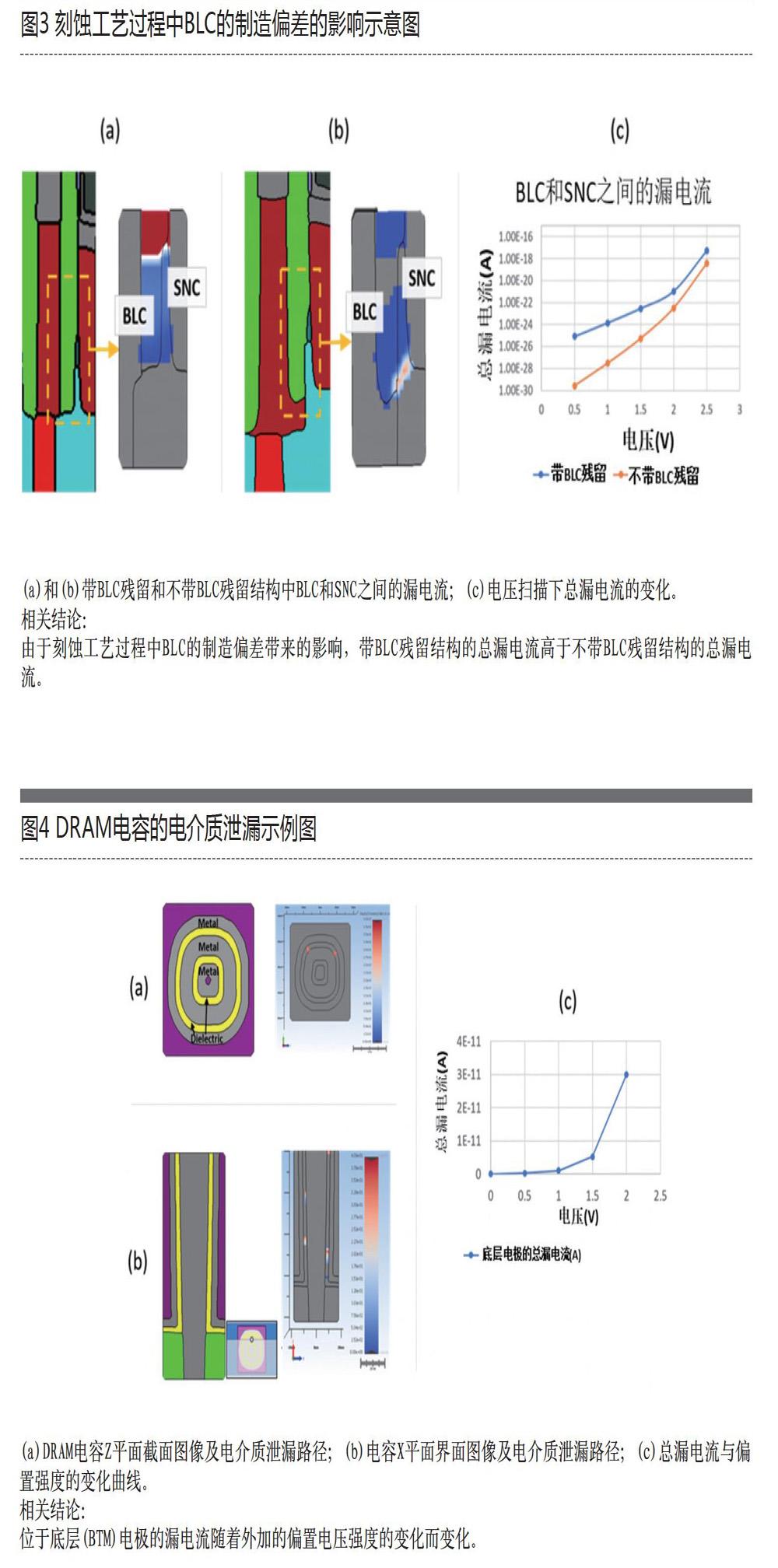

DRAM中的第二種漏電機制是位線接觸 (BLC)與存儲節點接觸(SNC)之間的電介質泄漏(如圖1(c))。電介質泄漏通常發生在電容內部,此時電子流過金屬和介電區域(如圖1(d))。當電子通過電介質層從一個電極隧穿到另一個電極時,便會引起電介質泄漏。隨著工藝節點的縮小,BLC和SNC之間的距離也在逐漸縮短,因此,這個問題正在變得愈發嚴重。……

登錄APP查看全文

猜你喜歡

山東冶金(2019年6期)2020-01-06 07:45:54

汽車維修與保養(2019年7期)2020-01-06 03:30:42

世界農藥(2019年2期)2019-07-13 05:55:12

汽車維護與修理(2016年10期)2016-07-10 08:17:41

銅業工程(2015年4期)2015-12-29 02:48:39

新疆鋼鐵(2015年3期)2015-11-08 01:59:52

汽車維修與保養(2015年12期)2015-04-18 07:51:49

汽車維修與保養(2015年6期)2015-04-17 03:31:50

汽車維修與保養(2015年2期)2015-04-17 01:30:34

汽車維護與修理(2015年2期)2015-02-28 12:15:39