SDH E1時隙可配幀格式及數據編碼的 設計與FPGA實現技術

池飛,武建鋒,何在民

(1.中國科學院 國家授時中心,西安 710600;2.中國科學院 精密導航定位與定時技術重點實驗室,西安 710600;3.中國科學院 時間頻率基準重點實驗室,西安 710600;4.中國科學院大學 電子電氣與通信工程學院,北京 101048;5.中國科學院大學,北京 100049)

0 引言

隨著通信、網絡技術的不斷進步,時間統一技術在SDH(synchronous digital hierarchy)光纖網絡中的應用越來越廣泛,但網絡中網元設備內部晶振的精度較低,網元守時能力差,SDH光纖網絡傳統業務和新業務亟需實現整個網絡的時間同步,以保證整個網絡時間的高度統一。E1通道可靠性、穩定性高,可應用于SDH光纖網絡的時間同步。E1是國際電聯(ITU-T)制定并由歐洲郵政與電信協會(CEPT)命名的數字傳輸系統一次群(即PCM30)標準,E1通道的物理及電氣特性符合CCITT(國際電報電話咨詢委員會)的ITU-G.703標準,我國也采用E1標準作為PCM系統和N-ISDN的基群[1-4]。E1通道在國防、電力、通信、交通等領域得到廣泛的應用,本文立足于用戶實際需求,基于FPGA(field programmable gate array)工具,設計并實現了時隙可配的SDH E1幀格式及HDB3(high density bipolar)數據編碼技術,通過實驗,仿真驗證其功能正確性[5-6]。

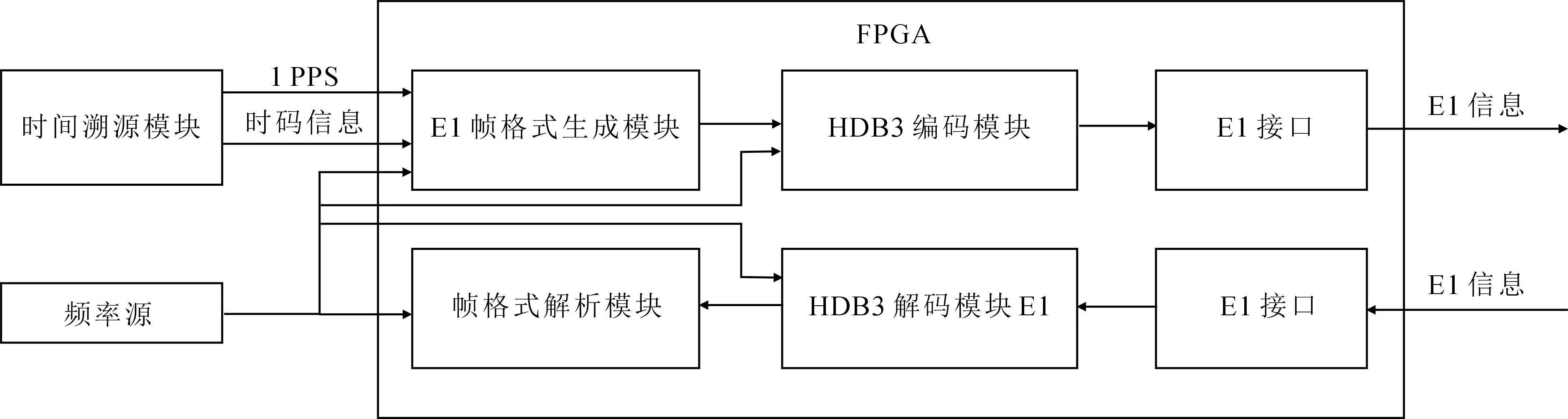

1 SDH E1時間同步系統設計

SDH E1時間同步系統總體框圖如圖1所示,FPGA集成相應的通信模塊,與時間溯源模塊進行通信,獲取時碼信息和1 PPS脈沖信號,同時外接10 MHz頻率源作為外頻標參考以驅動整個系統。FPGA系統用7位巴克碼信息作為幀頭來表示1 PPS以填充到對應時隙中,將其與時碼信息進行組合,并配置成E1通道所規定的幀格式,利用HDB3編碼模塊將二元碼變成適合在線路中傳輸的雙極性碼,最后通過E1通道將信息發送到下一個節點,SDH網絡中另一端接收E1幀格式信號,經過HDB3解碼,而后進行E1幀格式解析,從7位巴克碼幀頭中恢復1 PPS脈沖信號,即可在對端實現同步[7]。文中主要是設計并采用FPGA實現SDH E1線路中的幀格式生成和數據HDB3編碼兩個關鍵模塊,采用Modelsim和Signal Tap II仿真工具,驗證數據編碼和幀格式生成的正確性。

圖1 E1總體框圖

2 E1幀格式及HDB3編碼原理

E1線路是一條基于時分復用的數字鏈路,它的數據傳輸速率為2.048 Mbit/s,整個線路由8 000個E1幀構成,每個E1數據幀由256 bit數據位構成,這256 bit的數據位又分為32個時隙(TS),每個時隙又包含8 bit的數據,即:8 bit×32×8 000=2.048 Mbit/s,這樣,構成了整個E1線路[8-10]。我國和歐洲均采用2.048 Mbit/s的E1信號。

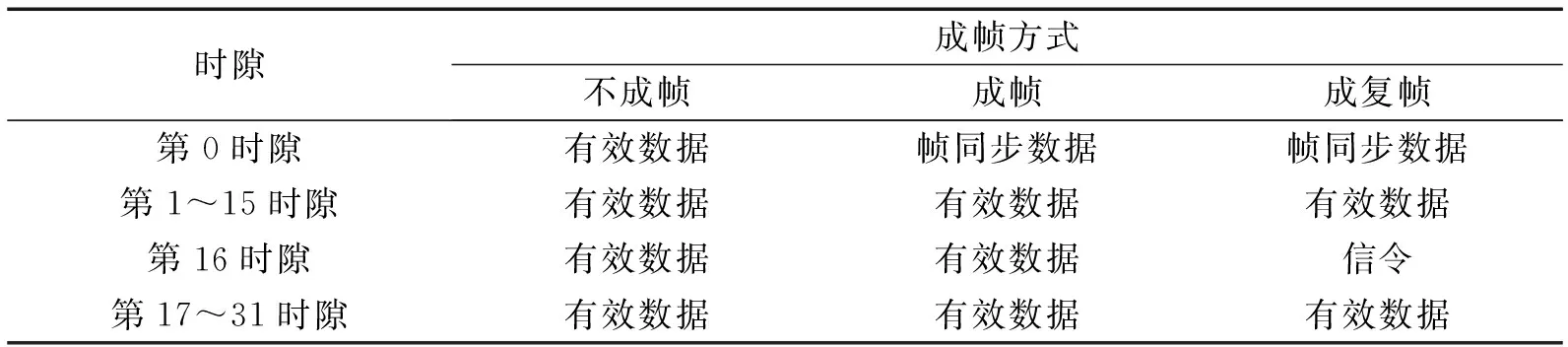

表1 E1幀格式

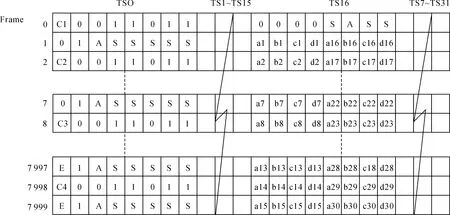

實際SDH網絡應用中,核心業務數據傳輸一般采用成幀格式或成復幀格式[11-13]。進行系統時間同步時,時碼信息傳輸可根據用戶需求,在TS1~TS31 31時隙中的任意一個時隙靈活配置,幀格式如圖2所示。

圖2 E1幀格式

E1系統中,當輸入信息被配置成規定的幀格式后,需要通過相應的編碼才能更好的在整個系統中傳輸。根據CCITT的建議,E1線路中采用HDB3編碼[14]。由于該編碼方式不含直流分量,低頻分量較少,同時含有定時信息。并且它改進了AMI碼中出現過長的連“0”串造成信號電平長時間不跳變引起提取定時信息困難的問題。

HDB3編碼規則如下:

①將二元碼中的“1”進行極性交替,即完成“+1”和“-1”交替出現,變成AMI碼;

②檢查碼中“0”的個數,當連“0”個數小于等于3時,HDB3碼與AMI碼一樣,+1與-1交替;

③當連“0”個數超過3時,將每4個連“0”化作一小節,定義為B00V,成為破壞節,其中V成為破壞脈沖,而B成為調節脈沖;

④V與前一個相鄰的非“0”脈沖的極性相同(這破壞了極性交替的規律,所以V成為破壞脈沖),并且相鄰V碼之間極性必須交替。V的取值為+1或-1;

《模擬電子技術》課程歷年來大多數的學生覺得學習難度大,一些概念與原理比較難懂,為了提高該門課程的教學效果,在教學過程中積極探索了基于“雨課堂+互聯網+PowerPoint”的在線混合式教學改革方法,不僅有利于了解學生的課前預習情況,也可以提高課堂的教學效果,大大改善了以往課堂教學沉悶的現象,還便于學生課后的復習,這種混合式的教學方法給予學生課前、課中、課后每個環節都有新的不同的體會與感受,并且充分的利用了智能手機的優勢,讓它更好地服務教學的方法,獲得了廣大學生的好評。

⑤B的可能取值可選0,+1或-1,以使V同時滿足④中的兩個要求;

⑥V碼后面的傳號碼極性要交替。

依據HDB3編碼規則,對二元碼“1000010000110000000011”進行編碼,其對應過程序列及最終HDB3編碼結果如表2所示。

表2 HDB3編碼結果

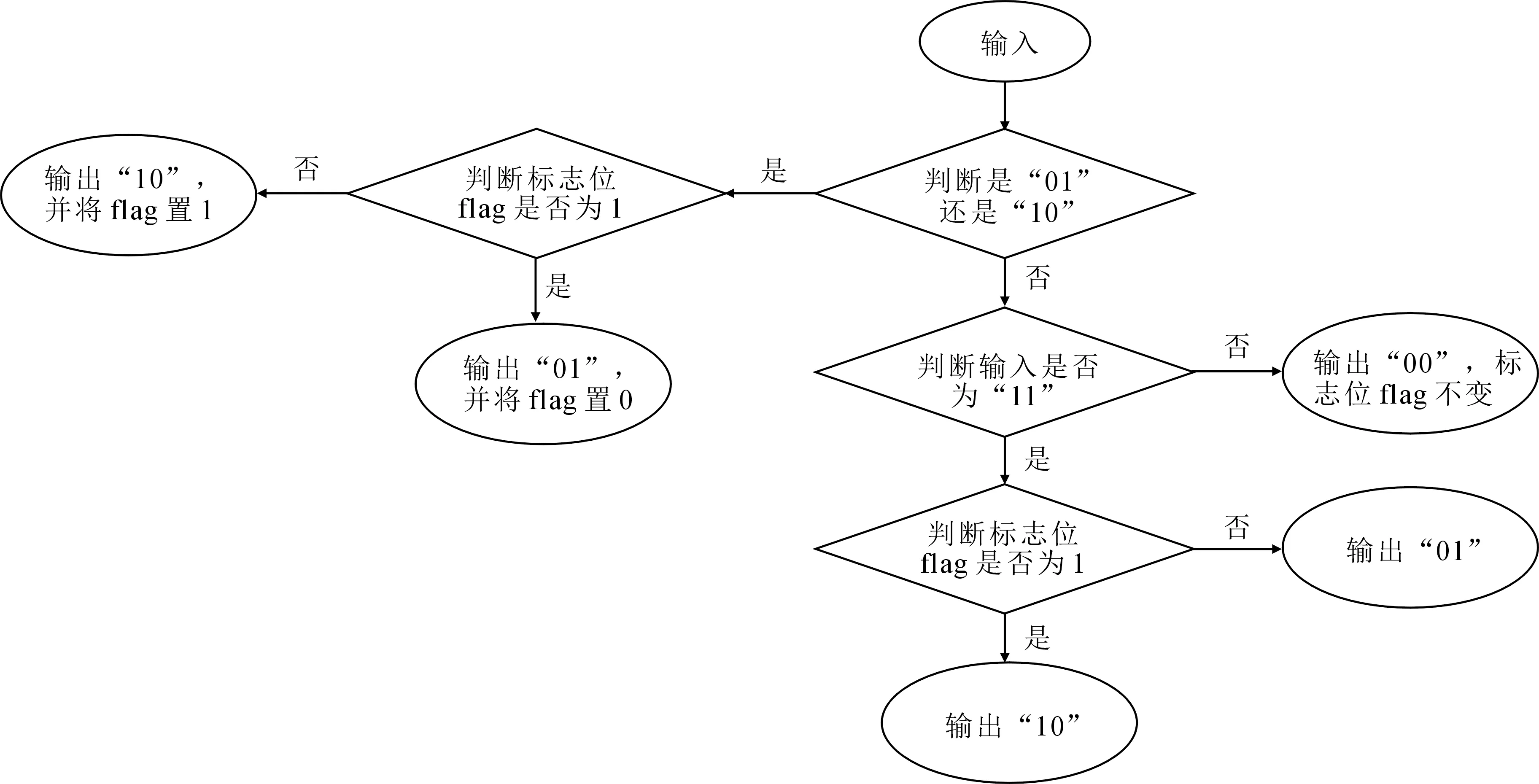

總體來說,對于HDB3編碼部分,可分為3個部分進行,包括:加“V”操作、加“B”操作、極性變換操作,其中的對應關系如表3所示。

表3 HDB3編碼碼型對應

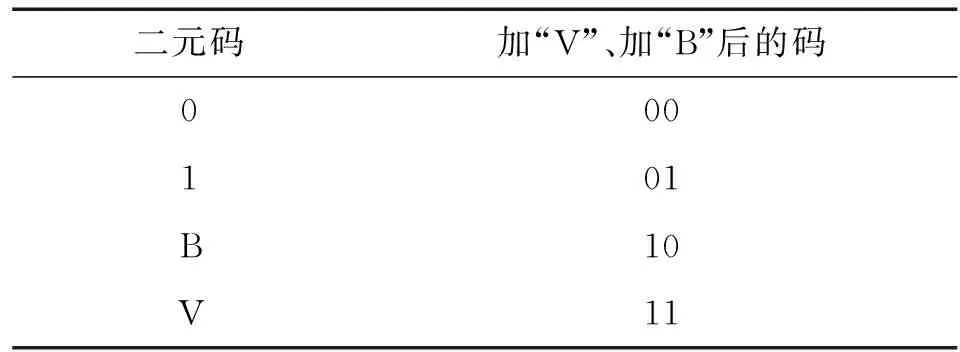

在加“V”操作中,主要是檢測二元碼中“0”的個數,一旦“0”的個數達到4個,就將第4個“0”變成破壞節“V”,具體的操作流程圖如圖3所示。

圖3 HDB3編碼加“V”操作流程圖

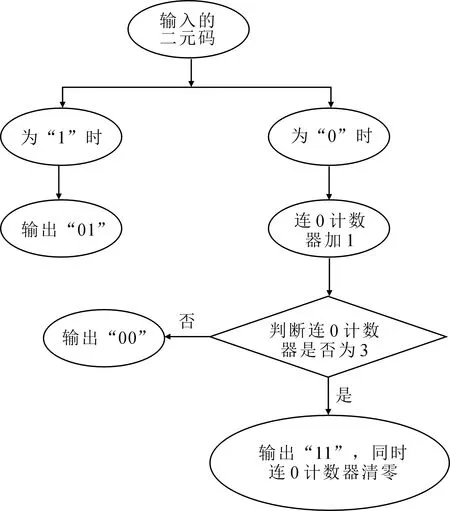

接下來就是加“B”操作,主要是檢測相鄰兩個“V”之間有奇數個非“0”還是偶數個非“0”碼,當非“0”碼個數為偶數時,將“V”前面的第3個“0”變為“B”,具體流程圖如圖4所示。

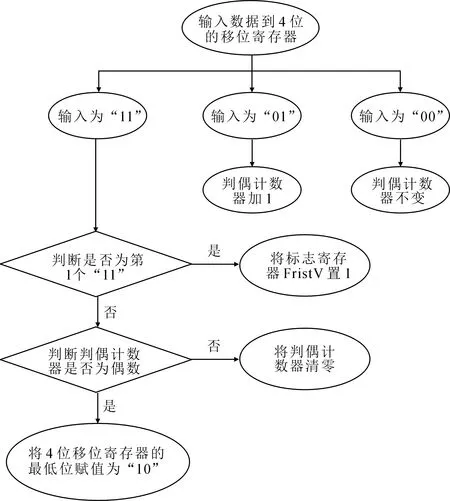

最后一部分為單雙極性變換,整體思想是滿足“V”的極性是正負交替的,同時滿足“1”和“B”構成的整體也是正負交替的,流程圖如圖5所示。

圖4 HDB3編碼加“B”操作流程圖

圖5 HDB3編碼極性變換流程圖

3 E1幀格式實現

本文采用成幀的方式,即第0時隙用來傳輸幀同步信息,其他31個時隙傳輸有效信息。此處的幀同步信息是由7位巴克碼“1110010”來表示,由1 PPS脈沖信號上升沿觸發巴克碼第1個碼片的產生,由于此處用100 MHz作為時鐘,故兩者同步偏差在10 ns以內。由于巴克碼是一種具有特殊規律的碼組,有尖銳的自相關函數,與隨機數字信息相區別,易于識別,故用巴克碼作為幀頭[15-18]。

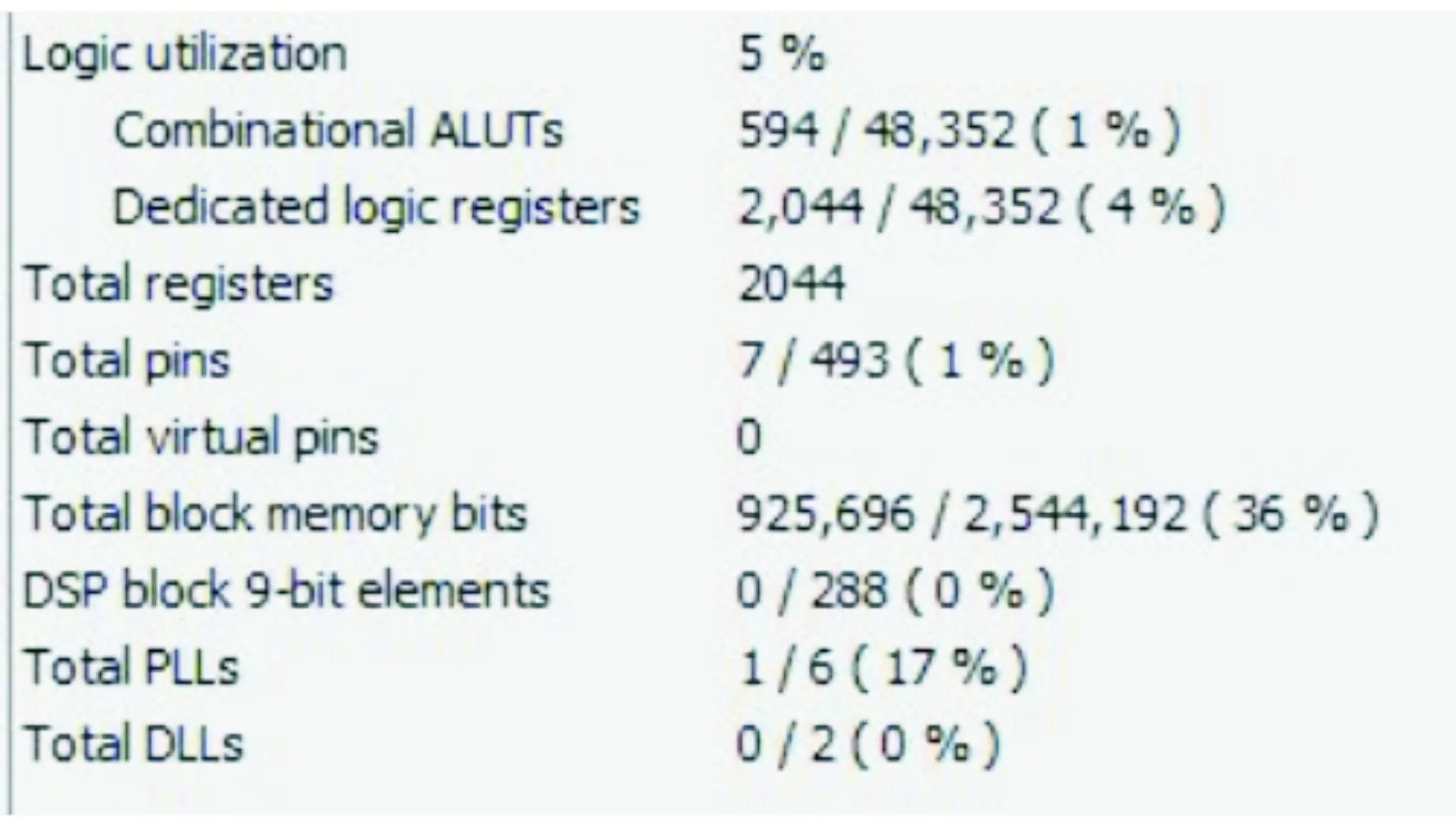

本工程采用Altera公司的EP2C8T144I8芯片,工作時鐘由本地晶振(10 MHz)通過片內的PLL倍頻、再經DDS模塊分頻產生,為SDH E1規定的2.048 MHz,對于幀格式生成部分,具體使用的邏輯資源以及片內資源使用情況如圖6所示。

圖6 幀格式生成所占用片內資源情況

為了增強時隙利用的靈活性,本設計給用戶提供了一個接口信號(時隙選擇信號)i_Ts_Sel,讓用戶根據自身需求以及時隙的利用情況去靈活分配1~31中任一時隙為所用。使用中,只需給i_Ts_Sel賦上1~31中任一值,系統就會按照要求將所要傳輸的數據填充到指定時隙。當用戶通過指令配置生效后,系統能夠很好將巴克碼作為幀頭填充到第0時隙,將輸入數據填充到用戶指令配置的時隙,以達到靈活配置的目的。o_Data為輸入信號,SlotCnt信號為時隙計數器,用來直觀辨別時隙的占用情況,o_Frame_Data為最終的E1時隙填充信號,展示完整的32個時隙。下面通過選擇第1時隙、第5時隙和第18時隙為例,利用FPGA的開發環境Quartus II軟件自帶的邏輯分析儀Signal Tap II進行仿真驗證。

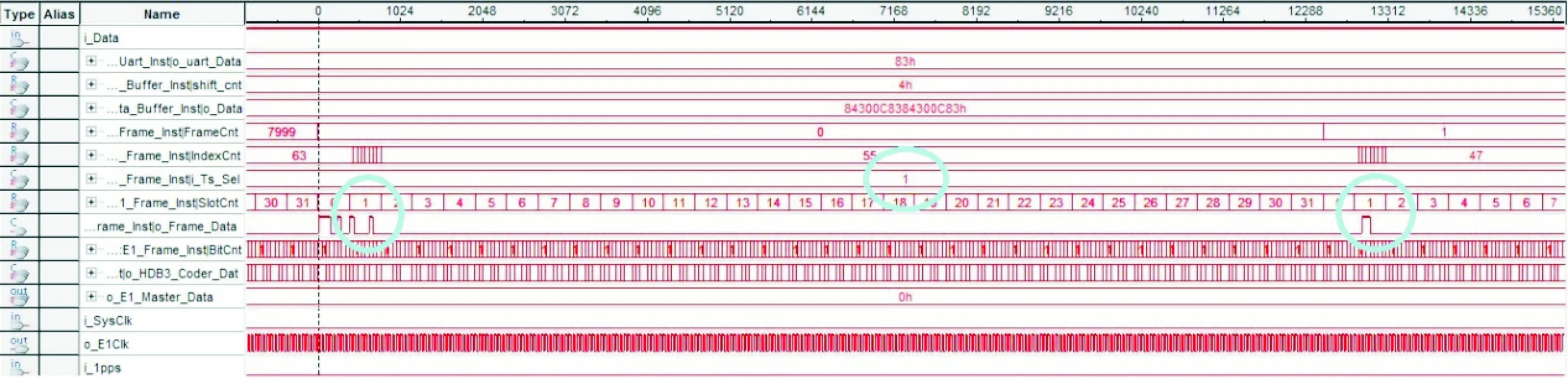

圖7和圖8為E1可配時隙幀格式。由圖7可以看到,當給時隙選擇信號i_Ts_Sel賦值為1,即選擇第1時隙時,根據時隙計數器SlotCnt可以清晰看到,輸出信號o_Frame_Data第1時隙的位置填充了相應的數據。

圖7 E1可配時隙幀格式(填充時隙1)

由圖8可以看到,當給時隙選擇信號i_Ts_Sel賦值為5,即選擇第5時隙時,輸出信號o_Frame_Data第5時隙的位置填充了相應的數據。

圖8 E1可配時隙幀格式(填充時隙5)

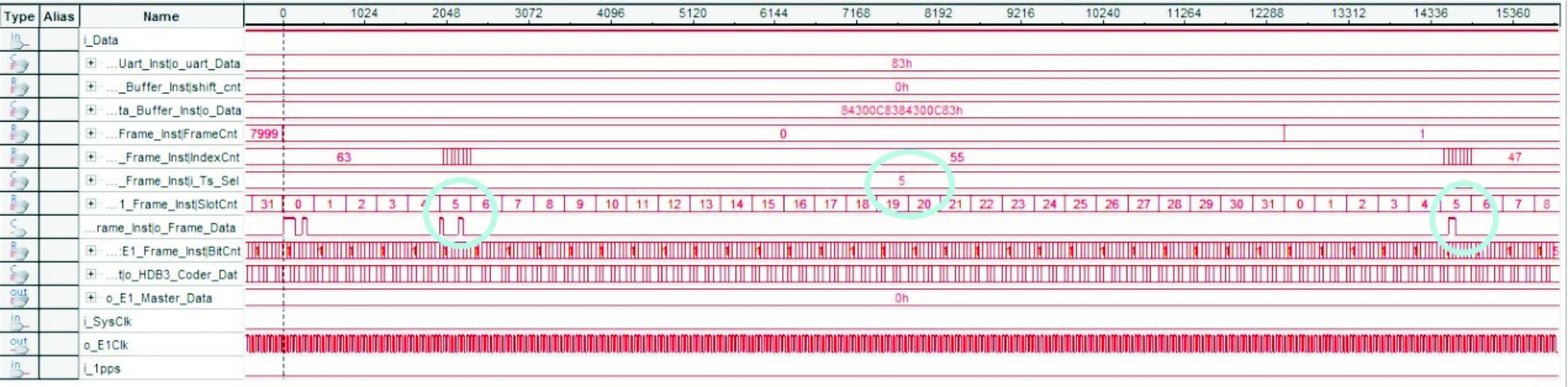

同理,當給時隙選擇信號i_Ts_Sel賦值為18,即選擇第18時隙時,輸出信號o_Frame_Data第18時隙的位置填充了相應的數據,如圖9所示。

圖9 E1可配時隙幀格式(填充時隙18)

4 HDB3編碼實現

由總體框圖的設計流程可知,數據經過E1幀格式的生成以后,需要對數據進行編碼,本系統采用的是HDB3的編碼方式。

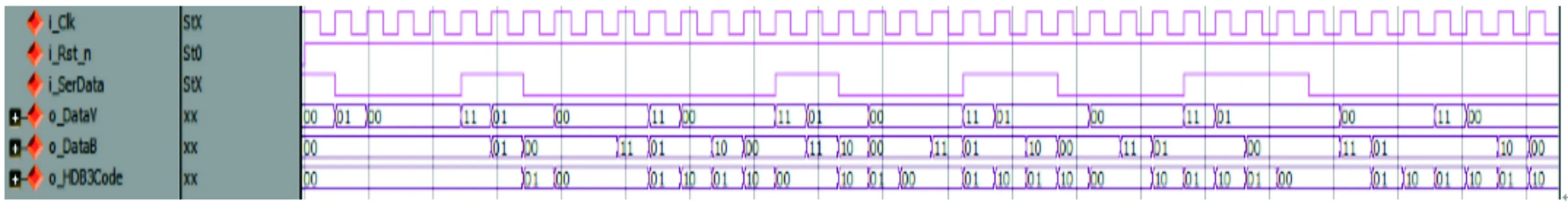

由于數字電路中只有“0”和“1”,無法傳輸“V”,“B”等字符,因此對編碼過程中出現的“V”,“B”,“+1”,“-1”進行事先標識,以便后期的處理與識別。HDB3編碼模塊主要實現的是對二元碼進行加“V”、加“B”和極性變化操作。本文將編碼模塊分成3步進行,在加“V”和加“B”兩步中,以“00”表示“0”,“10”表示“B”,“11”表示“V”,在極性變換中,以“10”表示“+1”,“01”表示“-1”,“00”表示“0”。以“100001100000000 110000111 0000111100000000111000100000100000011”為測試數據進行測試,數據中包含多種長連“0”出現的情況,具有普適性。

對于HDB3編碼部分,具體使用的邏輯資源以及片內資源使用情況如圖10所示。

圖10 HDB3編碼所占用片內資源情況

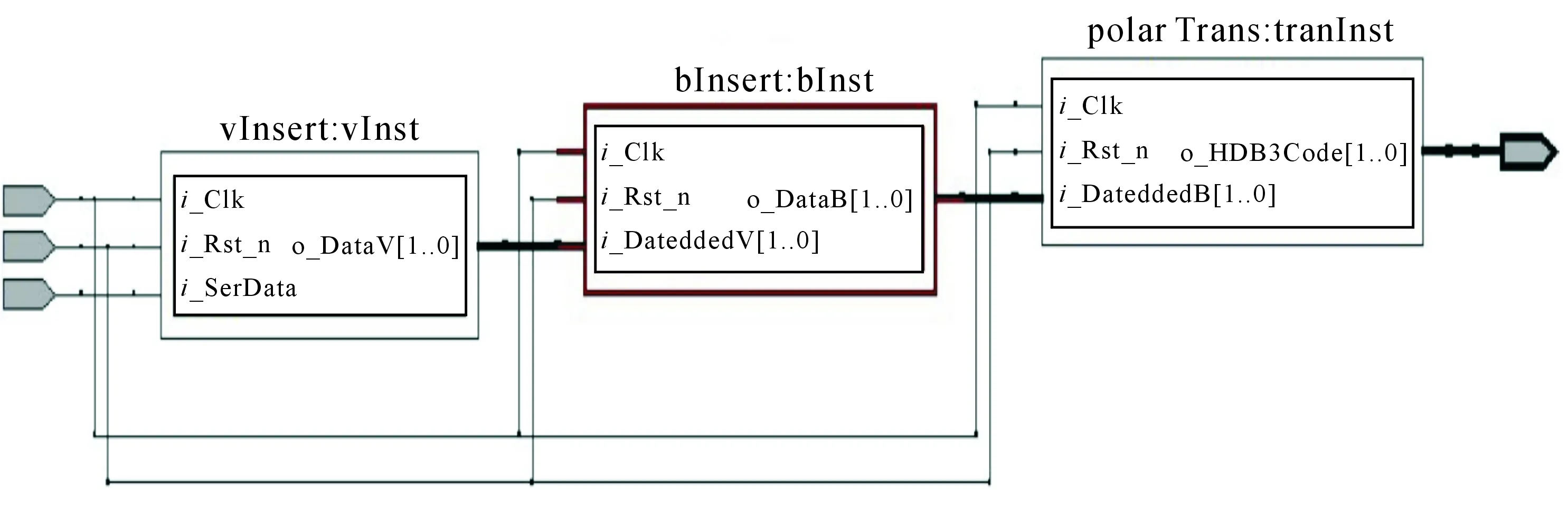

編碼的RTL流程圖如圖11所示,主要包含3個部分,其中,vInst為加“V”模塊,bInst為加“B”模塊,tranInst為極性變換模塊。

圖11 HDB3編碼RTL視圖

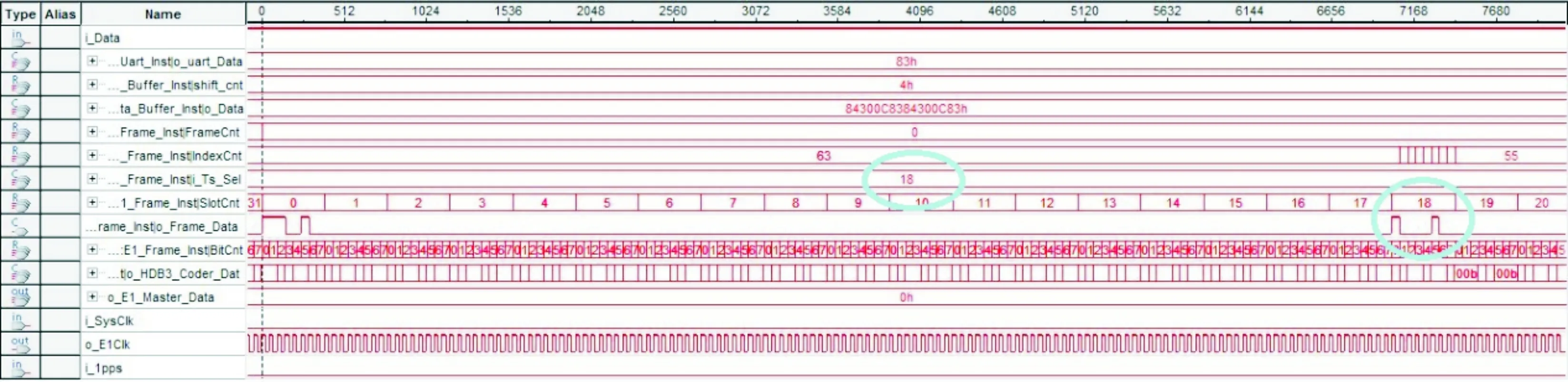

具體的仿真見圖12,此圖為Modelsim的后仿真截圖,由于時序裕量充足,未做時序約束。i_SerData為輸入信號,o_DataV,o_DataB和o_HDB3 Code分別為加“V”,加“B”,極性變換后的信號。根據編碼規則以及前面約定的標識,輸入的二元碼經過HDB3轉換后應該為“01 00 00 00 01 10 01 10 00 00 10 01 00 00 01 10 01 10 00 00 10 01 10 01 00 00 00 01 10 01 10 01 10…”,圖12仿真結果與之前理論推導結果一致,表明該編碼方式實現正確。

圖12 HDB3編碼仿真圖

5 測試結果分析

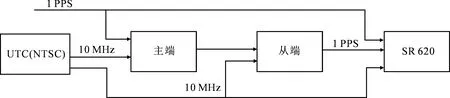

通過各模塊的仿真驗證無誤后,對整個E1時間同步設備進行測試,將主端設備連接上GNSS定時模塊輸出的1 PPS信號,同時連接上UTC(NTSC)輸出的10 MHz參考頻率,經過主端設備的處理后,生成滿足E1幀格式協議的信號[19-21]。該信號通過E1線路進行傳輸,當從端收到該信號后,對該信號進行解幀和解碼操作,進而復現出1 PPS信號。最后,將最開始主端源頭處的1 PPS和從端復現出來的1 PPS同時連接到SR620時間間隔計數器上進行測試(SR620時間間隔計數器的外參考頻標是UTC(NTSC)輸出的10 MHZ信號),從而測試出兩者的時間間隔數據。

圖13 測試流程圖

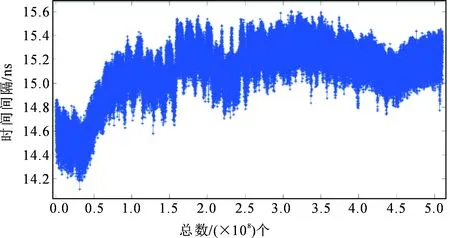

本次試驗測試,通過分時段采集了兩次數據。第1次的測試數據是從北京時間2018-01-19 20:37:57到2018-01-20 10:49:09,共采集了51 070個數據點;第2次的測試時間從北京時間2018-01-20 18:25:08到2018-01-21 11:16:41,共采集了60 694個數據點。

圖14是第1段測試采集到原始數據的繪圖,經過對數據的分析,計算得出均值為15.11 ns,標準差是0.24 ns。

圖14 測試結果圖1

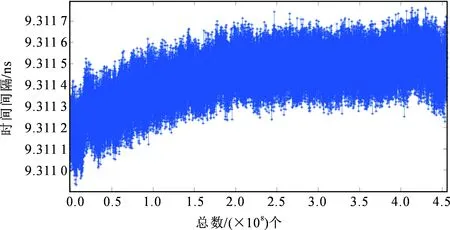

圖15是第2段測試采集到原始數據的繪圖,同理,經過對數據的分析,計算得出均值為34.094 6 ns,方差為0.120 6 ns。

圖15 測試結果圖2

通過在兩個不同的時間段對設備進行開關機試驗,得出以上兩個測試結果。鑒于E1的數據速率為2.048 Mbit/s,所以從端在檢測接收到的數據的時候,會存在(1/2.048)s的不確定度,大約為488 ns。因此在每次開關機的過程中(即每次上電的時候),會存在488 ns的不確定度。以上兩次的數據結果在該范圍內,說明設備功能健全。

6 結語

基于幀格式生成和HDB3編碼原理,設計時隙可配的SDH E1幀格式及數據編碼方案,并在FPGA上進行實現,通過實驗仿真驗證其功能。基于本文設計結果,SDH光纖網絡用戶在保證其語音、圖像等數據傳輸核心業務的同時,可根據信道特性和自身需求,通過軟件對E1幀格式中的時隙進行配置,使得時碼信息可占用E1幀格式31個時隙中的任意一個時隙,經過HDB3編碼實現時間同步信息在SDH光纖網絡中的傳輸,提高SDH光纖網絡時間同步信息傳輸的靈活性,為SDH光纖網絡通信性能的提升提供支撐,SDH光纖網絡E1通道時間同步具有重要的工程實用價值。