Verilog HDL編碼的綜合與優化

王 鵬,張玉峰,徐華結

(池州學院 集成電路設計與嵌入式應用研究中心,安徽 池州 247000)

1 引言

隨著微電子技術的發展,專用集成電路(ASIC)和用戶現場可編程門陣列(FPGA)的設計復雜程度的增加,邏輯電路系統的設計時間要求卻越來越短,傳統的原理圖設計方法已經不能滿足用戶的設計需要,而硬件描述語言形式化的方法不僅能夠準確、直觀的對電路進行建模仿真,而且極大的提高了復雜電路的設計效率.在設計過程中設計者使用verilog HDL作為對數字電路進行描述的輸入,綜合工具將verilog HDL所描述的RTL級電路在附加的約束條件下映射到目標工藝庫,輸出由工藝庫中的標準單元和互聯組成的門級網表.在設計過程中正確的理解運用verilog HDL代碼,不僅會影響綜合所得到的準確性,同時對電路的性能、面積功耗也起著至關重要的作用.

2 Verilog編碼與綜合網表的生成

2.1 Verilog HDL是一種用于描述數字邏輯電路的硬件描述語言,它可以從邏輯功能上對電路模型進行行為級的描述,也可以通過元器件之間的相互連接關系在結構上對電路模型進行描述.根據對電路模型描述的不同抽象級,verilog HDL可用于系統級(System)、算法級(Alogrithem)、寄存器傳輸級(RTL)、邏輯級(Logic)、門級(Gate)和開光級(Switch)設計.在設計的過程中硬件描述語言verilog HDL的風格與C語言等其他語言有相似之處,如if語句、case語句等與C語言十分相似,但實際上verilog HDL代碼所描述的對應的是實際的電路模型,同時一些非阻塞賦值等語句也是C語言沒有的,所以對Verilog HDL語句特殊方面的著重理解,將有益于生成希望得到的電路網表.

2.2 賦值語句

Verilog語言中阻塞賦值和非阻塞賦值的語言結構是需要重點掌握的方法之一,能夠完全正確的理解可綜合風格的賦值語句才能設計出符合要求的電路,清楚的理解阻塞賦值語句和非阻塞賦值語句含義的差別可以避免代碼綜合生成的電路中現競爭冒險現象.

表1 阻塞賦值與非阻塞賦值的比較

在綜合的過程中綜合工具對阻塞賦值和非阻塞賦值的處理方法不同,阻塞賦值在賦值過程中順序執行,在執行下一條賦值語句時就已經完成對右端對象的賦值,而對于非阻塞賦值是在執行過程中并不會立即賦值,需要在整個過程塊結束后才對所有變量完成賦值操作.如表1所示:

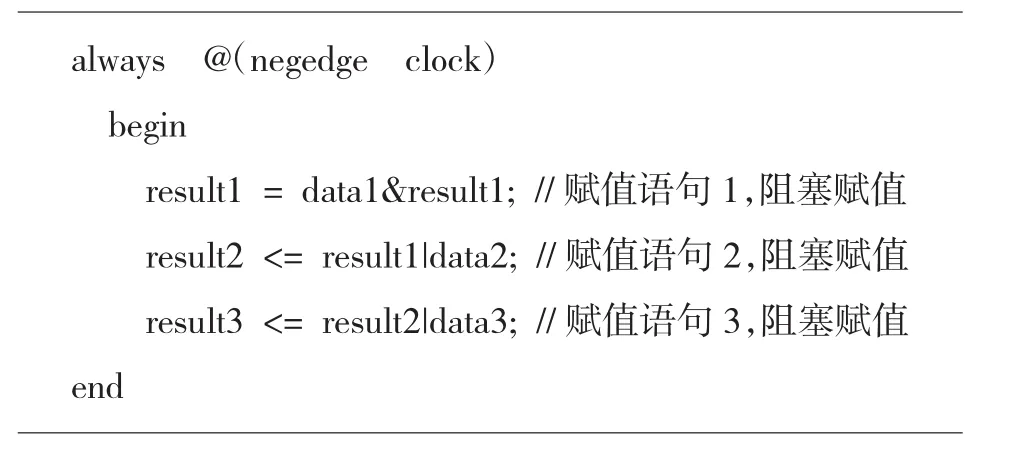

表1中有三條賦值語句,其綜合出的網表如圖1所示,always語句塊中三條賦值語句受下降沿時鐘clock控制,綜合生成三個下降沿觸發的觸發器,第一條賦值語句是阻塞賦值,將右邊data1&result1計算的值賦給左邊的result1,完成賦值語句后result1獲得新值,第二條賦值語句是非阻塞賦值將右邊的result1|data2值非給左邊的result2,第二條賦值語引用result1新值,所以result2觸發器的輸入端通過邏輯門連接到result1觸發器的數據輸入端,第三條賦值語句是非阻塞賦值,將右邊result2|data3的值給左邊的result3,因為第二條賦值語句是阻塞賦值,其result2值會在語句塊結束時才完成賦值,所以賦值語句三中使用的仍然是其原值,所以在綜合過程中result3觸發器的數據輸入端通過邏輯門連接在result2的數據輸出端.

圖1 賦值語句綜合出的網表

對三條賦值語句對比可以看出,阻塞賦值和非阻塞賦值所綜合出的網表有所區別,在verilog的代碼編寫過程中充分的理解賦值語句將有效的避免生成錯的電路網表,同時在運用賦值語句中一些注意要點可以有效的解決在綜合后出現的冒險競爭問題,如表1中出現的一個always語句塊中同時出現阻塞和非阻塞語句在代碼編寫中應盡量避免,可以將它分別寫在兩個always語句塊中.

2.3 if、case語句

在verilog HDL中的條件選擇語句有if語句和case語句,if語句是用來判斷所給的條件是否滿足,根據判斷結果進行二選一的操作,而case語句是多分支選擇語句,在實際問題中遇到多種選擇時,可以使用case語句進行選擇.不過這兩種語句在編寫代碼時應注意對其中的每條分支進行賦值,不當的編碼其綜合過程中可能會推導出不希望生成的鎖存器.

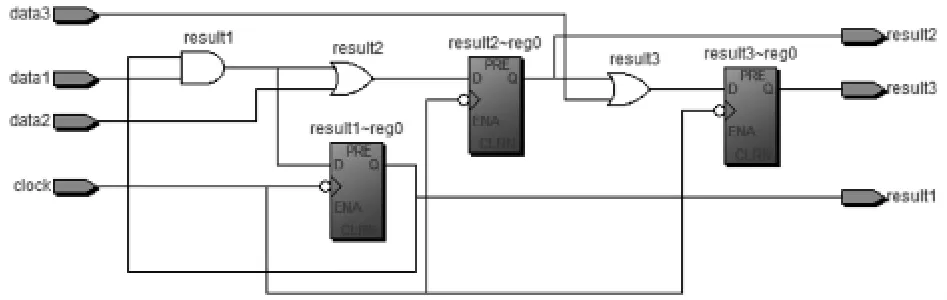

表2中的第一個編碼的if語句中只當a=1時,對 q進行了賦值將d的值賦給q,而a=0時編碼中沒有寫出q該取什么樣的值,這時候會默認變量保持原值生成一個鎖存器,如第一個代碼右邊生成的電路圖所示.如果設計者希望當a=0時將0的值賦給q,在第二代碼中加上一個else語句,其生成的電路圖如第二個代碼右邊電路所示,這時電路就不會生成鎖存器.

表2 if語句生成鎖存器

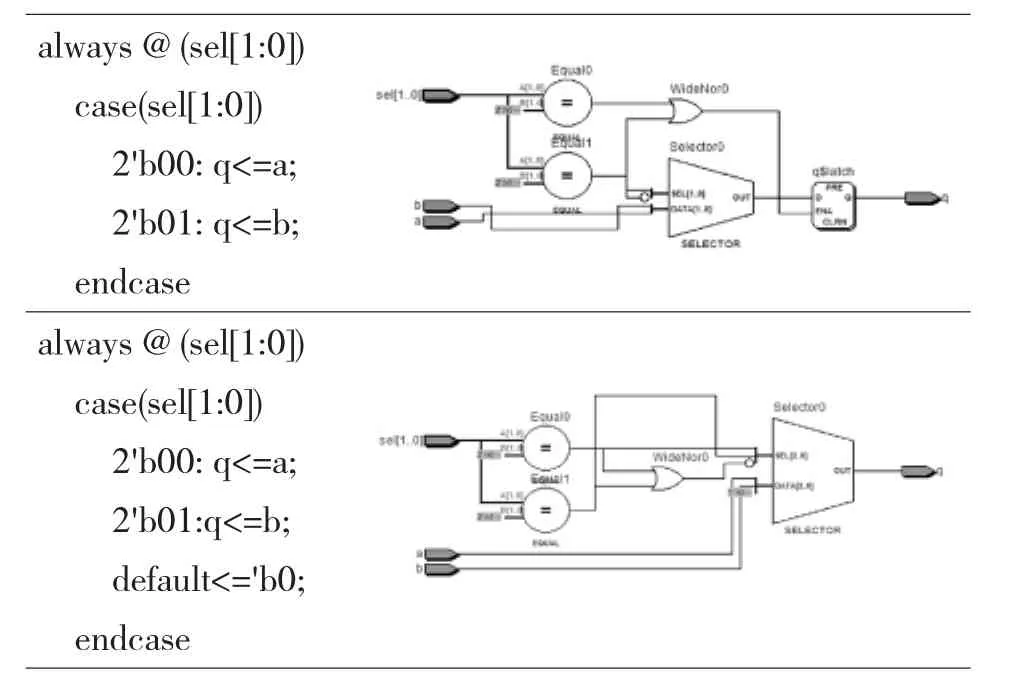

verilog HDL中case語句是多分支的選擇語句,在編碼時與if語句類似,表3中的第一個case語句當sel取00和01時,分別將a和b的值賦給q,當sel取00和01以外的值10和11時,并未告訴q應該賦予何值,這時會默認保持原值生成一個鎖存器,如果不希望生成多余的鎖存器,可以在case語句中加入default項避免在電路中生成不必要的鎖存器,如表3中第兩個代碼所生成的電路所示.

表3 case語句生成鎖存器

3 verilog編碼與網表性能的優化

Verilog HDL的編碼的準確性影響著綜合所生成網表的功能的正確描述,同時不同的編碼方式和結構所綜合出來的網表的性能也不盡相同,通過對verilog HDL代碼的優化可以實現優化綜合所生成的網表,根據不同的電路需求在面積、功耗、性能間進行平衡,以完成最終的設計需求.

下面以流水線設計(pipe-line)為例,通過pipe-line的設計方法對電路的性能和所使用邏輯資源進行優化和權衡.在verilog HDL對復雜的組合邏輯電路和時序電路描述過程中,工具能自動的綜合生成電路并對電路的進行全面驗證,但對于一些對時鐘速度要求很高的電路和一些特殊的電路,如CPU的指令讀取、執行和高性能的DSP系統設計其結構還是需要設計者來定奪,而pipe-line技術被廣泛的采用在這些電路的設計中.pipe-line設計是將規模和層次較多延時較長的組合邏輯電路分成幾個部分,在每個部分之間插入寄存器暫存兩個寄存器中間組合邏輯電路產生的數據,而k級流水線就是在組合邏輯電路的起始端到輸出端之間插入K個寄存器.

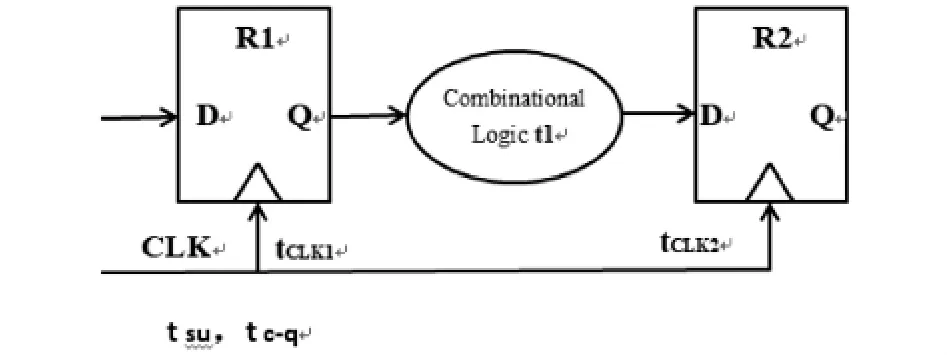

圖2在電路中可以達到的時鐘最快周期與建立時間(tsu)、組合邏輯電路延遲(tcomb)和寄存器輸出響應時間(tc-q)有關,不考慮時鐘抖動(skew)等因數的情況下,時鐘周期可以達到的時間T的表達式如下:

建立時間(tsu)、寄存器的延遲(tc-q)相對與組合邏輯電路的延遲時間(tcomb)較小,若設:t1comb為20t,tsu和tc-q分別為5t和3t,則圖2時鐘可以達到的最快周期為T>20t+5t+3t=28t.

圖2 正常結構的電路圖

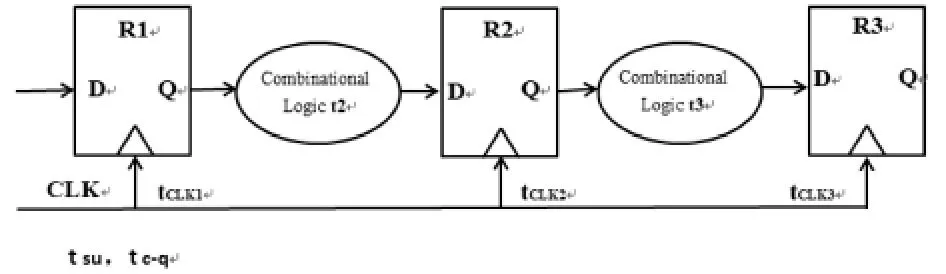

采用pipe-line結構在圖3的組合邏輯電路t1comb中插入一個寄存器,將組合邏輯電路t1comb分成t2comb和t3comb時延分別為8t和12t如圖3所示,此時電路中時鐘可以達到的最快周期為 max{tc-q+tsu+t2comb,tc-q+tsu+t3comb},T>max{16t,20t}.

圖3 采用pipe-line結構設計圖

通過對比采用pipe-line結構的設計在電路的性能上得到了提升,付出的代價是增加了一個寄存器,在高性能的電路系統面積相對寬裕的情況下,對一些時序緊張的路徑采用pipe-line結構設計是一種重要的方法.

4 結語

通過對verilog HDL的編碼和綜合過程的研究和理解,能夠有助于設計者設計出正確的邏輯功能的電路,避免在設計過程中綜合出與設計意圖不相符的電路網表,同時通過對verilog HDL編碼結構的調整能夠對生成的網表進行優化達到電路系統設計要求,縮短設計周期提升設計效率.