基于BP神經網絡的CPU電壓噪聲預測

李亞光

(1.中國科學院上海微系統與信息技術研究所,上海200050;2.上海科技大學信息與技術學院,上海201210;3.中國科學院大學北京100049)

隨著現代CPU和SOC的集成度的增長,功耗密度已經成為了一個主要問題[1]。另一方面,為了降低功耗密度過大的問題,降低CPU供電電壓已經成為了不可避免的趨勢[2-3]。但是同時,由于低電壓的趨勢,晶體管安全工作的閾值電壓范圍開始變小[4]。這將導致潛在的電壓噪聲很有可能使晶體管工作在安全工作的閾值電壓以下,從而引起CPU/功能模塊的異常工作,這種情況被稱為電壓緊急情況(Voltage Emergency)[5-7]。因此,低電壓的趨勢使得,CPU電壓噪聲預測變的尤為重要。

傳統的電壓噪聲預測,首先需要建立精細的CPU供電網絡物理模型,然后進行RTL層面仿真。但是整個過程不僅涉及到復雜的物理建模,RTL層面仿真時計算復雜度也大[8]。另外,最近有一些基于片上電壓傳感器的電壓噪聲預測方法[9]:利用訓練數據中體現出來的數據相關性的特性,提出了一種基于貝葉斯方法進行片上電壓噪聲預測的方法[5]。利用了CPU供電網絡物理相關性的特性,提出了一種基于Group-lasso和SVM的機器學習式的電壓噪聲預測方法。這兩種方法都基于片上電壓傳感器和電壓噪聲數據的相關性進行了CPU電壓噪聲的電壓預測。

與此同時,神經網絡近些年來在各個領域發揮著巨大的作用[10],例如在模式識別[11],自然語言處理[12-13]等領域。通過采集一定量的訓練集和調節網絡的參數結構,神經網絡,如BP神經網絡,卷積神經網絡等,就能夠有效的學習到數據中潛在的模型,從而進行相應功能的預測。本文探討了利用神經網絡進行CPU電壓噪聲預測的潛在可能性。區別于傳統的方法,該方法一方面避免了CPU供電網絡精細的物理建模過程,另一方面也減少傳統RTL仿真的復雜度。區別于[5,9]本文使用的方法,并不需要利用片上電壓傳感器和電壓噪聲數據的相關性,而是利用神經網絡的方式探討了CPU功能模塊功耗和CPU電壓噪聲預測之間的潛在可能性。

1 CPU供電電壓網絡分析

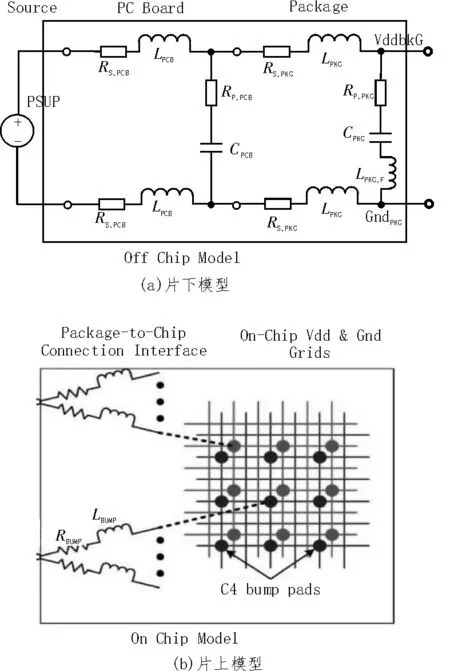

CPU的供電網絡可以被建模成由RCL(電阻電容電阻)組成的網絡[8],通常分為片下供電網絡和片上供電網絡,如圖1所示。其中片下供電網絡包括由PC板和封裝引入的RCL成分。片上供電網絡包括由封裝與芯片互連和芯片供電網格引入的RCL成分。完成片上和片下的供電網絡建模和調參之后,傳統的電壓噪聲分析通過RTL層面仿真得到實際的電壓噪聲。但是事實上,在構建CPU的供電網絡時,不僅需要構建相應的RCL結構(見圖1),也需要反復調節參數,其模型才足夠精確。另外在進行RTL層面仿真時,由于需要進行精細的仿真,因此其耗時也較大。

但是事實上,對于給定的CPU供電網絡,其RCL參數都是特定的,事實上我們可以嘗試利用神經網絡來學習給定的CPU供電網絡的RCL特性,從而避免CPU供電網路的復雜的物理建模過程。另一方面,如果神經網絡已經學習到了給CPU供電網絡的RCL特性,那么我們就可以通過給定一定的輸入向量,讓其進行CPU電壓噪聲的預測。具體來講,我們可以通過合理地構建訓練集(訓練特征集和訓練目標集),讓神經網絡學習CPU供電網絡的特性,從而進行CPU供電網絡的電壓噪聲預測。

圖1 CPU的供電網絡

通過對CPU由于CPU的供電網絡只包含RCL成分,因此CPU/功能模塊的瞬時功耗對CPU的供電網絡的影響應有如下兩個特點:

1)持續性:由于CPU供電網路中容性和感性器件(電容和電感)的存在,瞬時功耗引起的電壓噪聲不僅不會隨著瞬時功耗的消失而立即消失,反而會持續一段時間。所以過去的瞬時功耗對當前的電壓噪聲有影響。

2)有限性:過去某個瞬時功耗對電壓噪聲的影響不會影響未來所有的電壓噪聲,如果時間間隔足夠久,那么其影響應當降為零。所以雖然過去的瞬時功耗對當前的電壓噪聲有影響,但是并不是所有的過去瞬時功耗都對當前的電壓噪聲有影響。所以可以利用有限個過去和當前的瞬時功耗去預測當前的電壓噪聲。

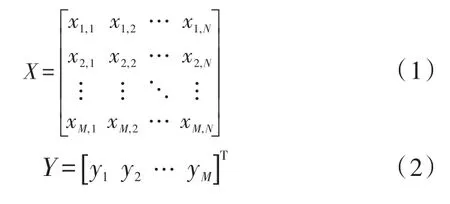

基于對CPU電壓傳遞網絡特性的分析,即瞬時功耗對于電壓噪聲影響的持續性和有限性,我們可以將有限個過去和當前的瞬時功耗作為一個訓練特征樣本,將當前的電壓噪聲作為相應的訓練目標樣本,同時采集多組訓練數據,以便于神經網絡來學習CPU供電網絡的特性,從而進行電壓噪聲預測。

2 BP神經網絡

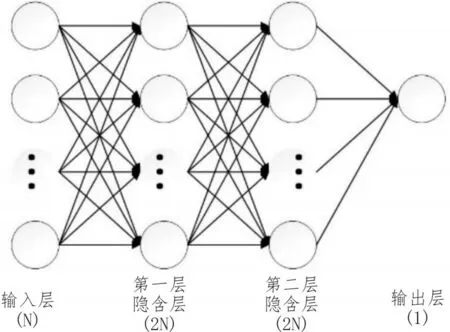

BP(Back Propagation)神經網絡的結構一般包含輸入層,隱含層和輸出層,如圖2所示。本文根據部分1的分析,構建了用于適合電壓噪聲預測的神經網絡結構:由于當前的電壓噪聲不僅與當前的負載有關,還有過去的負載有關,所以本文嘗試了4層的BP神經網絡:輸入層為N個節點,表示過去和當前的N個功耗;第一層隱含層為2N個節點;第二層隱含層為N個節點;輸出層為1個節點,表示需要預測的當前電壓噪聲。顯然模型的精度會受到N的影響,關于N的取值將在實驗部分討論。

圖2 BP神經網絡

3 數據獲取和訓練集構建

本文首先通過軟件仿真獲得原始的電壓噪聲數據,然后將原始數據轉換成用于神經網絡學習的訓練集。

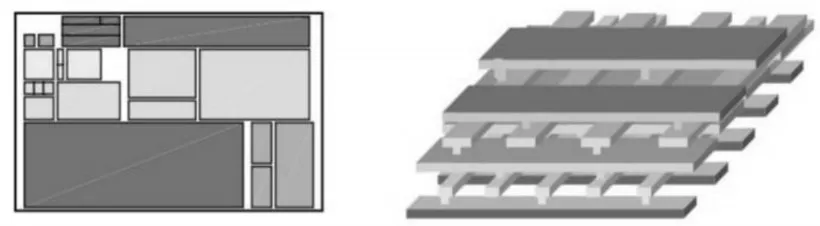

圖3 設計的芯片和片上供電網絡

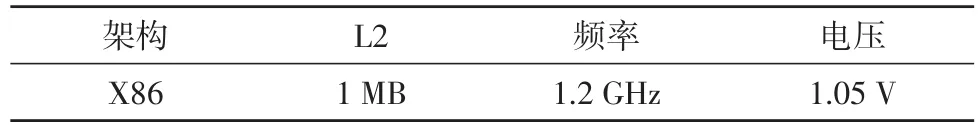

原始數據獲取包括系統層面的仿真,CPU/功能模塊的功耗仿真和RTL級Spice電壓噪聲仿真。第一步:本文通過系統級Gem5[14]仿真軟件,以CPU2006[15]中部分程序作為測試程序,獲得了程序運行時在X86架構下CPU的系統層面參數。Gem5詳細配置如表1所示。第二步,將系統運行時的系統層面參數作為輸入,利用McPAT[16]軟件仿真,獲得了CPU/功能模塊的實際功耗。第三步,根據得到的實際功耗,利用由[17]中修改的電壓供電網絡,通過Spice仿真獲得了CPU電壓供電網絡的實際電壓噪聲,仿真間隔為10 ns。軟件平臺基于Ubuntu,i7-4790U,32G。本文仿真的CPU共包含24個功能模塊,總面積為17.91 mm2,如圖3中左圖所示。片上的供電網絡為32 nm工藝下的5層供電網格,如圖3中右圖所示。實驗中選取了部分具有代表性的供電網格點的功耗值作為訓練特征集和Spice仿真電壓作為訓練目標集,并以此來完成BP神經網絡的訓練和預測。

表1 Gem5配置文件

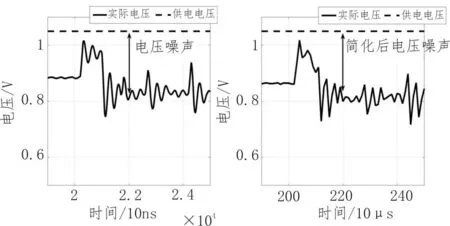

本文將原始數據獲取部分第二步中獲得的CPU/功能模塊的過去和當前的N個功耗數據作為一個訓練特征樣本,并且取M個樣本數據作為一個訓練特征集,如公式(1)中X矩陣,其中每一行代表一個訓練樣本,共M行。為了加速神經網絡的訓練速度,我們將第三步中獲得電壓噪聲,以1 μs為一個時間間隔(即Spice中仿真數據每100個點為一個時間間隔),取該時間間隔中,電壓噪聲最大點作為一個電壓噪聲的訓練目標,即該時間間隔中最壞情況的電壓噪聲作為訓練目標,如圖4所示。并取M個與相應訓練特征對應的訓練目標,如公式(2)所示,其中電壓噪聲定義為供電電壓與實際電壓的差值。本文在Matlab中實現了用于電壓噪聲預測的BP神經網絡。為了避免過擬合,本文用在實驗時,采用了5-fold交叉驗證。

圖4 電壓噪聲與訓練特征的產生

4 實驗結果

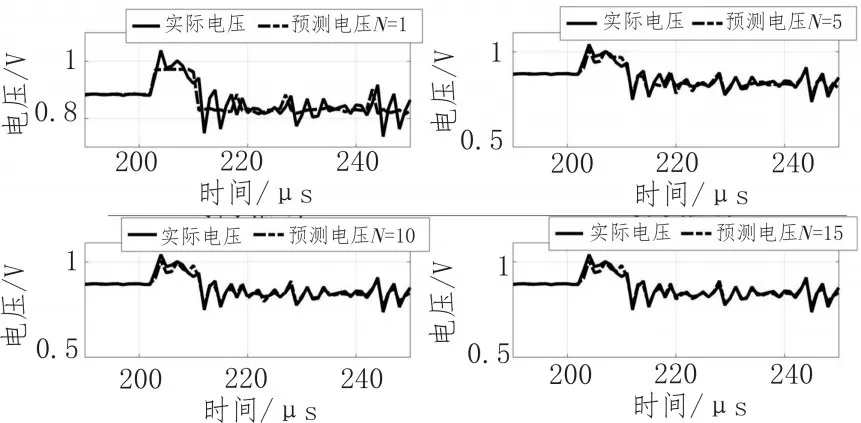

圖5 訓練結果樣本

圖5顯示了神經網絡預測所得的部分預測結果樣本。從圖片中可以發現,隨著N的增加預測電壓曲線與實際電壓曲線越來越接近。

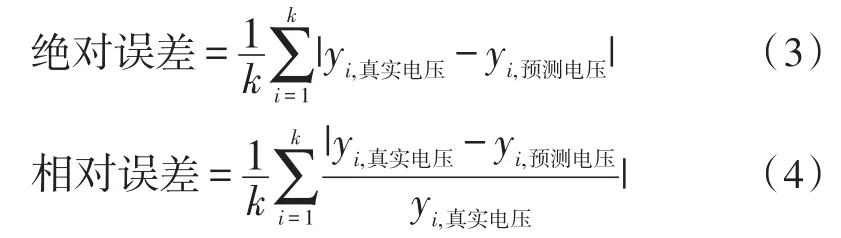

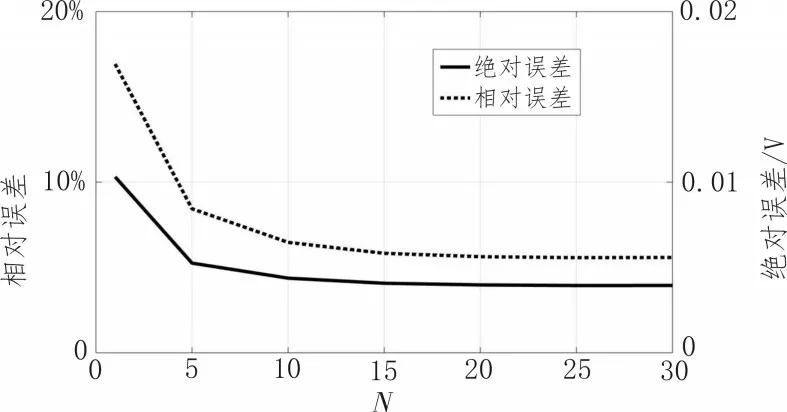

圖6展示了基于神經網絡模型電壓噪聲預測的準確度。當N=1時,電壓噪聲預測的絕對誤差為16.9 mV,相對誤差為10.3%。隨著N的逐漸增加,模型的準確度有所增加,但是當N大于10之后,模型的準確度的增加程度變得平緩。當N=15時,電壓噪聲預測的絕對誤差(見公式(3),其中k表示用于驗證的數據集的樣本數目)為3.9 mV,相對誤差(見公式(4))為5.5%。可見,增加N的數量確實對于CPU的電壓噪聲預測有幫助,并且利用BP神經網絡能夠準確的完成CPU的電壓噪聲預測。

圖6 模型準確度

5 結 論

低電壓趨勢,使得由電壓噪聲可能造成的電壓緊急情況變的尤為突出,因此CPU電壓噪聲預測很重要。與傳統的方法相比,本文中提到的基于BP神經網絡的電壓噪聲預測方法,一方面不僅可以避免精細的物理建模過程,另一方面還可以減少RTL層面仿真的復雜度。數據實驗結果表明,BP神經網絡完成的電壓噪聲預測能夠達到絕對誤差為3.9 mV,相對誤差為5.5%的準確預測。