一種基于片同步技術的高速ADC與FPGA互連方法

韓 琦 葛 飛 梁圣杰 張之卓

北京航天自動控制研究所,北京100854

在數字中頻接收機中,為適應電子設備小型化、低功耗設計且具有較寬的頻帶覆蓋和較高靈敏度的需求,系統經常使用單片多通道的高速ADC組建多通道采樣處理平臺。如AD公司的AD9653采樣器為4通道16位125Msps高速同步采樣器,可適用于多通道同步采集系統的設計,其中芯片接口使用8對高速串行差分線傳輸采樣數據,每對差分線最高傳輸速率高達1Gbps。在如此高的數據傳輸速率情況下,即使保證ADC各通道串行數據與隨路采樣時鐘的走線嚴格等長,采用傳統的ADC與FPGA數據接口互連方式也將無法實現穩定可靠的數據接收。基于上述原因,Xilinx公司在Vertex4系列FPGA之后引入了片同步技術(ChipSync),通過采用此技術在FPGA內部設計同步調整模塊,可實現調節采樣時鐘處在數據的最佳采樣位置,以保證數據采樣的同步性和穩定性,從而解決高速ADC和FPGA之間高速數據傳輸的問題。

文獻[1-2]提出對ADC輸入的串行數據進行延遲調整以達到最佳采樣位置的方法,但在ADC進入輸出采樣數據模式之前,需要事先發送一連串的訓練序列用于對比判決,以此控制串行數據位延遲調整至采樣時鐘的最佳采樣位置,而控制輸出發送訓練序列的格式和輸出采樣數據之間的模式切換,需要FPGA增加SPI接口的控制邏輯對ADC進行發送命令來完成,由此增加了FPGA的邏輯復雜性。

提出了一種在FPGA設計中對ADC輸入的采樣位時鐘進行自適應延遲調整來補償采樣位時鐘的內部走線延時,將采樣時鐘調節至數據的最佳采樣位置的方式,不需要對ADC輸出發送訓練序列模式和輸出采樣數據模式的切換控制,去除了FPGA與ADC之間的SPI接口數據交互,大大降低了FPGA的設計復雜度,提高了系統可靠性。

1 高速ADC和FPGA互連設計整體方案

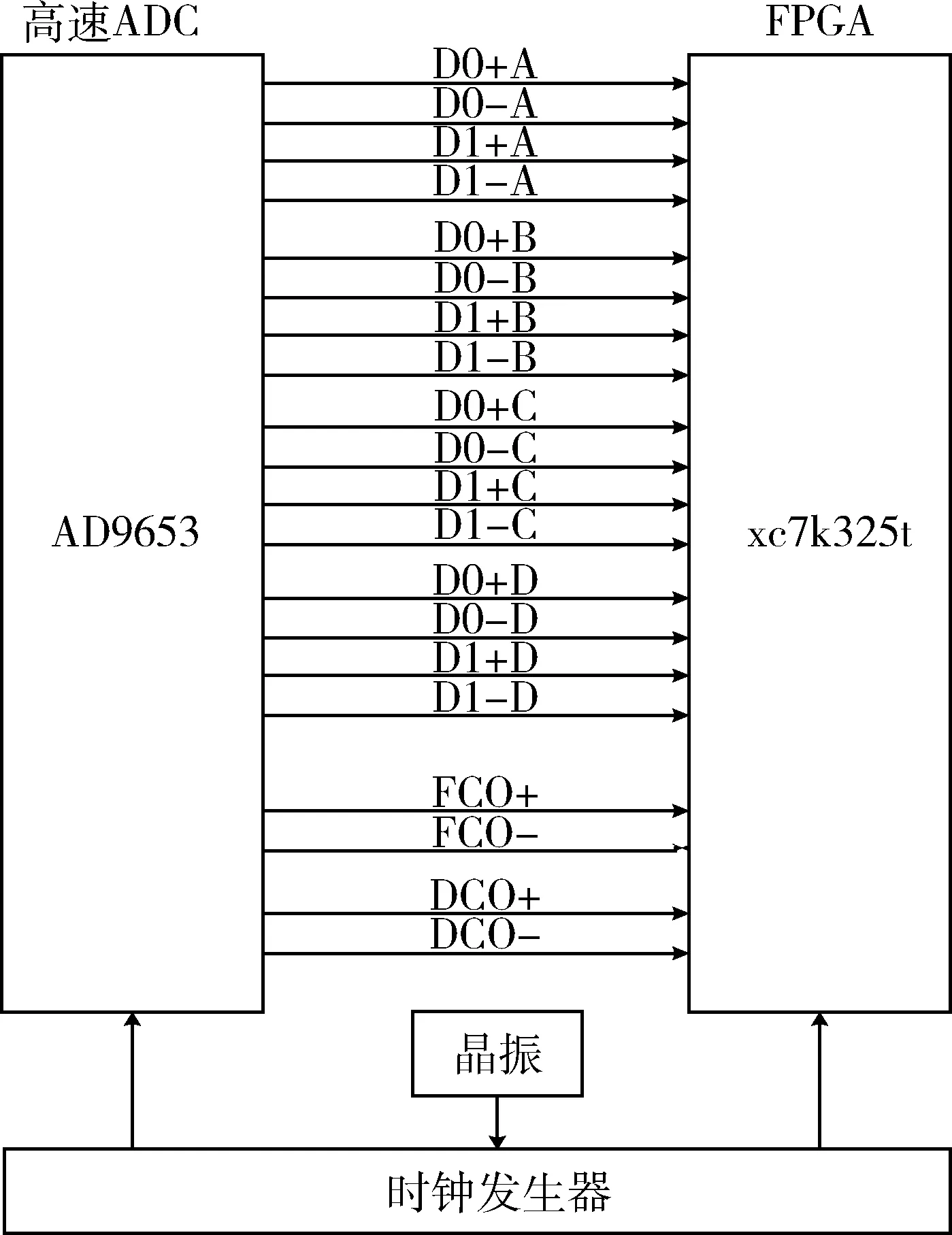

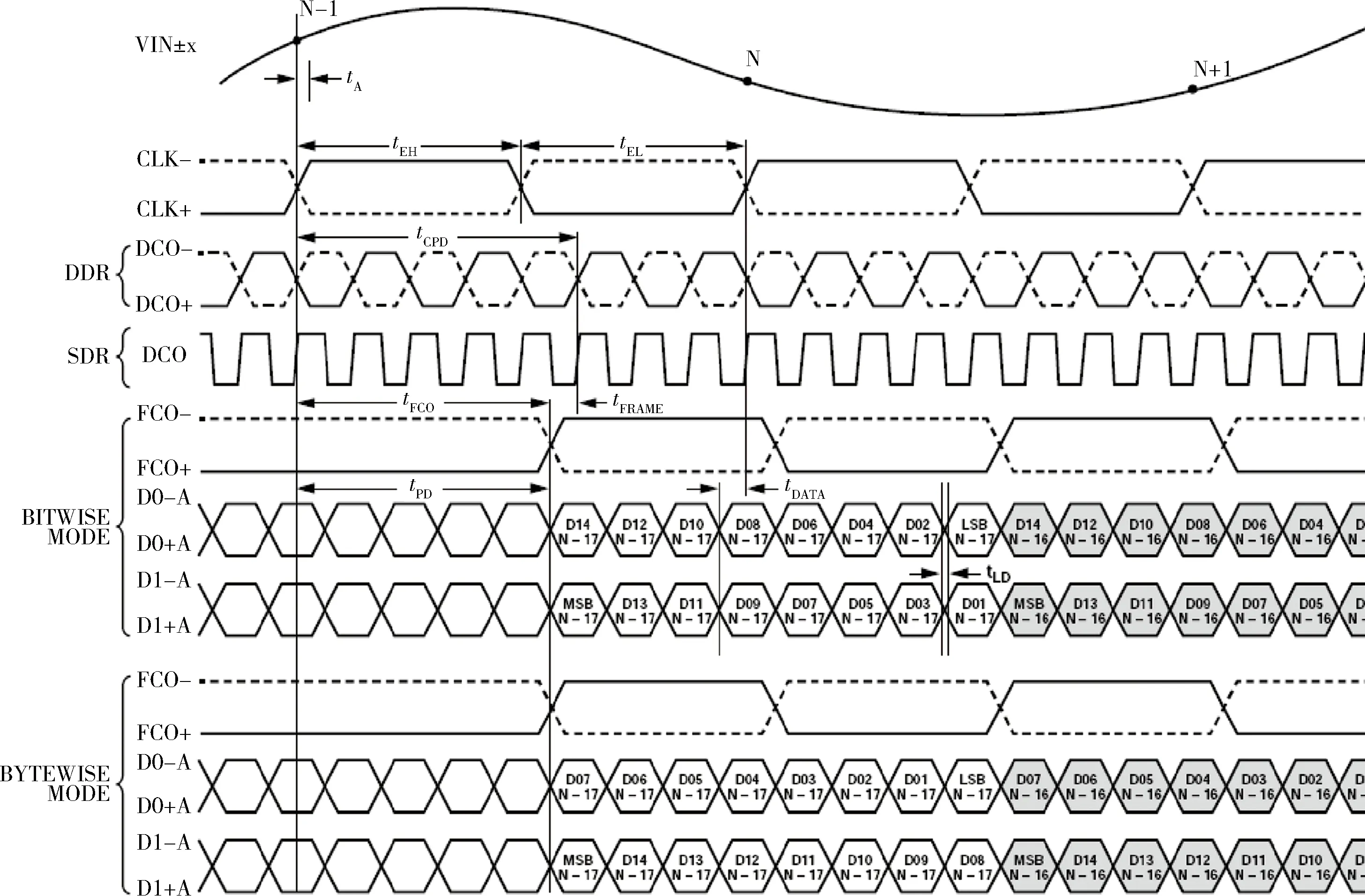

本文的四通道高速ADC和FPGA互連結構框圖如圖1所示。其中FPGA采用Xilinx公司的xc7k325t,使用內置的SERDES收發器對其進行高速解串處理。高速ADC采用AD9653,采樣數據接口格式為二進制補碼格式,采用16Bit DDR,雙通道,1x幀格式逐字節模式。具體處理過程為:AD9653對四路模擬信號進行模數轉換,再分別將對應通道采樣得到的16bit數據轉換為2對串行差分信號(例:A通道2對差分信號為D0+A/D0-A,D1+A/D1-A),采用源同步的方式連同位時鐘(DCO+/-)、幀時鐘(FCO+/-)一起傳輸給FPGA,ADC接口輸出的時序關系如圖2所示[3];在FPGA內部按照要求使用內置的SERDES收發器完成高速解串、數據幀對齊后得到采樣后的16bit并行數據進行后續的數據處理。

圖1 四通道高速ADC和FPGA互連結構框圖

圖2 AD9653的輸出時序圖

通過圖2可知AD9653輸出的位時鐘DCO+/-與串行數據D0+/-、D1+/-,幀時鐘FCO+/-之間存在固定的相位關系,只要在硬件設計上保證各路信號的走線等長,該相位關系即可保證位時鐘所處相位為最佳采樣點。但是由于位時鐘DCO作為串行數據、幀時鐘之SERDES收發器的采樣時鐘,FPGA內部的走線延時將導致到達各SERDES收發器的相位與串行數據、幀時鐘之間的相位關系發生變化,此時通過位時鐘DCO對串行數據直接采樣,將會產生誤碼。本文采用基于片同步技術對采樣位時鐘進行自適應調整至數據的最佳采樣點來可靠準確地采樣數據。

2 基于片同步的互連設計方法

2.1 片同步設計整體方案

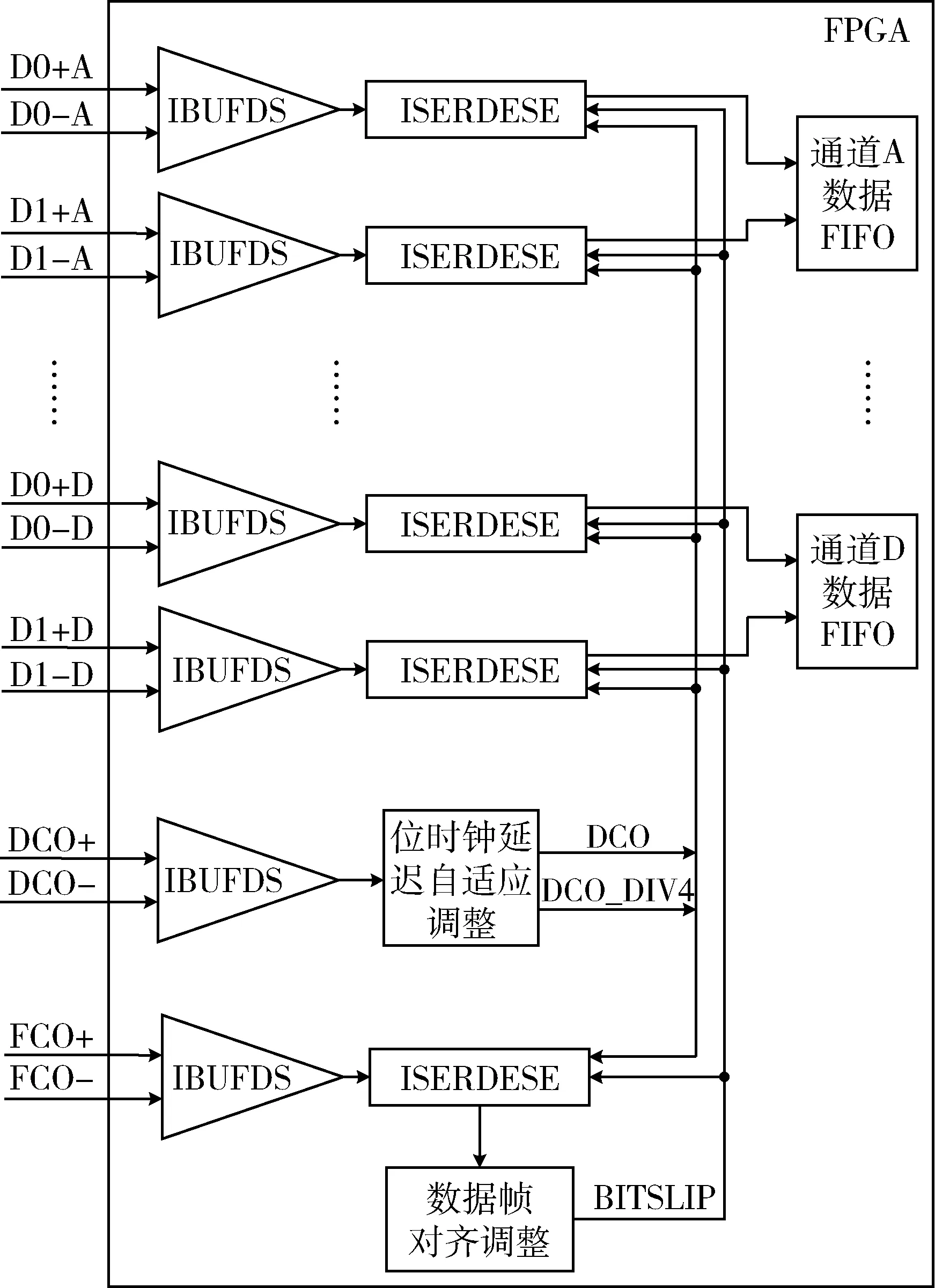

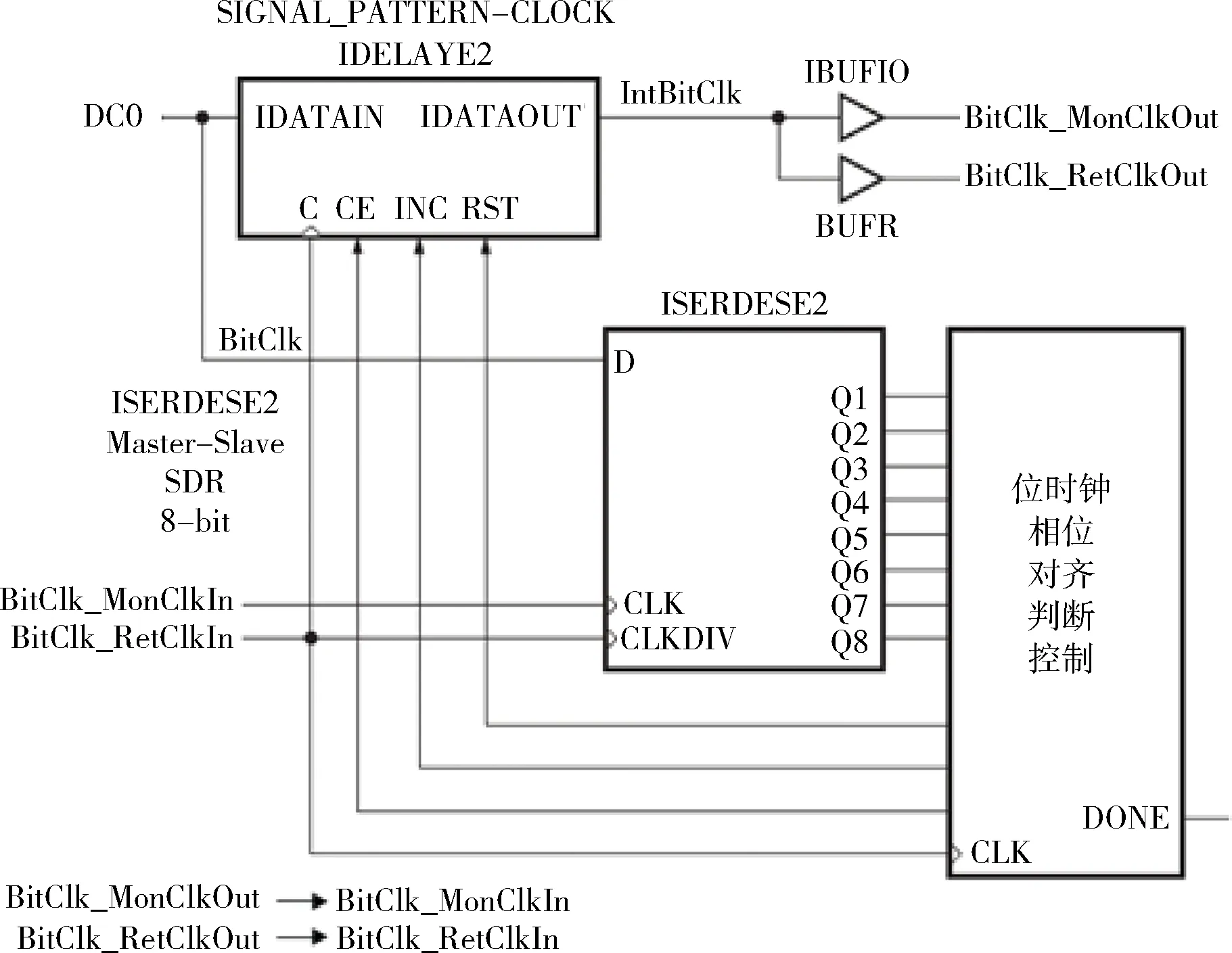

圖3為基于片同步設計的FPGA實現方案,首先通過位時鐘自適應調整模塊調節位時鐘延遲,使得連接至各ISERDES采樣時鐘的相位與輸入的DCO+/-一致,此刻采樣點處于串行數據位和幀時鐘的采樣中心,為最佳采樣位置。然后再采用數據幀對齊調整模塊對幀時鐘采樣獲得的并行數據進行判斷,產生BITSLIP信號控制各ISERDES進行移位操作,直至幀時鐘采樣輸出期望的并行數據后,完成數據幀對齊操作,此時即完成了各數據通道的并行數據提取工作。

圖3 片同步設計整體方案圖

2.2 片同步技術[4]

片同步(ChipSync)是Xilinx公司命名的一種同步技術,其目的是為FPGA提供一個高速的源同步數據總線接口。主要由IODELAY延時調整模塊、ISERDES解串模塊、OSDRDES并串轉換模塊及時鐘網絡組成。本文采用的方法主要通過IDELAY延時調整模塊控制精確延時,實現采樣位時鐘的動態調整,確定串行數據的最佳采樣位置,然后通過ISERDES解串模塊對高速串行數據進行穩定可靠的采樣。

IDELAY為內嵌32級每級78ps的可調延時器(IDELAYCTRL的參考時鐘為200MHz),可通過CE和INC信號來控制數據延時的增加和減小。

ISERDES為高速解串模塊,支持SDR、DDR兩種采樣模式。在SDR模式下,支持2、3、4、5、6、7、8位寬的串并轉換,在DDR模式下,支持4、6、8位寬的串并轉換。通過級聯可以將串并轉換器擴展到10位和14位寬。本方法中串行數據和幀時鐘對應的ISERDES選擇1:8的串并轉換(DDR模式)。同時ISERDES的BITSLIP信號負責對ISERDES的接收數據進行移位操作,用于數據位順序的調整。

2.3 位時鐘延遲自適應調整

由于數據位采樣為DDR上下沿采樣模式,故位時鐘自適應調整的過程只需要將連接至串行數據位和幀時鐘的采樣時鐘,通過IDELAY延時模塊實時調整至位時鐘DCO的跳變沿即可保證ISERDES的采樣時鐘與數據的相位關系與輸入一致,如圖4所示。位時鐘延遲自適應調整的處理方法是:

圖4 位時鐘延遲自適應調整原理框圖

將差分轉單端后的位時鐘DCO連接IDELAY延時調整模塊進行相應級數的延遲,調節級數由位時鐘相位對齊判斷控制輸出CE和INC信號進行控制。

將IDELAY輸出的延時時鐘IntBitClk分別經過BUFIO和BUFR(分頻參數為4)驅動作為ISERDES的采樣時鐘CLK和四分頻時鐘CLKDIV。其中BUFIO為IO時鐘驅動,BUFR為區域時鐘驅動,四分頻時鐘CLKDIV為并行化數據的速度。

將差分轉單端后的位時鐘DCO作為串行數據提供給ISERDES進行采樣,采樣時鐘為經過延時處理和BUFIO驅動后的同頻時鐘,位時鐘對應的ISERDES選擇1:8的串并轉換(SDR模式)。

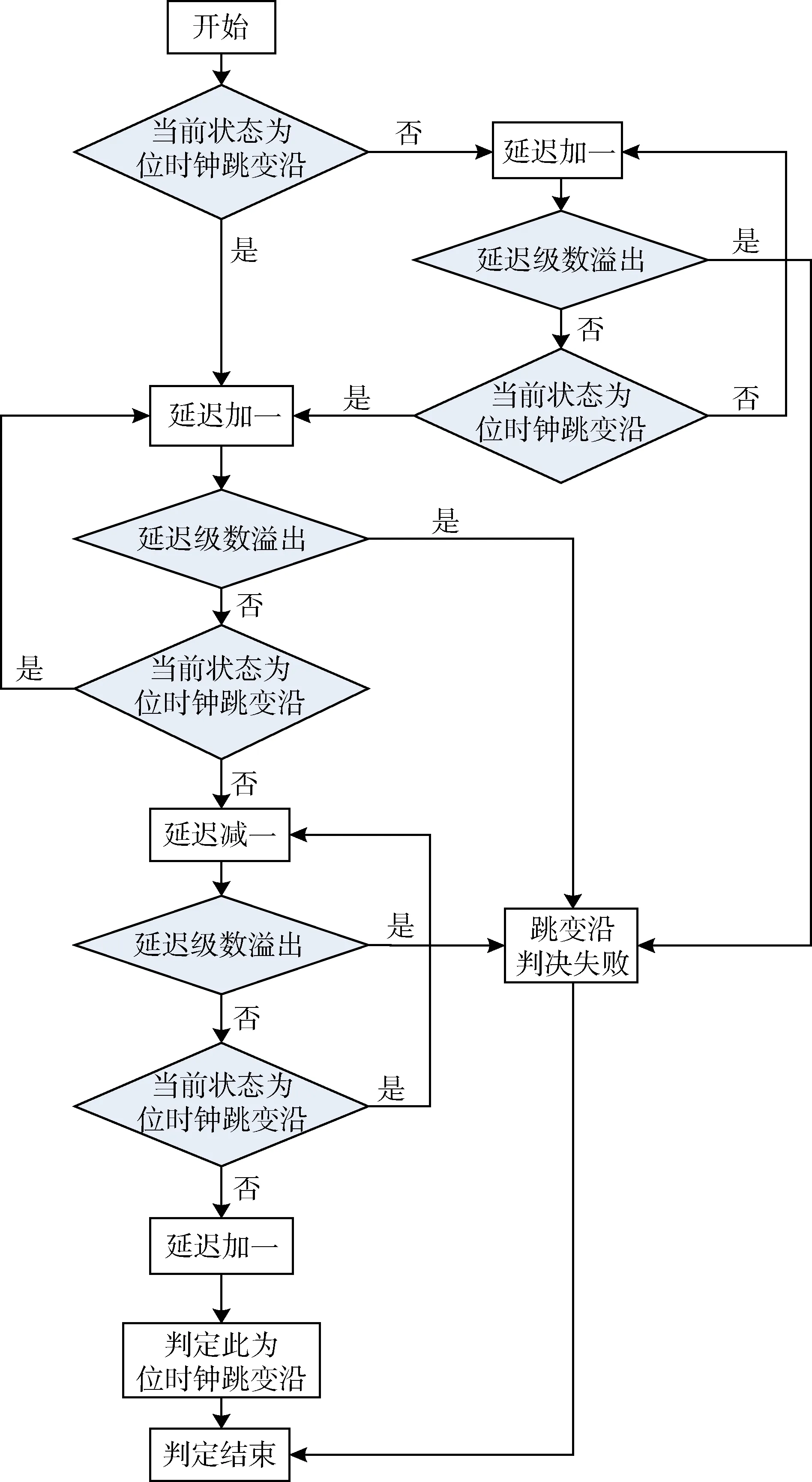

位時鐘相位對齊判斷控制負責對ISERDES的并行數據(Q1~Q8)進行判斷,尋找位時鐘的跳變沿。處理流程如圖5所示。

圖5 位時鐘相位對齊判斷控制處理流程圖

位時鐘跳變沿的判斷依據為ISERDES上一次采樣的并行數據和當前并行數據結果不一致,則當前設置的IDELAY延遲采樣時鐘與輸入的位時鐘跳變沿對齊。通過IDELAY延時調整補償了FPGA內部位時鐘的走線延時,使之與AD9653輸出數據相位關系保持一致,保證了采樣時鐘處于數據采樣窗口的最佳位置。另外IDELAY的延遲級數為32,需要對延遲級數是否溢出進行判斷,當延時級數超過32時表明由于位時鐘跳變沿速率不高,IDELAY在整個延遲周期都無法找到位時鐘的跳變沿,此時跳變沿判定失敗。

2.4 數據幀對齊調整

位時鐘延時自適應調整負責完成串行數據和幀時鐘的ISERDES采樣位時鐘與輸入位時鐘相位對齊,但只能保證串行數據被位時鐘正確采樣,而串并轉換后的并行數據順序不確定,將有8個組合。為了得到正確順序下的并行數據流,需要進行數據幀對齊調整。數據幀對齊調整采用對幀時鐘ISERDES采樣并行數據進行判斷,通過調整串行數據和幀時鐘ISERDES的BITSLIP,當幀時鐘ISERDES采樣得到的并行數據與期望的數字序列“00001111”相同時,表明此時數據幀輸出順序正確,即完成了數據幀對齊工作,否則產生一個并行化數據時鐘寬度的BITSLIP控制ISERDES的移位操作,進行下一次的判斷操作。

3 仿真與板級驗證

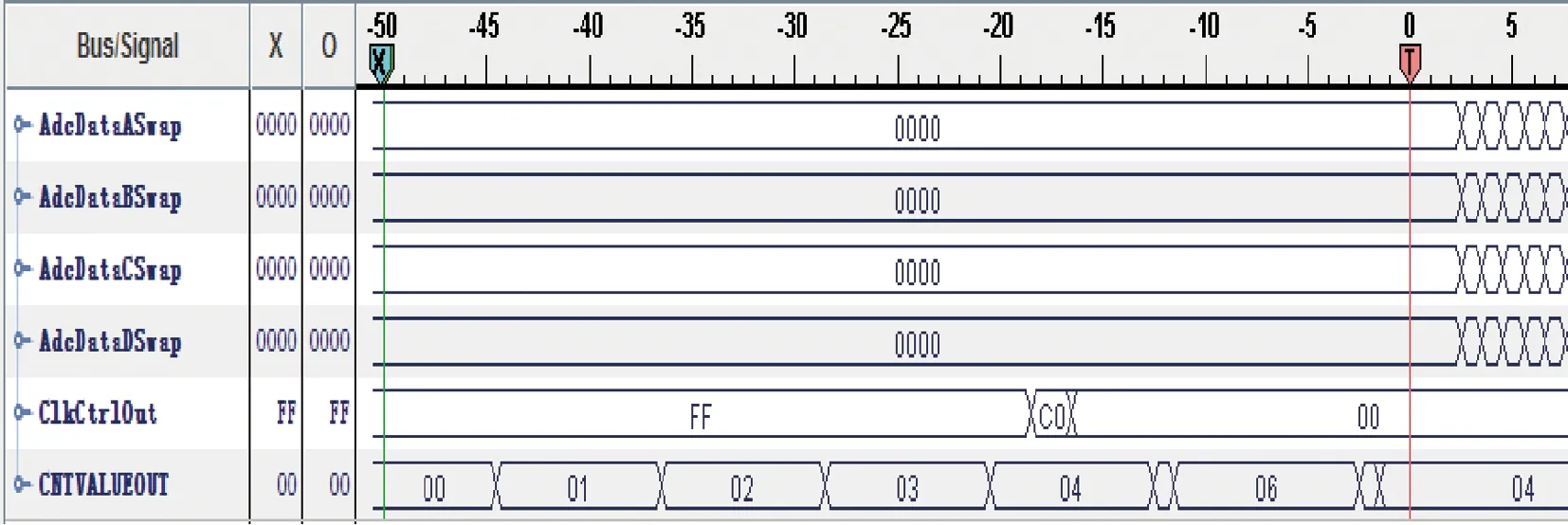

高速接口的FPGA程序是在Xilinx ISE14.7編譯環境下實現的,通過編寫測試激勵文件在Questa Sim 10.0a軟件下進行了仿真。如圖6所示。經過3146ns,通過IDELAY延時模塊18級延時調整后,ISERDES輸出的并行數據發生變化,采樣位時鐘DcoClk_MonClkOut與端口輸入位時鐘DcoClk的相位差由0.6ns減小到0.004ns,實現了位時鐘的自適應對準。其中,CNTVALUEOUT為IDELAY延時模塊的延時階數;ClkCtrlOut為ISERDES采樣得到的并行數據。

圖6 采樣位時鐘相位調整驗證仿真圖

使用信號發生器產生正弦信號進行板級測試,采樣頻率為125MHz,雙線傳輸,單通道數據率為2Gb/s(125M*16bit)。使用ChipScope工具抓取位時鐘的自適應對準過程和采樣后的并行數據結果。

位時鐘的自適應對準過程板級測試圖如圖7所示,在IDELAY延時模塊完成4級延時調整后(CNTVALUEOUT為x“04”),位時鐘DCO采樣ISERDES輸出的并行數據值ClkCtrlOut發生跳變(由x“FF”變為x“C0”,最后為x“00”),此時位時鐘完成自適應對準,IDELAY延時模塊固定在4級延時值上,開始進行后面的數據幀對齊調整和中頻采樣數據工作。

圖7 位時鐘的自適應對準過程板級測試圖

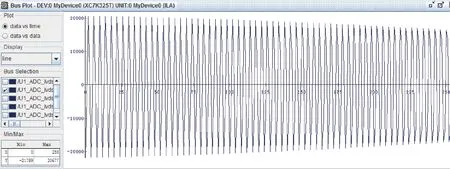

圖8為完成數據幀對齊調整對準后對正弦信號的實時采樣數據波形圖,橫坐標為采樣點數,縱坐標為數值。輸入波形與輸出波形一致,完成了對本文采用方法的正確性驗證。

圖8 采樣數據波形圖

4 結論

針對多通道的高速ADC與FPGA互連傳輸的要求,本文提出通過FPGA的片同步技術對位時鐘延時進行自適應調整來解決FPGA內部走線延時帶來的數據高速采樣不穩定問題,與通過對數據位進行延遲調整的方式,降低了FPGA的邏輯復雜度。測試結果表明該方法可滿足高速數據傳輸的要求,已在實際工程中得以應用。該方法也可作為其他點對點高速數據傳輸系統設計的參考。

參 考 文 獻

[1] 顧峰, 呂余清. 應用源同步技術實現高速ADC與FPGA互連[J].電子技術, 2016,10:30-33.(Gu Feng, Lv Yuqing. Implementing High-speed ADC and FPGA Communication Based on Source Synchronization Technology [J]. Electronic Technology, 2016,10:30-33.)

[2] 屈超. 多通道ADC的高速接口設計[J].無線電通信技術, 2013,39(3):76-78.(Qu Chao. Design on Multichannel ADC High-speed Interface[J]. Radio Communications Technology, 2013,39(3):76-78.)

[3] Analog Devices. AD9653[EB/OL]. http://www.analog.com/media/en/technical-documentation/data-sheets/AD9653.pdf.

[4] Xilinx,7 Series FPGAs SelectIO Resources User Guide[EB/OL]. http://www.xilinx.com/support/documentation/user_guides/ug471.pdf.