星載存儲器吞吐率瓶頸與高速并行緩存機制

董振興, 朱 巖, 許志宏, 宋 琪

(1.中國科學院國家空間科學中心,北京 100190; 2.中國科學院大學,北京 100190)

星載存儲器吞吐率瓶頸與高速并行緩存機制

董振興1,2, 朱 巖1,2, 許志宏1,2, 宋 琪1,2

(1.中國科學院國家空間科學中心,北京 100190; 2.中國科學院大學,北京 100190)

為解決目前星載存儲器無法有效支持多路高速數據并行存儲的問題,針對載荷數據高速輸入需求,對基于NAND Flash的固態存儲器的吞吐率瓶頸進行分析,根據固態存儲器的固有寫操作特性對有效吞吐率的影響,提出了四級流水線操作和總線并行擴展方案;針對多通道數據并行存儲、流水線加載連續性等需求,對使用現場可編程門陣列FPGA(Field-Programmable Gate Array)內部雙端口隨機存取存儲器RAM(Random access memory)、外置靜態隨機存取存儲器SRAM(Static Random Acess Memory)等已有緩存方案的不足進行分析,完成了基于同步動態隨機存儲器SDRAM(Synchronous Dynamic Random Access Memory)的方案可行性分析與新型存儲單元架構設計,最終提出了基于SDRAM的高速多通道緩存與存儲協同調度方案. 模型仿真與原型功能驗證結果表明,方案在極限工況下可將4路高速文件數據連續并行接收緩存至SDRAM中,并可根據各分區緩存狀態將文件數據按優先級自主動態寫入Flash中,期間緩存無溢出,并最終進入常規動態平衡調度狀態,實現了對多路高速載荷數據的并行接收緩存和自主調度存儲,且存儲器的數據吞吐率可達1.2Gbps,能夠滿足未來星載存儲器對多路高速載荷數據存儲的需求.

星載存儲器;存儲吞吐率;流水線操作;總線并行擴展;高速并行緩存

隨著航空航天事業的快速發展,空間探測器的有效載荷種類及任務形式多樣化,對星上數據管理系統高速并行存儲能力提出更高要求. 星載存儲器是數管系統的核心設備之一[1-2]. 基于NAND Flash的固態存儲器具有存儲密度高、非易失等特點,是星上數據存儲的主流方式[3-5].

目前星載存儲器方案主要面向低速有效載荷設計,支持信源量小、固定分區存儲靈活性差[6-7],如暗物質粒子探測衛星、實踐十號科學實驗衛星存儲器有效吞吐率低于350Mbps,僅支持兩路數據分區存儲,無法適用于多路載荷數據高速輸入、同一時刻多任務等工作模式. 徐永剛等[8]基于Flash設計的圖像記錄系統使用CPU內存作為兩路外部圖像數據緩存,每路各緩存一幅圖像后由CPU將數據按順序逐一寫入Flash陣列中,其緩存調度方式制約了載荷數據的輸入速率. 李晴等[9-10]針對Flash存儲技術和高速互連技術進行了研究,系統通過多個存儲體同時工作實現對多種類型數據記錄,雖然提高了系統存儲吞吐率,但不支持單個存儲體對多路載荷數據的有效存儲,無法適用于對功耗、重量等要求嚴格的航天領域. 為此,針對星載存儲器實際應用,對固態存儲器吞吐率瓶頸進行分析,探討提高吞吐率關鍵技術以支持高速載荷數據輸入,并對高速并行緩存與任務調度機制進行設計驗證,以期解決單板存儲器對多路高速數據同步緩存與自主存儲方案的需求問題.

1 星載存儲器吞吐率分析

1.1基于Flash存儲器吞吐率瓶頸

目前星載存儲器主要使用經抗輻照加固處理后的宇航級3DFN64G08VS NAND Flash疊裝芯片,每個疊裝模塊由8片K9F8G08U0M基片組成[11]. 設疊裝模塊Flash數據總線位寬為Wone_die,最大工作頻率為fflash_work_max,則單個模塊理論最高吞吐率為

Hone_die_theory_max=fflash_work_max*Wone_die.

(1)

宇航級NAND Flash基片最高工作頻率為50 MHz,抗輻照加固后疊裝模塊最高工作頻率降為40 MHz. 根據軍用元器件80%降額使用準則,NAND Flash實際最高工作頻率為32 MHz,又Wone_die=8bit,由式(1)可得Flash疊裝模塊理論最高吞吐率為256 Mbps.

固態存儲器的固有寫操作特性降低了有效吞吐率. K9F8G08U0M基片以頁為單位進行讀寫操作,一頁數據區大小為4 096 Bytes,數據寫入時,先將數據加載到芯片內部緩存區,再經過編程完成數據寫入,寫操作流程見圖1.

根據寫操作時序要求,完成一頁數據寫操作需要的時間為:

tone_page_write=tLOAD+tPROG+tCHECK,

(2)

tLOAD=tcommand+taddress+tADL+tdata.

(3)

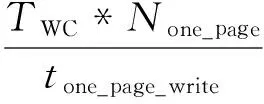

時序參數見表1,其中:T為時鐘周期,None_page為頁容量,tWHR為讀取編程結果等待時間.

圖1 NAND Flash寫操作流程

參數說明時間tcommand命令加載時間3*Ttaddress地址加載時間5*TtADL地址到數據加載間隔≥100nstdata數據加載時間None_page*TtPROG編程等待時間200us~700ustCHECK編程結果檢查時間≥tWHR+TtWHR讀編程結果等待時間≥60ns

設Flash有效寫操作效率為ηone_die_write,實際工作時最大支持寫速率為Hone_die_theory_max,則

(4)

Hone_die_work_max=Hone_die_thy_max*ηone_die_write.

(5)

由式(2)~(5)可得Flash在實際工作中的最高有效寫操作效率為38.97%,最高寫速率為99.76 Mbps,無法滿足多路高速載荷數據的存儲需求.

1.2提高吞吐率關鍵技術

1.2.1 流水線操作

在Flash寫操作流程中,芯片編程占用大量時間,大大降低了Flash的寫入效率,采用流水線操作方式可解決芯片內部編程過程中的長時間等待問題. 流水線寫Flash操作原理見圖2.

每次加載數據到一組Flash芯片后,該組芯片進入內部編程狀態,在此期間盡管不能對該組芯片進行其它操作,但可立即進行另一組芯片加載. 由芯片加載時間與編程時間數值關系知,當第4組芯片加載完畢后,第1組芯片的編程過程通常已經結束. 使用四級流水線操作技術,可以基本保證宏觀上實現對存儲區的全速率無間斷數據寫入,Flash有效寫操作速率接近理論值256 Mbps,解決了存儲介質固有寫操作特性對存儲器有效吞吐率的限制.

圖2 四級流水線加載Flash原理

1.2.2 總線并行擴展

為進一步提高存儲吞吐率,擴展存儲容量,在空間橫向軸上采用I/O總線并行擴展技術. 綜合考慮FPGA管腳資源和存儲器性能需求,設計8倍I/O總線并行擴展方案,并行擴展結構見圖3.

將8片Flash疊裝模塊控制總線、狀態總線互連,而I/O總線擴展為64位,64位總線不同數據位段分別對應8片并行擴展的Flash的8位總線,將Flash中8片并行的頁擴展成1簇進行讀寫操作. 由于物理空間擴展與芯片操作時序無關,因此8倍總線擴展后系統速率將提高為原來的8倍,此時存儲器單板理論可支持最高2Gbps數據輸入,提高了存儲系統對高速載荷數據的吞吐能力.

圖3 8倍FLASH I/O并行擴展結構圖

2 高速緩存與存儲任務調度

四級流水線的操作特點要求Flash在啟動寫操作時,將加載所需的四簇數據準備完成,以確保四級流水加載連續性,同時為保證每次流水操作均是針對同一載荷,需設計并行緩存機制解決多路載荷數據各自分區緩存問題.

傳統方案使用FPGA內部雙端口RAM作為緩存以降低控制復雜度,但對于多路載荷高速并行輸入,有限的RAM資源難以滿足緩存容量需求. 外置緩存芯片SRAM雖然有了一定容量提升,但仍然有限,并且在64位數據總線下SRAM接口速率最高為2 Gbps,數據吞吐復用I/O端口時平均讀寫速率只有1 Gbps,限制了Flash最高寫速率使用. 宇航級SDRAM(Synchronous Dynamic Random Access Memory,同步動態隨機存儲器)芯片最高工作頻率達133 MHz,當數據總線為64 bits時,理論接口總吞吐率可高達8 Gbps,且芯片容量3 Gbits,能夠滿足系統高吞吐率需求.

2.1SDRAM緩存可行性

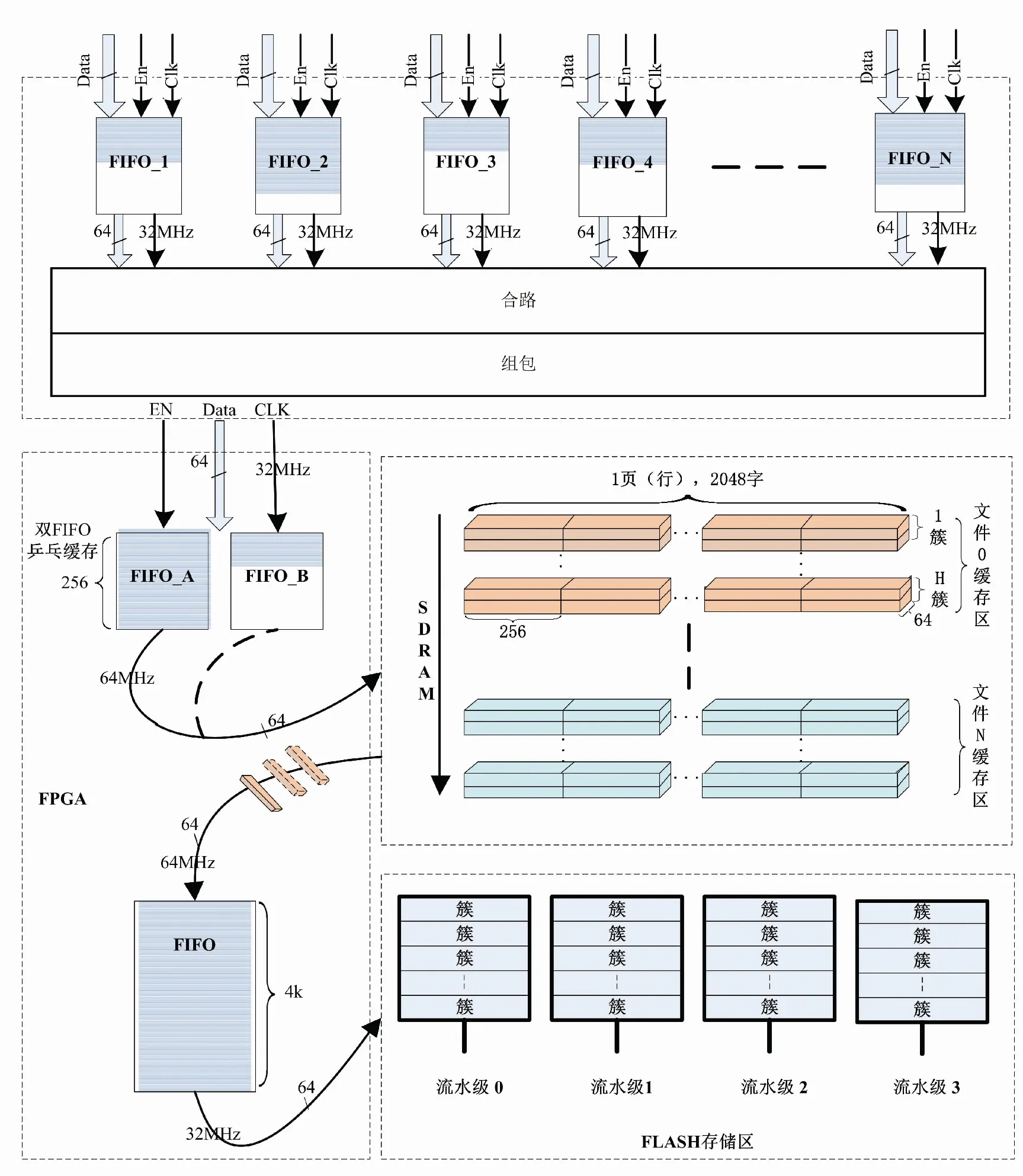

SDRAM芯片一次完整的讀/寫數據操作包括自刷新、行選通、數據突發讀寫、預充電及自動刷新等部分[12],操作流程見圖4.

圖4 SDRAM讀寫操作流程圖

SDRAM換行操作需再次行選通,為減小時間開銷,設計一次讀、寫所涉及地址均在同一行內,數據吞吐采用8字突發傳輸方式. 由于SDRAM芯片每64 ms內必須完成8 192次自動刷新操作以保證數據有效,為保證連續讀/寫作過程滿足刷新要求,將自動刷新機制分配到每個讀/寫周期操作后,此時

(6)

其中:NW/R為一個讀/寫周期的數據大小,T為SDRAM工作時鐘周期,Nref為每次讀/寫操作后自動刷新次數,操作時序參數見表2.

當SDRAM工作時鐘為64 Mhz,Nref取2時,由式(6)可得吞吐率HW/R_operate=3.848 Gbps,平均讀寫速率HW/R_operate_average=1.924 Gbps,與NAND Flash最大支持寫速率相匹配,能夠滿足多通道分區輸入速率、空間需求,緩存方案可行.

表2 SDRAM時序參數

2.2星載存儲器方案設計

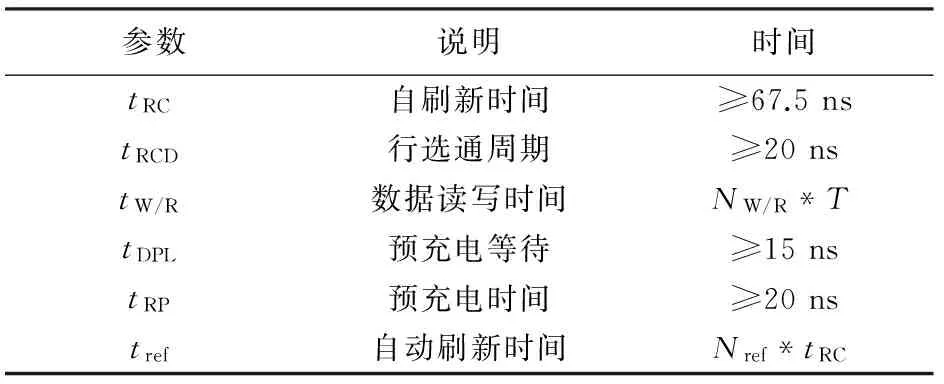

采用四級流水線操作與總線并行擴展技術提高單板存儲吞吐率與存儲容量,采用SDRAM芯片作為緩存支持高速并行數據輸入,星載存儲器總體設計方案見圖5.

圖5 星載存儲器方案框圖

新型星載存儲器設計參數為單板數據吞吐率2 Gbps,存儲容量1 Tbits. 采用FPGA作為控制器載體,配置SDRAM高速并行緩存,將各載荷數據動態自主存儲于NAND Flash中. 數管系統CPU單元運行存儲管理軟件,實現存儲系統的文件化管理.

2.3高速數據并行緩存

在多路高速載荷數據并行輸入的工況下,合路單元設置FIFO分別接收緩存,同時設定文件號與之對應. 隨后數據被送至存儲控制單元,經RS(252,256)糾錯編碼后通過雙FIFO進行乒乓緩存. 任一FIFO緩存滿256字后向SDRAM控制模塊發出讀申請,SDRAM根據載荷數據文件號將數據送往對應的分區通道進行緩存. 當任一SDRAM分區內緩存的數據量滿足四級流水需要(即滿4簇)時,存儲控制FPGA與CPU單元協同管理,啟動Flash寫操作,將數據按四級流水寫入固態存儲介質. 多通道數據并行接收與緩存流程見圖6.

圖6 多通道數據并行接收與緩存流程圖

2.4存儲任務調度

由于各載荷通道數據速率的差異,導致SDRAM各分區內緩存數據量互不相同,當多個緩存通道同時滿4簇大小,或者一個緩存通道中有多個4簇大小緩存時,可通過通道緩存任務調度機制保證數據被完整有效存儲.

設計Flash寫操作優先級最高,讀操作次之,擦除操作優先級最低,以保證Flash在復雜工況下載荷數據被優先存儲;設計優先對SDRAM通道緩存中速率高的載荷數據進行寫Flash操作,以防止數據緩存溢出. 通道緩存任務調度與存儲流程見圖7.

圖7 通道緩存任務調度與存儲流程圖

存儲控制FPGA根據載荷數據產生速率高低由小到大依次分配文件號,SDRAM控制模塊按文件號由大到小輪詢各通道數據緩存情況,當某通道緩存數據多于4簇時,寄存該通道文件號. 完成所有通道遍歷后,確定當前被操作通道,如果被操作緩存通道有多個4簇數據,則按緩存時間先后順序進行通道內各4簇數據調度讀取.

SDRAM各通道需設置的緩存空間大小由多路有效載荷數據速率綜合決定. 保證通道緩存不溢出的條件是存儲器在極限工況下工作時SDRAM各通道仍有緩存空間,即在SDRAM各緩存通道都即將滿4簇時, NAND Flash啟動了擦除操作,待擦除操作完成后,所有通道緩存數據被完整寫入Flash存儲區.

3 仿真驗證

為驗證存儲器高速并行緩存與任務調度機制設計正確性,使用Matlab工具進行模型仿真. 設置輸入條件為:1)4路載荷,數據速率分別為480 Mbps、400 Mbps、200 Mbps、120 Mbps;2)文件號對應設定為1~4;3)極限工況;4)載荷數據連續輸入;5)Flash擦除時間1.5 ms,流水寫4簇數據時間0.5 ms;6)存儲無失敗. 對SDRAM內部各文件緩存變化情況進行仿真觀察,結果見圖8.

圖8 4路文件并行緩存與存儲調度模型仿真

Fig.8 Model simulation of 4 files parallel cache and storage scheduling

t=0時刻,4路文件緩存均將滿4簇,由于擦除任務阻塞,Flash不執行寫操作;

t=0~3時,Flash擦除操作,4路文件持續寫入SDRAM緩存,無寫Flash操作;

t=3時刻,Flash擦除結束,4路文件緩存均多于4簇,根據優先級讀文件1緩存寫Flash;

t=4時刻,文件1寫結束,文件2、文件3、文件4緩存多于4簇,讀文件2緩存寫Flash;

t=5時刻,文件2寫結束,文件1、文件3、文件4緩存多于4簇,開始讀文件1寫Flash;

t=6時刻,文件1寫結束,文件2、文件3、文件4緩存多于4簇,開始讀文件2寫Flash;

t=7時刻,文件2寫結束,文件3、文件4緩存多于4簇,開始讀文件3寫Flash;

t=8時刻,文件3寫結束,文件4緩存多于4簇,開始讀文件4寫Flash;

t=9時刻,因擦除阻塞累積的所有緩存文件全部寫入Flash中,SDRAM進入常規動態平衡調度狀態.

綜上,在極限工況下4路文件數據被連續并行接收緩存至SDRAM中,并按照存儲優先級動態自主調度寫入Flash,期間緩存無溢出,并最終進入常規動態平衡調度狀態. 仿真結果符合并行緩存與任務調度機制設計,滿足了多路高速數據同時輸入需求,說明方案機理設計有效可行.

為進一步驗證高速并行緩存與任務調度機制的實用性,基于FPGA開發程序進行原型功能仿真. 參考模型仿真結果,并考慮到FPGA內部模塊間交互時間開銷與Flash可能存儲失敗重加載的影響,設置各文件緩存通道大小為4個4簇(0~3,4~7,8~11,12~15). 在與模型仿真實驗相同載荷速率輸入條件下,4路文件并行緩存與存儲調度原型功能仿真結果見圖9.

在原型功能仿真結果中選取部分關鍵時間點,觀察分析SDRAM內各文件緩存調度變化情況見表3.

圖9 4路文件并行緩存與存儲調度原型功能仿真

項目關鍵時間點A時刻B時刻C時刻D時刻E時刻F時刻文件1緩存12~15簇未滿12~15簇滿0~3簇未滿0~3簇滿0~3簇滿4~7簇未滿文件2緩存8~11簇滿12~15簇未滿12~15簇未滿12~15簇滿0~3簇未滿0~3簇未滿文件3緩存0~3簇滿0~3簇滿0~3簇滿4~7簇未滿4~7簇未滿4~7簇未滿文件4緩存0~3簇未滿0~3簇未滿0~3簇未滿0~3簇未滿0~3簇滿0~3簇滿SDRAM操作正在讀文件2并寫Flash啟動讀文件1并寫Flash啟動讀文件3并寫Flash正在讀文件2并寫Flash正在讀文件1并寫Flash啟動讀文件4并寫Flash理論存儲調度讀文件2讀文件1讀文件3讀文件2讀文件1讀文件4

由原型功能仿真結果可知,在實際工作中4路載荷文件被并行接收緩存至SDRAM中,存儲任務調度機制根據各分區緩存狀態將文件按優先級自主動態寫入Flash中,仿真結果與模型仿真結果吻合,并驗證了存儲器單板可有效支撐1.2Gbps數據輸入,證明了高速并行緩存與任務調度方案的可行性和實用性.

4 結 論

針對目前星載存儲器無法有效支持多路高速數據并行存儲的問題,采用四級流水線操作和總線并行擴展方案,提高了存儲系統對多路高速數據的存儲能力;設計SDRAM高速多通道緩存與存儲協同調度機制,實現了多路數據有效并行接收緩存與存儲,確保了復雜工況下數據存儲完整性. 模型仿真與原型功能仿真結果表明SDRAM高速多通道緩存與存儲寫操作協同調度機制設計有效可行.

[1] MORGAN P S. Cassini Mission-to-Saturn Spacecraft overview & CDS preparations for end-of-mission Proximal Orbits[C]// 2015 IEEE Aerospace Conference. Big Sky, MT:IEEE Press, 2015:1-18. DOI: 10.1109/AERO.2015.7118911.

[2] FABIANO M, FURANO G. NAND flash storage technology for mission-critical space applications[J]. IEEE Aerospace and Electronic Systems Magazine, 2013,28(9):30-36. DOI: 10.1109/MAES.2013.6617096.

[3] 李姍,宋琪,朱巖,等.星載大容量固態存儲器快速可靠啟動算法設計[J].哈爾濱工業大學學報, 2015,47(10):100-105.

LI Shan, SONG Qi, ZHU Yan, et al. Design of quick initialization algorithm for space-borne solid state recorder[J]. Journal of Harbin Institute of Technology, 2015,47(10):1-10.DOI:10.11918/j.issn.0367-6234.2015.10.019.

[4] REID M, OTTMAN G. Software controlled memory scrubbing for the Van Allen Probes Solid State Recorder (SSR) memory[C]// IEEE Aerospace Conference. Big Sky, MT:IEEE Press, 2014:1-6. DOI: 10.1109/AERO.2014.6836406.

[5] KIM J Y, PARK S H, SEO H, et al. NAND flash memory with multiple page sizes for high-performance storage devices[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2016,24(2):764-768. DOI: 10.1109/TVLSI.2015.2409055.

[6] 宋琪.星載固態存儲技術的應用與研究[D].北京:中國科學院大學,2015.

SONG Qi. Research and application of spaceborne solid state reocorder technology [D]. Beijing: University of Chinese Academy of Sciences, 2015.

[7] HSIEH J W, TSAI Y L, KUO T W, et al. Configurable flash-memory management: performance versus overheads[J]. IEEE Transactions on Computers, 2008,57(11):1571-1583. DOI: 10.1109/TC.2008.61.

[8] 徐永剛.基于NAND Flash的嵌入式圖像記錄技術[D]. 北京:中國科學院大學,2013.

XU Yonggang. Embedded image recording technology based on NAND flash[D]. Beijing: University of Chinese Academy of Sciences, 2013.

[9] 李晴.高速大容量NAND FLASH存儲系統的設計與實現[D]. 北京:北京理工大學,2015.

LI Qing. The design and realization of a high speed and large capacity NAND FLASH storage system[D]. Beijing: Beijing Institute of Technology, 2015.

[10]徐玉杰.高速大容量存儲系統的設計與實現[D].西安:西安電子科技大學,2014.

XU Yujie. Design and implementation of high-speed and huge-capacity storage system[D]. Xi’an: Xidian University, 2014.

[11]Samsung Electronics. K9F8G08UXM NAND FLASH memory data sheet [EB/OL].(2007-3-31). www.datasheetspdf.com/datasheet/K9F8G08UXM.html.

[12]Orbita Control Engineering Co., Ltd. VDSD3G48XQ114XX6V75 user manual(Version 1.4)[EB/OL]. [2016-11-29]. www.myorbita.net.

Bottleneckanalysisofspacebornememorythroughputandhigh-speedparallelcachingmechanismdesign

DONG Zhenxing1,2, ZHU Yan1,2, XU Zhihong1,2, SONG Qi1,2

(1. National Space Sciences Center, Chinese Academy of Sciences, Beijing 100190, China;2.University of Chinese Academy of Sciences, Beijing 100190, China)

To solve the problem that the current spaceborne memory cannot support parallel storage of multi-channel high-speed data effectively, this paper proposes two methods. To satisfy the requirement of receiving high-speed payload data, this paper analyzes the throughput bottleneck of NAND Flash-based solid-state memory, and proposes a four-stage pipeline operation and bus parallel expansion scheme according to the inherent write operation characteristics. To meet the needs of parallel storing multi-channel data and the continuity of pipeline operation, this paper analyzes the deficiencies of the data cache methods which use RAM (Random access memory) and SRAM (Static Random Acess Memory), and proposes a scheduling scheme using high-speed caching and cooperative storing, which is based on SDRAM (Synchronous Dynamic Random Access Memory). Through the model simulation and the prototype function verification, we verify that the proposed scheme can effectively support parallel reception of the 4-way high-speed payload data and the autonomous scheduling storage of solid state memory, and the throughput rate of memory can reach 1.2 Gbps, which satisfies the demands for storing the multi-channel high-speed payload data on spaceborne memory in the future.

spaceborne memory; storage throughput; pipeline operation; bus parallel expansion; high speed parallel cache

10.11918/j.issn.0367-6234.201611144

TN919.5

A

0367-6234(2017)11-0052-08

2016-11-30

中國科學院空間科學先導衛星計劃(XDA0402020201)

董振興(1991—),男,博士研究生 朱 巖(1973—),男,博士生導師

董振興,E-mail: dongzhenxing@nssc.ac.cn

(編輯苗秀芝)