基于自抗擾的三電機同步解耦控制系統

馮佩云,陳 沖,馮俊青,段小匯

(1.鹽城工學院,鹽城 224051;2江蘇大學,鎮江 212013)

0 引 言

在高性能的同步控制領域[1],為了達到最優的控制效果,必須使信號傳輸并處理及時,如果數據處理較慢,則在此情況下會使系統控制性能變差,而處理速度快的控制器價格很高,這就要求在合適的價位以及高性能的控制效果中權衡并選用合適的運動控制器。目前,我國運動控制器系列產品起步晚、發展相對較慢,所供應的產品大約有以下幾種[2]:(1)用微處理器(MCU)作為控制器的“大腦”[3]。這種類型的控制器的控制精度不高,但控制器價格較便宜,所以適合于在一些低速控制領域或對運動控制精確性要求較低等場合使用;(2)將專用芯片設計為“指揮中心”。這類控制器結構簡單、成本較低,是根據特定的控制要求來設計相應的控制方法,這一基本控制思想決定了它只能針對特定的系統實現特定的控制過程,限制了通過專用芯片設計的控制器使用廣泛度,自適應性較差;(3)設計出用DSP并在外圍擴展CPLD或FPGA的運動控制器[4-7],這種控制器利用了各個芯片的獨特優勢,采用開放式結構,便于開發人員二次開發等優點,在運動控制領域得到了很快的發展。本文選用第三種設計思路,設計了基于單片機、DSP和CPLD共同組成的三核控制器,完成了多電機同步協調控制,該控制器具有成本低廉,靈活方便,可靠性高等特點。

1 三電機同步系統的總體設計

1.1 三電機同步系統的控制方案

本文需要控制的參數是1個轉速與2個張力,整個三電機系統是3輸入3輸出的被控系統,在控制過程中,先精確控制主電機的轉速,在此基礎上通過張力控制器1有效控制1,2號電機的張力值,以此來控制2號電機的轉速,這就使2號電機跟隨1號電機良好的運行,以此類推來控制最后一臺電機的轉速,使其跟隨中間電機良好運行,從而達成整個被控目標同步協調運行。當選用經典PID控制方案時,調節過程完全依靠經驗、調節時間長,增加了控制的復雜程度又達不到最優的控制效果,本文采用ADRC的控制方案[8],如圖1所示。

圖1 基于一階ADRC的三電機同步控制策略

1.2 速度、張力自抗擾控制環的設計

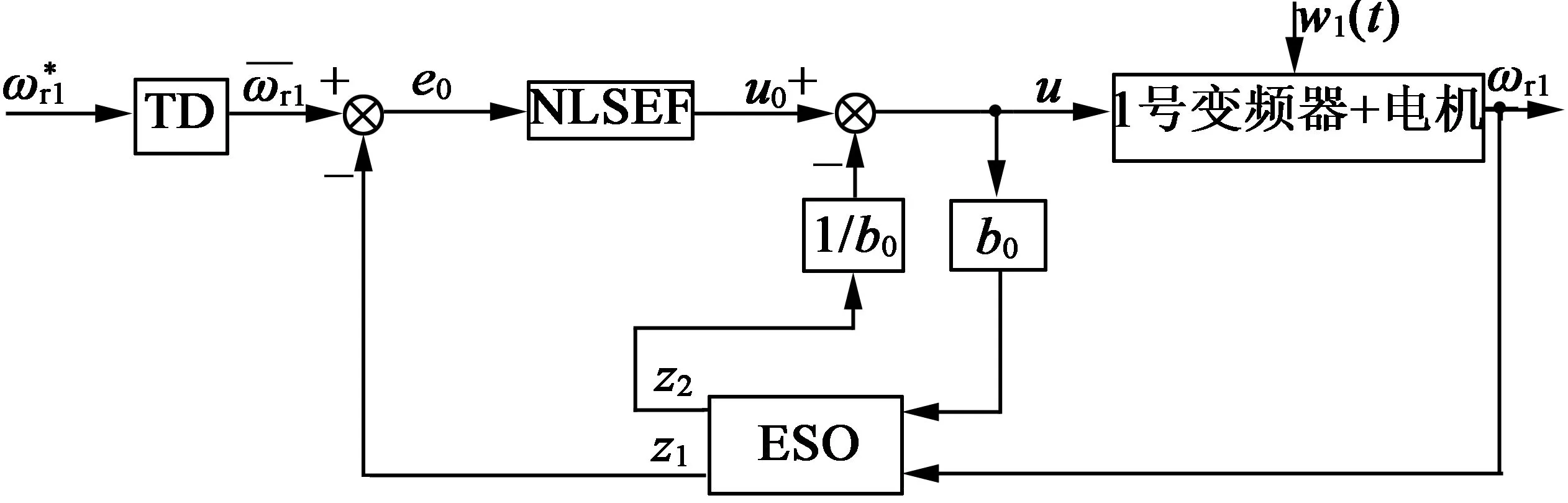

本文主電機速度環選用的是一階ADRC,將交流異步電機轉動慣量變化和負載變化以及一系列不確定因素所引起的擾動均視為總擾動,用ESO觀測后輸入到控制器的前端實現補償。TD,ESO,NLSEF和擾動補償4個環節共同組成了ADRC[9]。由此推出一階速度ADRC控制器的結構圖,如圖2所示。

圖2 一階速度ADRC的結構圖

2 系統的硬件平臺

三電機同步控制系統主要由控制部分、驅動部分、反饋檢測部分以及負載部分組成。

1)控制部分包括一臺PC機和以單片機、DSP和CPLD為控制芯片所組成的三核控制器。控制器和工控機之間用RS-232通訊,用于實現對現場信號的檢測以及上位機實時值顯示和歷史數據曲線的繪制,并對歸檔得到的數據進行逐個分析,以驗證所設計控制器所表現出的各項性能情況,也可以用來作為配置控制器相關參數的依據。控制器中的CPLD與被控對象的3臺變頻器之間采用RS-485通訊,用于將控制器處理好的數據傳輸給變頻器,進而再用變頻器來控制電機,以實現3臺電機的同步協調運行[10]。

文中所設計的三核控制器如圖3所示。由圖3可知,顯示部分包括LCD彩屏顯示和數碼管顯示,彩屏位于控制板上左上角,用以顯示速度和張力的實時數值以及這3個參數歷史數據的曲線繪制,并具有自動刷屏的功能;數碼管位于右上方,用于控制過程中顯示速度值和張力值。速度和張力的給定值可以在程序中直接給定,或者可以通過鍵盤設定張力和速度值,并經過74HC138編碼后輸入單片機處理。SN74LVC8T245芯片是用于將從單片機輸出的5 V的信號轉換為3.3 V信號輸給CPLD進行2個張力的處理。

圖3 控制器

2)驅動部分包括3臺西門子MMV變頻器和3臺交流異步電機,3臺變頻器分別驅動3臺電機。

3)反饋檢測部分包括對速度的檢測和對2個張力的檢測。本文選用圓形的國產YGM-615編碼器,實驗中編碼器輸出的信號時常會帶有毛刺,系統中毛刺的進入會影響每轉脈沖數的計數值,所以在轉速計算之前,必須在編碼器輸出信號后對其濾波,編碼器輸出線經330 Ω電阻降壓為3.3 V,接到CPLD的96號引腳完成軟件濾波。

張力傳感器選用上海毅浦自動化設備有限公司生產的型號為YP-H2的傳感器,將傳感器測出的信號經過AD7705進行模數轉換,得到相應的數字信號輸入給單片機,再經過SN74LVC8T245芯片,將從單片機輸出的5 V的信號轉變為3.3 V信號輸給CPLD進行2個張力的處理。

4)負載部分由3臺電機軸分別與3臺減速機和3臺驅動滾筒同軸連接,3臺驅動滾筒上分別安裝了磁粉制動器,通過給磁粉制動器加激勵電流來模擬實際工況下的負載。

三電機控制網絡采用的是主-從站機制,其中,控制器是由MCU,DSP和CPLD的三核處理器組成,控制器和工控機作為系統主站,3臺西門子MM440作為系統從站。系統整體網絡結構,如圖4所示。

圖4 三電機系統整體網絡結構圖

3 系統的軟件設計

本文設計了一個三核控制器,而這3個控制芯片分別是單片機、DSP和CPLD,利用3個處理芯片的各自優勢,它們之間相互協調達成最終的控制任務。下面將針對這3個處理器所承擔的任務,分別設計其相應的控制程序。

首先,單片機處理器選擇的是STC89C52,主要完成2個張力采集時需要和前端模數轉換芯片進行通信,在張力1采集完成后,需要對張力2進行采集,其過程類似于張力1。下面以張力1為例說明采集的詳細過程:首先AD7705通信端口復位,并使A/D芯片第一個通道初始化,單片機的P3.5引腳通知模數轉換芯片做好準備,等AD7705準備好后,向其通信寄存器寫入一個命令,再從AD7705中讀入一個字節的張力1轉換后的數字量,將讀入的數據放入寄存器中并還原成對應的電壓值,再進行張力2的讀入,至此,完成了張力的采集。

DSP作為主處理器處于系統的核心地位,在整個系統中主要作用有反饋信息的獲取、控制信息的發送和PID或一階ADRC算法的計算,實驗中速度和張力數值的實時顯示以及速度和張力曲線的繪制,整體的流程圖如圖5所示。

由圖5可知,先進行系統配置寄存器的初始化及中斷的初始化,所用中斷引腳為XINT1,初始化通用I/O口,將I/O口配置為輸入輸出口。由于算法中用到的變量、數組等存儲單元較多,編程時采用結構體形式存儲數據,可以使程序閱讀方便、結構清晰,同時在系統上電時要對自抗擾算法的相關數據進行初始化。速度信息采用1個字的信息來表示,2個張力也各是1個字,需要讀取的參數信息一共6個字節。DSP數據接收口是8位并行數據線需要6次才能讀完,每次中斷讀取1個字節。算法對反饋信息的處理程序都發生在中斷子程序中,初始化完成后就進入了等待中斷。當有中斷來臨讀取并口數據線上的數據,接著判斷電機停轉標志位,該標志位由F12或F23大于900 N時引起,防止皮帶過緊崩斷,若是則在下次中斷執行中發送電機停轉指令,否則判斷data_rx_over_flag是否等于“1”,該標志位置“1”代表CPLD發送過來的6個字節的反饋信息接收完畢,若是“0”則跳出中斷,否則先將data_rx_over_flag清零,接著計算接收到的速度、張力數據的實際大小,以便為算法處理提供直觀數據。若是電機的轉速大于600 r/min則給定電機轉速為600 r/min,目的是限制運行速度。計算過實際大小后,接著調用ADRC算法子程序返回調節后的控制量,返回的張力數據經過計算得到實際值。實驗中獲取的張力信號毛刺很多,濾除這些干擾采用一階滯后濾波,濾波后判斷張力是否過大,F12或F23超出900 N將電機停轉標志位stop_flag置“1”,下次中斷程序中發送停轉指令,否則將獲取的張力數據進行張力的ADRC計算,得到第二、三臺電機的頻率字。3臺電機的頻率控制字都得到后,統一通過SPI接口發送給CPLD進而發送給變頻器。程序在執行完一個控制運算周期后,緊接著進入下次控制運算流程。

圖5 DSP程序框圖

CPLD主要實現對編碼器輸出信號的濾波處理、控制器和上位機的通信以及控制器輸出信號與3個西門子變頻器的通信。首先編碼器采集主電機速度脈沖序列,在實際工況下,先對編碼器代入的毛刺進行濾波,而單片機傳輸來的數據則需要經過分揀,編碼器信號和張力信號都要經過合并,也就是將16位的數據寄存器存儲值合并成32位數據進行并行傳輸,數據一方面將傳輸到232模塊發送到上位機;另外將傳輸到數碼管用于張力和速度的顯示。數據還需要傳輸給DSP用于算法的處理,這里CPLD給DSP發出中斷信號,然后進行相關算法的運算。

4 驗 證

為了測試所設計三電機系統同步控制效果,進行基于ADRC算法與PID控制算法下抗負載擾動實驗。在負載實驗中,通過觀察負載改變時,系統中主電機轉速與2個皮帶張力的變化情況。在系統中,設定主電機轉速ωr1給定為300 r/min,張力F12給定為96 N,張力F23給定為72 N,不加負載的情況下使電機空載起動,在80 s的時刻,加載1.3 A的電流給主電機的磁粉制動器,得到使用PID控制器的各參數曲線,如圖6所示。使用ADRC控制器的各參數曲線如圖7所示。

圖6 PID控制

圖7 ADRC控制

由圖6、圖7可知,突然增加負載時,當系統選用PID方案時,則超調為-15.6%,調節時間為7.3 s;當系統選用ADRC方案時,則超調為-6.7%,調節時間為0.73 s。由此可知,采用ADRC控制器時,超調量減少而且調節時間也大大縮短,且在突加負載時,張力F12有負超調,隨后帶來了系統的振蕩。從而得出采用ADRC方案的抗負載擾動能力優于PID。

[1] 張今朝,劉國海,潘天紅.多電機變頻調速同步系統的多模型預測控制[J].控制與決策,2009,24(10):1489-1494.

[2] 於新華.基于DSP+FPGA的多電機同步控制系統研究[D]:北京印刷學院,2011.

[3] 楊士河,劉景林等,基于DSP的多電機協同控制系統設計[J],測控技術,2010,29(6):45-47.

[4] 于凱平,郭宏,吳海洋.采用DSP 和FPGA 多電機速度伺服驅動控制平臺[J],電機與控制學報,2011,15(9):39-43.

[5] 聶宜云,孟凡軍,顏肖平.基于DSP_FPGA架構的嵌入式運動控制平臺設計[J],測控技術,2015,34(5):69-71.

[6] 施文美.基于DSP_CPLD控制結構的礦用蓄電池機車設計[J].儀表技術,2016(8):18-22.

[7] 劉建國.基于DSP+CPLD的全數字脈沖MIG焊機的研制[D].廣州:華南理工大學,2014.

[8] 韓京清.自抗擾控制器及其應用[J].控制與決策,1998,13(1):19-23.

[9] 韓京清.自抗擾控制技術:估計補償不確定因素的控制技術[M].北京:國防工業出版社,2008:342-598.

[10] 王宏波.多電機驅動的帶式輸送機的傳動控制[J].煤礦現代化,2009(5):60-61.