基于現場可編程門陣列并行頻率源的改進方法

徐 躍,簡金蕾,任宏濱,連 可,吉 陽

(1.空軍工程大學防空反導學院,陜西 西安 710051;2.中國電子科技集團公司第十研究所,四川 成都 610036)

?

基于現場可編程門陣列并行頻率源的改進方法

徐躍1,簡金蕾1,任宏濱1,連可2,吉陽1

(1.空軍工程大學防空反導學院,陜西 西安710051;2.中國電子科技集團公司第十研究所,四川 成都610036)

摘要:針對傳統直接數字頻率合成(DDS)電路中相位累加器與波形查找表的工作頻率與高速數模轉換器(DAC)采樣頻率不匹配的問題,提出了基于現場可編程門陣列(FPGA)并行頻率源的改進方法。該方法采用改進的8路并行DDS電路有效地擴展了DDS電路的輸出帶寬;基于并行DDS結構,利用FPGA和高速DAC生成了不同調制模式下的通信信號,并在Vivado2014.2環境下進行測試。實驗表明:該設計具有結構簡單、易于實現、分辨率高等特點,可用于雷達、電子對抗領域中寬頻帶高分辨率信號的產生。

關鍵詞:并行直接數字頻率合成;波形查找表;現場可編程門陣列;調制;高速數模轉換器

0引言

隨著現代電子技術的不斷發展,對于波形合成的輸出帶寬、輸出復雜度等指標要求越來越高。一般的振蕩器因較大的局限性不能滿足要求,為了實現具有頻率轉換速度快、頻率分辨率高、相位噪聲低、變頻相位連續等特性,直接數字頻率合成(DDS)技術應運而生。DDS最早于1971年由美國學者J.Tiemcy、C.M.Radar和B.Gold在《A Digital Frequency Synthesizer》一文中提出。它是繼直接頻率合成技術和鎖相式頻率合成技術之后的新一代頻率合成技術,可真正意義實現任意波形合成[1-3]。

基于單片機和DDS芯片的快速頻率合成方案已不能滿足實際工程的需要[4],而FPGA技術在近幾年得到迅速發展并以其可擴展性高、功耗低、開發周期短等特點得以廣泛應用。特別是通過復用高性能IP核可大大簡化FPGA電路設計[5],已逐漸成為DDS電路設計的不二選擇。一些學者即通過在FPGA硬件平臺進行DDS的電路設計,具有一定的靈活性,一方面降低了開發成本,另一方面提高了頻率合成器的性能。但也存在諸多問題,如文獻[6]和文獻[7]信號輸出僅為單路輸出。文獻[8]也僅設計了雙路DDS并行輸出。文獻[9]設計了32路并行輸出,但信號帶寬較窄,且輸出頻率低[6-9]。本文針對上述問題,提出了基于現場可編程門陣列并行頻率源的改進方法。

1現場可編程門陣列并行頻率源

1.1DDS基本原理

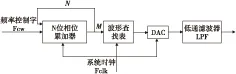

DDS技術是從相位的角度出發,根據相位幅度增量直接合成所需波形。其結構模型如圖1所示[10]。

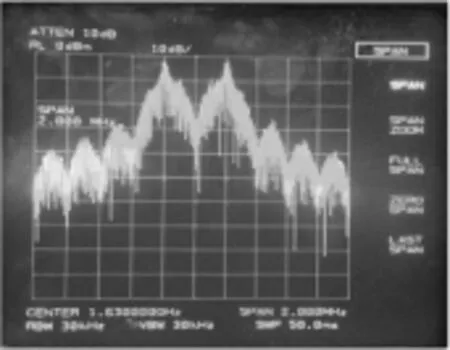

圖1 DDS 基本結構Fig.1 The Basic Structure of DDS

由圖1可知,DDS電路由系統時鐘Fclk、N位相位累加器、波形查找表、數模轉換器和低通濾波器等組成。其中,Fclk 代表時鐘頻率源,Fcw 代表頻率控制字,N代表頻率控制字 Fcw 的字長,M代表波形查找表尋址碼的位寬,D代表波形查找表輸出數據的位寬,也即數模轉換器的字長。在系統時鐘的控制下,N位累加器開始進行累加,步進為頻率控制字Fcw。截取相位累加器輸出的高M位作為對波形查找表進行尋址的相位地址,經過波形查找表后輸出對應的D位幅度值,完成相位到幅度的轉換。由于在每個時鐘脈沖下均可產生M位波形查找表尋址地址碼,這些尋址碼可用來查找出波形查找表中存儲的一一對應的D位離散波形幅度值數據。因此,當累加器一個周期運算結束后,由波形查找表輸出的所有離散數據便構成了離散的輸出信號波形[11]。輸出的波形幅度值經過數模轉換器構成的保持電路保持信號輸出后,變成相應的階梯型模擬信號,再由低通濾波器濾除雜散分量,保證輸出純凈的波形,從而最終輸出的信號即為實際所需合成波形信號。圖2所示為DDS工作的波形示意圖。

圖2 DDS波形示意圖Fig.2 DDS Waveform Diagram

1.2DDS精度分析

以正弦波W(t)為例[12],

Wout=Asin(2πfoutt+φ)

(1)

由上式可知,在振幅A和初始相位φ已知的前提下,可以得到正弦信號Wout的相位φ(t)和頻率fout有如下的一一對應關系:

φ(t)=2πfoutt

(2)

現假設系統采樣時鐘為fclk,則兩個相鄰采樣點的相位差為:

(3)

將上式的Δφ對應到數字形式中,假設DDS系統位數為N,則在數字形式對應的二進制相位碼為2N。由于一個周期的相位為2π,所以,最小相位間隔為2N/2π,也即相位分辨率。那么,相位增量為:

(4)

對上式進一步處理可得,系統輸出信號頻率與采樣頻率之間的關系為:

(5)

輸出信號的頻率分辨率為:

(6)

根據Nyquist采樣定律,系統允許輸出的最大頻率值為:

(7)

但在實際工程應用中,一方面,理想的低通濾波器無法實現;另一方面,為獲得比較理想的連續波形,一般輸出信號的最高頻率為采樣頻率的40%。

綜上所述可以看出,為了使DDS電路達到更到的精度,增加相位累加器的位數N即可。但如果一味地將累加器的 N 位輸出全部用來作為波形查找表的尋址地址,那么波形查找表需要2N個數據點的

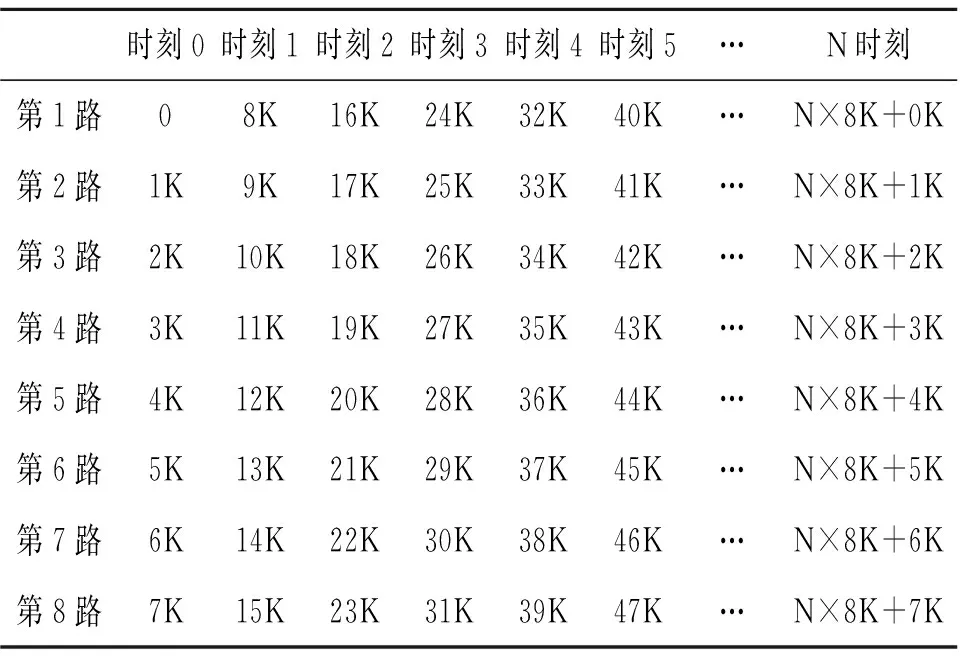

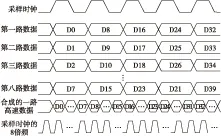

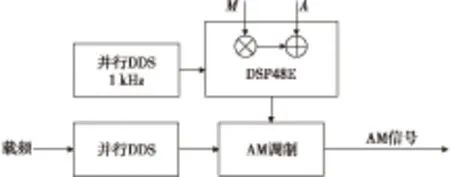

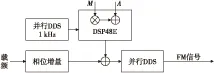

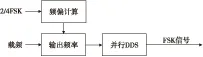

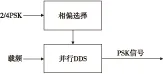

存儲容量。以32位的累加器為例,存儲容量將達到4G。在實際應用中往往無法實現或者實現代價過高,同時影響系統速度。因此,為了在兼顧合適的波形查找表容量下保證頻率分辨率,通常情況截取高M位(M 2并行頻率源的改進方法 根據DDS工作原理可知,其各個功能模塊均在系統時鐘的上升沿更新數據,也即該電路可等效為一同步時序電路。因此,相位累加器在第一個時鐘上升沿產生第一個相位值Phase1,該相位值作為波形查找表的輸入對其尋址獲取第一個波形數據Data1。同理,在第二個時鐘沿上升時,DDS電路可產生第二個相位值Phase2和數據Data2。在后面時刻的波形數據生成以此類推。圖3所示為DDS波形產生時序圖。 圖3 DDS波形時序圖Fig.3 DDS waveform sequence diagram 從波形圖中可以看出,隨著采樣頻率的提高,由于電路中相位累加器和波形查找表工作頻率的限制,導致需多個采樣時鐘去生成一個波形相位或者一個波形數據,使得采樣時鐘與波形相位值、波行數據無法實現同步。而目前DAC的工作頻率早已經超過GHz,這就意味著相位累加器、波形存儲器等單元的處理速度也必須達到GHz才能保證系統正常工作。但是由于FPGA自身結構的特殊性,相比于高速DAC,其工作頻率較低。也就是說DDS電路中的DAC的工作頻率遠遠大于相位累加器和波形存儲器的工作頻率,因此DDS電路設計的關鍵在于如何更快地為高速DAC提供數據。針對這一問題,本文在圖1所示的DDS傳統結構的基礎上設計了8路并行的DDS電路。在系統采樣時鐘不變的前提下,將整個DDS電路的處理速度提高了8倍。利用FPGA實現的8路并行DDS的設計框圖如圖4所示。 該設計的基本思想是將一路高速數據轉化為8路并行的低速數據,然后通過并串轉換技術再將多路數據合成一路,使原始信號的得以重現,從而實現數字處理模塊和數模轉換器之間的速度匹配。 圖4 并行DDS實現框圖Fig.4 DDS Implementation Diagram 假設DAC的工作時鐘為fs,期望信號的相位增量為K,則各時刻的信號的相位為NK,N=0,1,2,…,8。為了直接產生數字中頻或射頻信號,FPGA利用并行處理技術以產生期望的信號。假設FPGA內部進行8路并行相位累加處理,各路工作時鐘為fclk=fs/8 ,則各時刻每一路信號的相位值如表1所示。 表1 各時刻每一路信號 由表1可以看出,相鄰兩點之間的相位差為固定值K。可見,波形的輸出相位具有可預測性,通過輸出多個相位值的同時對波形查找表進行尋址,完全可以實現在一個采樣時鐘上升沿同時產生多個波形數據。該電路中的DDS系統采樣率為8×225MHz,則在第8n(n=1,2,3,…)個時鐘上升沿,可以同時產生8路的波形相位值,將獲取的波形相位值再對8路的波形查找表進行尋址,可以得到8路并行的波行數據。最后將8路低速數據轉換為一路高速數據如圖5所示。 圖5 8路并串轉換數據波形Fig.5 8 roads parallel-serial conversion data wave 如上圖所示,在單個DDS電路中,原來需要8個時鐘才能獲取的數據現在一個時鐘即可實現,也即相位累加器和波形查找表的工作頻率可降為原來工作頻率的1/8。 3并行頻率源的調制模式 3.1AM調制 AM調制是用調制信號去控制高頻載波的振幅,使其按照調制信號的規律而變化的過程。本文采用雙DDS電路分別產生載波和調制波形。 假設調制信號的時域表示為 (8) 載波信號的時域表示為 (9) 則AM信號的時域表示為 (10) 其中A為疊加的直流分量,M調制深度。 參數設置如下: 1)單音調幅信號頻率:fm=1kHz; 2)中頻信號:fc=70MHz; 3)調制深度:M=60%; 4)疊加直流分量:A=1。 根據系統參數設置要求,AM信號的FPGA實現框圖如圖6所示。 圖6 AM調制實現框圖Fig.6 AM Modulation Implementation diagram 3.2FM調制 FM信號是利用調制信號控制振蕩器的頻率,從而使其按調制信號的規律線性變化。 假設調制信號的時域表示為 (11) 載波信號的時域表示為 (12) 則FM信號的相位為 (13) 其中,ωc為載頻信號的角頻率,M為調制深度。 參數設置如下: 1)單音調幅信號頻率:fm=1kHz; 2)中頻信號:fc=70MHz; 3)調制深度:M=60%; 根據系統參數設置要求,FM信號的FPGA實現框圖如圖7所示。 圖7 FM調制實現框圖Fig.7 FM Modulation Implementation diagram 3.3FSK、PSK調制 由于DDS電路可以靈活控制輸出波形相位和頻率,因此實現數字調制相對簡單,只需設置兩個頻率控制字,在調制信號作用下不斷切換兩個頻率控制字,即可實現FSK調制。根據調制信號的相位值實時改變載波信號相位值可實現PSK調制。其在FPGA實現原理如圖8、圖9所示。 圖8 碼速率為1 MHz的FSK信號實現框圖Fig.8 FSK Implementation diagram at 1MHz 圖9 PSK信號實現框圖Fig.9 PSK Implementation diagram 4改進方法的驗證 采用FPGA+DAC架構所實現的圖3所示的并行DDS電路。系統邏輯部分硬件實現原理框圖如圖10所示。 圖10 邏輯部分硬件實現原理框圖Fig.10 Hardware Implementation Diagram 其中信號數據產生由FPGA實現,根據來自與ARM互聯的并行接口下發的參數,包括模擬目標方位、調制模式、距離配置等。 數據分8路進行實時數據計算,而后經由并串轉換將多路低速數據轉換為一路高速數據送至高速DAC,最后通過射頻接口輸出所需信號。 該系統能夠實現AM、FM、FSK、PSK等信號的合成,由于篇幅原因,圖11—圖16所示為頻率為600 MHz的基帶信號頻譜,載頻均為1.63 GHz的AM調制信號頻譜、FSK調制信號頻譜及其相應的FPGA時域仿真波形。 圖11 600 MHz的正弦信號頻譜Fig.11 Sinusoidal Signal Frequency Spectrum at 600 MHz 圖12 基帶信號時域波形的Modelsim仿真Fig.12 Baseband signal time domain waveform of the Modelsim simulation 圖13 AM信號頻譜(載頻1.63 GHz)Fig.13 AM Signal Frequency Spectrum (Carrier is 1.63 GHz) 圖14 AM信號時域波形的Modelsim仿真Fig.14 AMsignal time domain waveform of the Modelsim simulation 圖15 FSK信號頻譜(載頻1.63 GHz)Fig.15 FSK Signal Frequency Spectrum(Carrier is 1.63 GHz) 圖16 FSK信號時域波形的Modelsim仿真Fig.16 FSK signal time domain waveform of the Modelsim simulation 由上述測試結果不難看出,所生成的基帶信號頻率為600 MHz,并實現了AM、FSK等不同調制模式下的信號合成。輸出信號頻率可在1.6~1.7 GHz之間進行參數配置,實現了寬頻帶、輸出頻率高的指標要求。 5結論 本文提出了利用FPGA設計8路并行DDS電路的改進方法。該方法采用8路并行DDS電路在225 MHz的內部時鐘頻率下可以為DAC提供1.8 GHz的數據采樣率,通過并行方式解決了單路DDS電路在225 MHz下的工作頻率與高速DAC工作頻率1.8 GHz不一致問題,而且在相同的條件下,相較于傳統的DDS電路在原始頻率范圍為200~212.5 MHz的基礎上擴展到1.6~1.7 GHz,也即在單路DDS電路上擴展了8倍。同時設計產生了分辨率為0.052 Hz的穩定的信號,有效解決了數字處理模塊與數模轉換器處理速率不匹配的問題,擴展了輸出帶寬。實驗表明,該系統實現了信號頻率可調、高分辨率、高精度信號合成且能產生AM、FM等不同調制模式下的信號。擬在本系統設計的基礎上進一步增加并行處理的通道數,即可通過更低的速率生成高頻信號。該系統滿足設計指標要求,具有一定工程價值,可在寬頻帶高分辨率信號生成中廣泛使用。 參考文獻: [1]Tiemcy J, Radar C M, Gold B. A Digital Frequency Synthesizer[J]. IEEE Trans. Audio Electroacoust,1971,19(8):48-57. [2] Huang XiangSheng, Yang ZhanCai, Hu ShiWen. The design and implementation of digital function generator based on DDS and FPGA[J]. East China Institute of Technology Periodical, 2009, 32(4):390-393. [3] 蘇淑靖,張凱琳,劉科生. 程控調幅多路并行信號源[J].探測與控制學報, 2012,34(3):67-70. [4] 李可為,張玉平. 采用低端FPGA實現直接數字頻率合成的優化設計[J]. 電訊技術,2012,52(5):818-821. [5] 馮永浩,李云,吳曉麗. Xilinx IP核在2FSK調制解調器FPGA設計中的應用[J]. 電子器件,2014,37(3):469-713. [6] 曹鄭蛟,滕召勝,李華忠,等. 基于FPGA的DDS信號發生器設計[J]. 計算機測量與控制,2011,19(12):3175-3177. [7] 劉艷昌,左現剛,李國厚. 基于FPGA的多功能信號發生器設計與實現[J], 制造業自動化:2014,36(10):100-104. [8] 鄧耀華,吳黎明,張力鍇,等. 基于FPGA的雙DDS任意波形發生器設計與雜散噪聲抑制方法[J]. 儀器儀表學報,2009,30(11):2255-2258. [9] 張凱琳,蘇淑靖,劉科生.基于FPGA的DDS多路信號源設計[J]. 電測與儀表,2011,48(3):63-65. [10]楊韜儀,王超,夏艷琴. 基于并行DDS技術的寬帶通信信號模擬方法[J]. 微電子學,2014,44(6):790-793. [11]胡安燦. 基于FPGA的DDS設計與實現[D]. 上海:上海師范大學,2014. [12]蔣智辰. 基于DDS 芯片AD9852 的雷達回波模擬器設計[J]. 電子科技,2014,27(3):71-76. Improved Method of Parallel DDS Based on FPGA XU Yue1, JIAN Jinlei1, REN Hongbin1, LIAN Ke2, JI Yang1 (1.Air Force Engineering University, Air and Missile Defense College, Xi’an,710051,China;2.China Electronic Technology Group Corporation tenth Institute, Chengdu 610036, China) Abstract:Aiming at the disagreement among the frequency of phase accumulator, wave look-up table, and the frequency of high speed DAC in traditional DDS, an improved method of parallel DDS based on FPGA was put forward. The method took use of improved paralled DDS circuit of 8 channels to design, which expended output band effectively. Different modulation mode communication signals were generated via FPGA and high speed DAC based on parallel DDS. It was performed under the environment of Vivado 2014.2. The testing results showed this design was of simple construction, easy implementing and high frequency, which could be used in wide band high frequency signal generation. Key words:parallel direct digital synthesis; wave lookup table; FPGA; modulation; high-speed digital to analog converter 中圖分類號:TN911.7 文獻標志碼:A 文章編號:1008-1194(2016)02-0082-06 作者簡介:徐躍(1990-), 男,山東臨沂人,碩士研究生,研究方向:目標模擬器設計。E-mail:286696173@qq.com。 *收稿日期:2015-10-15