EAPR 設計中動態模塊間總線宏實現方法

□趙 鵬 申正義 張 勇

現階段,高密度FPGA 生產工藝實現難度增大,而且在使用時布線復雜度也呈幾何數上升,然而局部動態可重構(Dynamic Partial Reconfiguration,DPR)技術的提出解決了這個問題。局部動態可重構是指重新配置時僅配置FPGA 部分區域,重構過程中,FPGA 其余部分的工作不受影響。該方式減少了單元數目和重構范圍,從而大大縮短了FPGA 的重構時間。

一、FPGA 局部動態可重構中總線宏簡介

局部動態重構中,系統被劃分為靜態模塊和動態模塊,其中動態模塊即是可重構部分。靜態模塊間的通信可以通過簡單的直接路由實現,對于動態與靜態模塊間和動態與動態模塊間的通信就由總線宏來實現。局部動態重構設計,總線宏部分作為難點不易實現,文獻[1]中提出了總線宏的分類和結構分析,文獻[2]中提出的總線宏設計流程是基于三態緩沖器(TBUF)針對老式芯片的設計方法,文獻[3]中提出了EAPR 設計流程中的基于slice 的總線宏設計方法,但其僅局限在靜態模塊和動態模塊間的總線宏通信,未涉及動態模塊間的總線宏設計,所以局限了EAPR 設計的靈活性,不利于EAPR 應用在更為復雜的電路設計。

二、動態模塊間總線宏實現方法

本設計方法是以ML505 開發板為硬件實驗平臺,以ISE9.1i 和PlanAhead9.2.7 系列軟件為依托進行動態模塊間的總線宏通信研究。與傳統的總線宏設計不同,EAPR 的總線宏不再需要復雜的編程,而是通過模塊例化,在軟件中進行可視化的操作實現。下面通過一個實例具體解析動態模塊間總線宏的實現過程。

(一)獲取官方總線宏nmc 文件。首先在Xilinx 官網注冊用戶,進入總線宏下載頁選則相應芯片,由于這里采用的是ML505 開發板,所以選擇XC5VLX50T 系列,而后下載得到busmacro_xc5v_async.nmc 文件[4]。

(二)總線宏模塊的例化與連線。在EAPR 設計方法中,總線宏必須在ISE9.1i 軟件中進行HDL 設計描述和綜合,只有建立black box 并定義輸入輸出才可以在后續程序中調用。通過頂層文件對總線宏模塊的例化程序如下:

module busmacro_xc5v_async(input0,input1,input2,input3,output0,output1,output2,output3);

input input 0,input 1,input 2,input 3;

output out0,out1,out2,out3;

endmodule

通過前期實驗,針對動態模塊間的通信僅使用一級總線宏,在步驟方法一致情況下會在最后的檢測分析中反復報錯,無法繼續進行工程設計,且在其他類文獻中沒有相應解決方法。嘗試性地為兩個動態模塊各分配一級總線宏,在HDL 程序中,我們定義了bm2 和bm4 兩個總線宏的連線,聲明了四個端口(bm2_bm4[0.1.2.3]),相應Verilog 代碼如下:

busmacro_xc5v_async bm2(

.input0(prm_bm2[0]),

……

.input3(prm_bm2[3]),

.output0(bm2_bm4[0]),

……

.output3(bm2_bm4[3])

);

busmacro_xc5v_async bm4(

.input0(bm2_bm4[0]),

……

.input3(bm2_bm4[3]),

.output0(bm2_prm1[0]),

……

.output3(bm2_prm1[3])

);

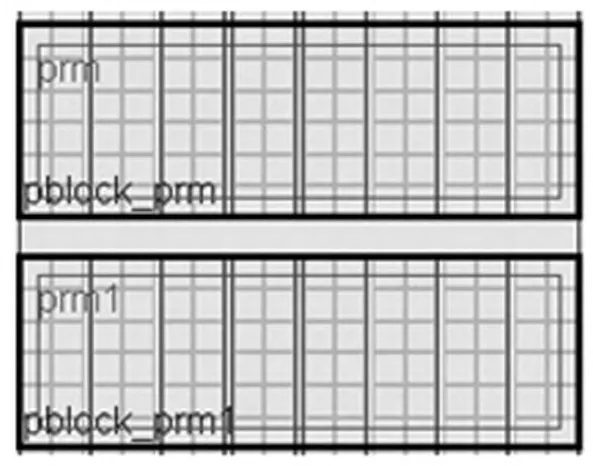

(三)重構區域的建立和總線宏設置。在經過綜合后生成網表文件,進入PlanAhead9.2.7 建立工程[5]。如圖1,利用該軟件可視化的優點在芯片中分配兩個動態可重構區域PRM 和PRM1,區域大小取決于后續應用于該動態區域需要的硬件單元數量,且動態區域相互獨立不能交集。

圖1 分配動態可重構區域

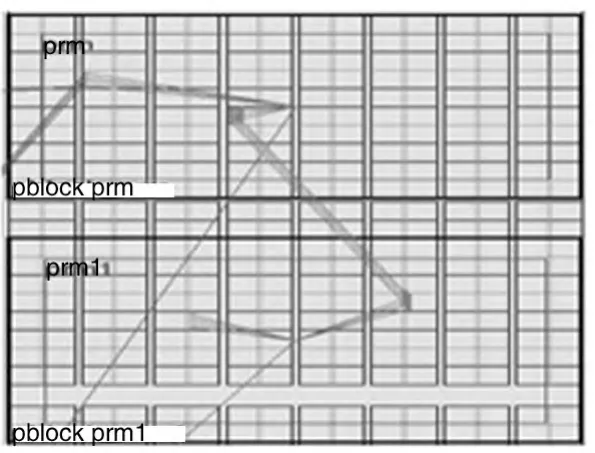

重構區域設置完成后在Netlist 窗口下,選擇總線宏bm2,并通過單擊菜單欄中Create Site Constraint Mode圖標 將其激活,然后將其拖置于動態區域prm 中。bm4 的放置區域為prm1,放置方法同bm2,如圖2 中兩個總線宏都設置好后可以看到建立在動態區域間的總線宏通信連線。

圖2 動態模塊間總線宏連線

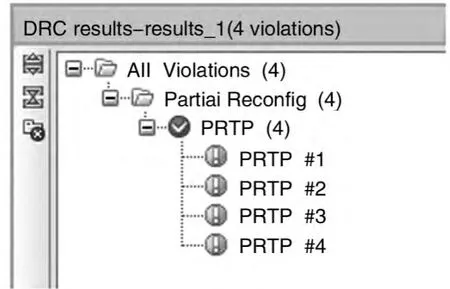

三、檢測與分析

在端口和時鐘都設置成功后,EAPR 設計的檢測部分依然是在PlanAhead9.2.7 軟件環境下完成的。PlanAhead9.2.7包含有設計規則檢查工具(Design Rule Check,DRC),我們可以通過工具欄中“Tools -RunDRC”選項,如果工程符合設計規則在DRC Results 中將顯示檢查通過,如圖3,僅有四個警告是由于四個端口懸空造成,所以可以得出結論應用此類方法動態模塊間的總線宏可以實現。

圖3 工程檢測與分析圖

四、結語

本文提出了一種基于EAPR 技術的動態模塊間總線實現方法。通過為兩個動態模塊分別配置一級總線宏的方式完成了EAPR 設計,并通過分析仿真驗證了新方法的正確性,提高了EAPR 在工程上應用的靈活性,拓寬其使用范圍,具有一定推廣性。

[1]喬守明,祝洪珍,王偉.動態重構中總線宏的結構與實現[J].開發研究與設計技術,2007

[2]趙秋桂,段青亞.FPGA 動態局部可重構中基于TBUF 總線宏設計[J].嵌入式技術,2009

[3]肖松,李躍華,張金林.一種DPR 中總線宏的設計方法[J].電子設計工程,2011

[4]Xilinx Inc.Early Access Partial Reconfiguration User Guide[EB/OL].2006 -3 -6.http://www.xilinx.com/.

[5]Brian Jackson.Partial Reconfiguration Design with PlanAhead 9.2[EB/OL].2007 -8 -2.http://www.xilinx.com/.