基于FPGA的多通道高速信號采集器的設計

廣州海格通信技術股份有限公司 毛 炎 羅繼鴻

引言

隨著電子技術的高速發展,數字系統被廣泛的應用于工業、醫療、軍事、科技等領域,高速數據采集系統已成為數字系統重要組成部分。傳統的信號采集設備,采用單片機或DSP為主要控制器,由于系統時鐘頻率低,接口種類少,造成系統采集通道數有限,采集速率低,接口種類單一,靈活性差。基于FPGA硬件可定制的特點,所有功能利用硬件實現,可有效解決以上問題。使得產品采集精度和速率大幅提高,靈活性和可擴展性得以優化。同時利用FPGA可現場編程的特性可方便實現系統的遠程維護和升級。

1.多通道數據采集器系統架構

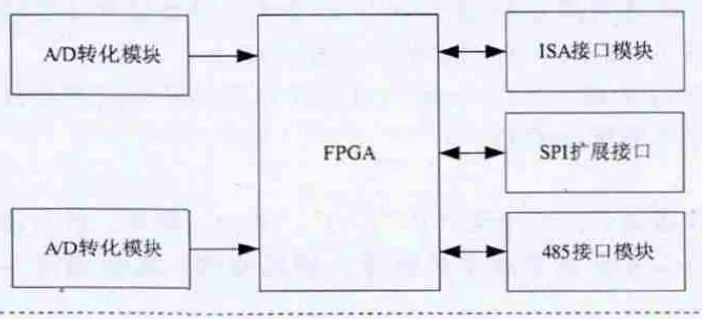

數據采集器主要由6部分組成,它包括兩路A/D轉化模塊,FPGA處理模塊,ISA接口模塊,485接口模塊,SPI擴展口組成的通信接口選擇模塊。如圖1所示。

圖1

FPGA的主要任務是生成控制信號和驅動系統各部分的時鐘信號,完成整個系統的邏輯控制以及A/D轉化模塊,485接口,ISA接口,SPI接口芯片組的驅動。

1.1 FPGA芯片概述

FPGA采用了Atlera公司的EP3C25F256。該芯片內部包含24624個邏輯單元,608256bit的RAM存儲器,66個乘法器,4個內置鎖相環可用I/O口182個。由于AD9241轉換速率高數據無法實時上報可利用內部的RAM作為緩存區儲存數據。FPGA預留SPI總線接口可與單片機、DSP、ARM等芯片直接連接,用做功能擴展、數據傳遞,同時初始化系統。

1.2 485接口模塊

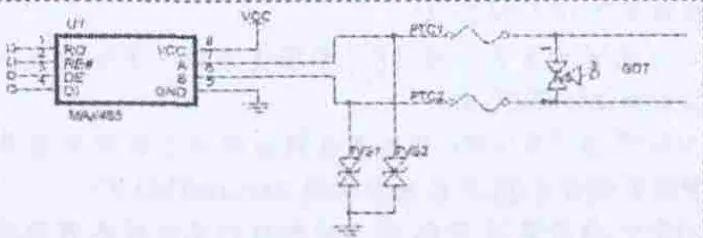

RS485總線采用平衡雙絞線作為傳輸媒介最遠傳輸距離可達1219米以上,可實現系統的遠程控制和數據交互并且能夠進行遠程系統更新升級,同時485總線可多機并聯,從而能夠實現一臺核心服務器控制多部數據采集器的功能。RS485標準通常作為一種相對經濟、具有相當到噪聲抑制、相對高傳輸速率、傳輸距離遠,并且RS485電路控制方便、成本低廉。由于RS485通信距離遠,傳輸電纜周圍電磁環境復雜,所以需要對485總線進行防浪涌,防雷擊保護,保護電路如圖2所示。

圖2

電路采取了兩級防護方案,其中第一級氣體放電管GDT用于瀉放大部分電流。中間PTC熔絲電阻為第一級與第二級之間的耦合器件,同時可限制部分電流。第二極保護采用了鉗位電壓更為精準的TVS管,將浪涌殘壓將至最低。

1.3 A/D轉換模塊

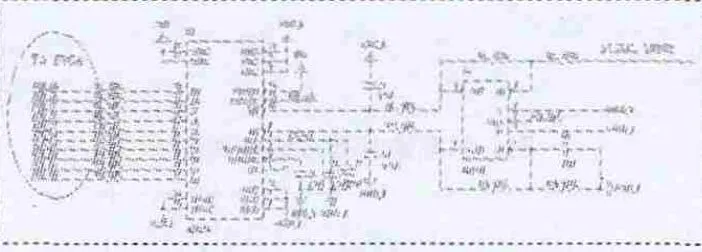

A/D轉換模塊采用AD9214芯片,該芯片采集速率最高可達并行105M,分辨率10位。支持模擬差分信號輸入,配合單端轉差分芯片AD8138可極大的提高A/D模塊的抗干擾能力,芯片接口電路如圖3所示。

圖3

電路中AD8138可將單端信號轉換為差分信號,提高了小信號的識別能力,增強了電路抗干擾能力。

AD9214可通過第13管腳ENCODE控制采樣速率,最高可達105M,由于采樣速率較高,需要對D0—D9管腳進行等長走線和控制50ohm阻抗處理AD9214芯片的接口時序如圖4所示:

圖4

由此可知,主芯片讀取的數據為6個周期前芯片所轉化的數據,系統啟動后需等待6個時鐘周期才可采集數據

1.4 ISA總線接口

ISA是IBM PC兼容機上的一種總線,系統時鐘頻率通常在4.77MHz~8MHz內選擇,最高頻率為8.3MHz。當今大部分工業控制計算機都設置了ISA接口,因此用戶通過ISA總線,可方便快捷的在采集器和工控機之間進行數據交互。但由于EP3C25F256采用3.3V電源供電,ISA接口的標準電平為5V,FPGA無法直接與ISA總線連接。需外加電平轉化芯片NXP的74LVC245。

2.多通道數據采集卡邏輯設計

2.1 設計工具

本設計采用Altera 公司提供的 QuartusⅡ作為開發平臺。該軟件是綜合性PLD/FPGA開發軟件,支持原理圖、VHDL、Verilog HDL、AHDL等多種設計輸入形式,內嵌綜合器和仿真器,同時為第三設計工具提供無縫接口為用戶提供多樣的設計工具和設計方法。FPGA的主流設計語言通常有VHDL和Verilog HDL,由于Verilog HDL使用習慣更接近于C語言,使用更加簡單,故本設計采用Verilog HDL作為開發語言。

2.2 系統工作流程圖

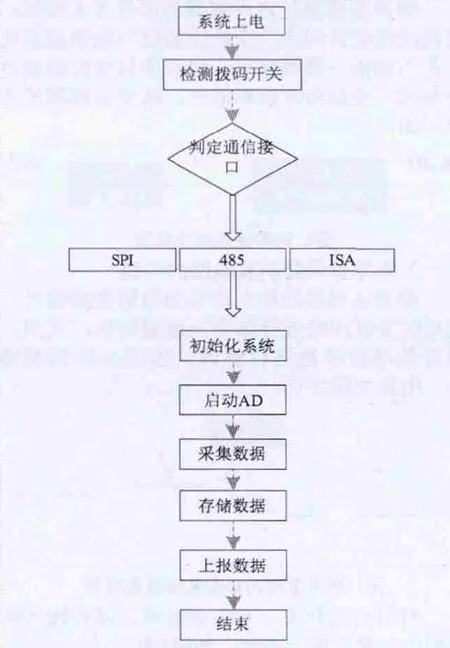

數據采集卡工作流程如圖5所示。

圖5

3.應用與測試

測試方法:

圖6

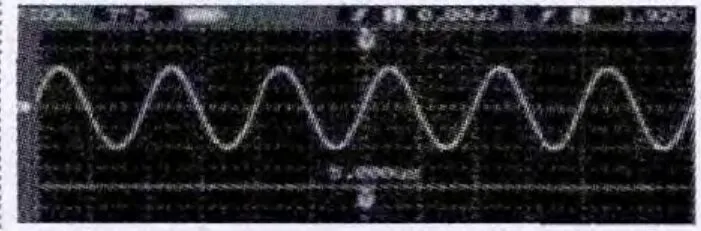

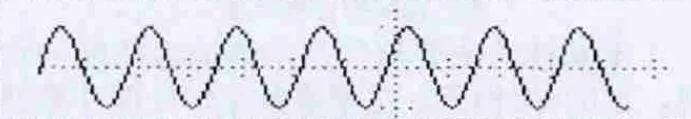

通過ISA總線采集數據上報PC,通過Visual C++等軟件可方便的編寫軟件。接收數據后結果如圖7所示:

圖7

實測結果,與示波器測量的結果基本一致,由此看出,本系統能夠完成高速數據采集的功能。

[1]蘇旭武,楊光友,程良明等.一種基于ISA 總線的FPGA在線配置方法[J].機械與電子,2005,05:47-49.

[2]周振安,范良龍.數據采集系統的設計與實踐[M]北京:地震出版社,2005.

[3]蔣學東.基于FPGA實現多路模擬信號自適應采集系統[J]現代電子技術包,2010,8.

[4]徐慶元,張天序,鐘勝.基于USB總線的高速視頻采集系統設計[J].微計算機信息,2006.