采用抗混疊濾波器的高性能、12 bit、500 MS/s 寬帶接收機(CN0238)

ADI公司

電路功能與優勢

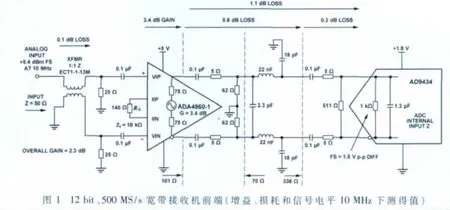

圖1所示電路是基于超低噪聲差分放大器驅動器ADA4960-1和 12 bit、500 MS/s模數轉換器 AD9434的寬帶接收機前端。因是原理示意圖,未顯示所有連接和去耦。

三階巴特沃茲抗混疊濾波器基于放大器和ADC的性能以及接口要求而優化。由濾波器網絡、變壓器和其他阻性元件引起的總插入損耗僅為1.2 dB。整體電路帶寬為290 MHz,通帶平坦度為1 dB。在140 MHz模擬輸入下測得的SNR和SFDR分別為64.1 dBFS和70.4 dBc。

電路描述

該電路接收單端輸入并使用寬帶寬(3 GHz)M/A-COM ECT1-1-13M 1:1變壓器將其轉換為差分信號。5 GHz ADA4960-1差分放大器的差分輸入阻抗為10 kΩ。通過選擇外部增益設置電阻RG,增益可在0 dB~18 dB范圍內調整。差分輸出阻抗為150 Ω。

ADA4960-1是AD9434的理想驅動器,通過低通濾波器可在ADC中實現全差分架構,提供良好的高頻共模抑制,同時將二階失真產物降至最低。ADA4960-1根據外部增益電阻提供0 dB~18 dB的增益。此電路中使用3.4 dB增益補償濾波器網絡(1.1 dB)和變壓器(0.1 dB)的插入損耗,從而提供2.3 dB的總信號增益。約5.4 dBm的輸入信號在ADC輸入端產生滿量程1.5 Vp-p差分信號。

抗混疊濾波器采用標準濾波器設計程序設計出的三階巴特沃茲濾波器。選擇巴特沃茲濾波器是因為它在通帶內具有平坦響應。三階濾波器產生1.05的交流噪聲帶寬比,可借助多種免費濾波器程序進行設計,例如NuhertzTechnologiesFilterFree (hwww.nuhertz/filter)或Quite Universal Circuit Simulator(Qucs)Free Simulation(www.qucs.sourceforge.net)。

為了實現最佳性能,ADA4960-1應載入100 Ω的凈差分負載。5 Ω串聯電阻將濾波器電容與放大器輸出隔離開,62 Ω電阻與下游阻抗并聯,當加入10 Ω串聯電阻時可產生101 Ω的凈負載阻抗。

5 Ω電阻與 ADC輸入串聯,將內部開關瞬變與濾波器和放大器隔離開。511 Ω電阻與ADC并聯,用于降低ADC的輸入阻抗,使性能更具可預測性。

三階巴特沃茲濾波器采用70 Ω的源阻抗、338 Ω的負載阻抗和360 MHz的3 dB帶寬設計而成。

常見變化

對于需要更少帶寬、更高雜散性能和更低功耗的應用,可使用ADA4927-1/ADA4927-2或 ADA4938-1/ADA4938-2。ADA4927-1帶寬為2.3 GHz,僅使用20 mA的電流,而 ADA4938-1帶寬為 1.0 GHz,使用 37 mA的電流。

對于需要更低分辨率的應用,8 bit、500 MS/s AD9484與AD9434引腳兼容。AD9484在250 MHz模擬輸入頻率下的SNR為47 dBFS。

對于需要更低采樣速率的應用,12 bit、170(MS/s)/210(MS/s)/250(MS/s)AD9230是與AD9434引腳兼容的ADC,且具有大致相同的動態性能。

對于需要數字預失真(DPD)觀測的應用,也可考慮12 bit、500 MS/s 的 AD6641該產品具有片內16 k×12 bit FIFO。

閱讀本文更多細節請訪問:

http://comm.ChinaAET.com/ADI/Circuit201205.html