Turbo乘積碼編碼器的FPGA設(shè)計(jì)與實(shí)現(xiàn)

咸陽(yáng)職業(yè)技術(shù)學(xué)院 史亞維 楊 斌

Turbo乘積碼編碼器的FPGA設(shè)計(jì)與實(shí)現(xiàn)

咸陽(yáng)職業(yè)技術(shù)學(xué)院 史亞維 楊 斌

Turbo乘積碼(Turbo Product Codes)是一種先進(jìn)的前向糾錯(cuò)(FEC,F(xiàn)orward Error Correction)信道編碼,糾錯(cuò)性能好,編碼效率高,同時(shí)由于其編碼構(gòu)造采用了線性分組碼,所以譯碼方法簡(jiǎn)單,實(shí)現(xiàn)復(fù)雜度低。本文對(duì)Turbo乘積碼編碼技術(shù)進(jìn)行了研究,給出了編碼器的FPGA設(shè)計(jì)實(shí)現(xiàn)方案,該編碼器的設(shè)計(jì)在Xilinx公司Virtex-II系列的FPGA平臺(tái)上進(jìn)行了實(shí)驗(yàn)驗(yàn)證。實(shí)驗(yàn)結(jié)果表明,本設(shè)計(jì)的編碼器滿足預(yù)期指標(biāo)要求。

Turbo編碼;前向糾錯(cuò)碼;FPGA

1.引言

隨著微電子技術(shù)、通信技術(shù)和計(jì)算機(jī)技術(shù)的發(fā)展,新的通信業(yè)務(wù)和信息業(yè)務(wù)不斷涌現(xiàn),用戶對(duì)信息傳輸?shù)馁|(zhì)量要求不斷提高。由于通信信道固有的噪聲和衰落特性,或者存在存儲(chǔ)媒介的缺陷等原因,信號(hào)在信道傳輸(或存/取)過(guò)程中,必然會(huì)受到影響從而產(chǎn)生失真。因此通常需要采用差錯(cuò)控制編碼技術(shù)來(lái)檢測(cè)和糾正失真引起的傳輸錯(cuò)誤。Turbo乘積碼是一種先進(jìn)的前向糾錯(cuò)信道編碼,糾錯(cuò)性能好,編碼效率高,同時(shí)由于其編碼構(gòu)造采用了線性分組碼,所以譯碼方法簡(jiǎn)單,實(shí)現(xiàn)復(fù)雜度低。因此本文主要介紹Turbo乘積碼的編碼器技術(shù),提出了一種編碼器的FPGA設(shè)計(jì)實(shí)現(xiàn)方案。

2.Turbo乘積碼編碼技術(shù)

2.1 Turbo乘積碼的編碼方式

按照構(gòu)成碼子碼種類的不同,Turbo乘積碼可分為Reed Solomon乘積碼,BCH乘積碼,加了一個(gè)奇偶校驗(yàn)比特后構(gòu)成的擴(kuò)展Hamming乘積碼以及單一的奇偶校驗(yàn)乘積碼。乘積碼由一系列多維的(n,k)分組碼構(gòu)成,在二維或三維空間使用不同長(zhǎng)度的碼可得到不同的碼率。為了降低譯碼復(fù)雜度,Turbo乘積碼通常由擴(kuò)展?jié)h明碼、奇偶校驗(yàn)碼或它們的組合構(gòu)成。

一般而言,如果考慮兩個(gè)系統(tǒng)線性分組碼c1= (n1,k1,d1),c2=(n2,k2,d2)如圖1所示,這里ni,ki,di(i= 1 ,2)分別表示碼長(zhǎng),信息比特?cái)?shù)和最小漢明距離。二維TPC編碼c=c1?c2可如下獲得:

1)把(k1×k2)信息比特放入一矩陣中;

2)使用行編碼器c1對(duì)k2行進(jìn)行編碼,產(chǎn)生行校驗(yàn)位,得到k2行、n1列的矩陣;

3)使用列編碼器c2對(duì)n1列進(jìn)行編碼,產(chǎn)生列校驗(yàn)位,得到n2行、n1列的矩陣。

以上步驟2)和3)不能同時(shí)進(jìn)行,因此這樣的編碼過(guò)程屬串行級(jí)聯(lián)方式。這樣得到二維Turbo乘積碼的參數(shù)為:n=n1×n2,k=k1×k2,d=d1×d2。碼率為R=R1×R2,這里Ri是碼ci的碼率,Ri=ki/ni。為了降低編碼器和譯碼器的復(fù)雜度,通常令c1=c2。

2.2 Turbo乘積碼編碼器結(jié)構(gòu)

圖2所示是Turbo碼編碼器的結(jié)構(gòu),Turbo碼編碼器通過(guò)交織器把兩個(gè)遞歸系統(tǒng)卷積碼并行級(jí)聯(lián),這兩個(gè)分量碼編碼器結(jié)構(gòu)相同,編碼器的輸出端包括信息位和兩個(gè)校驗(yàn)位,首先把輸入碼流kD劃分為長(zhǎng)度為N的數(shù)據(jù)信息塊,送給每個(gè)編碼器。第一個(gè)編碼器產(chǎn)生N比特的校驗(yàn)碼流1kY;第二個(gè)編碼器也處理同樣的信息數(shù)據(jù),但要經(jīng)過(guò)一個(gè)具有固定交織方式的交織器的擾序,也生成N比特的校驗(yàn)碼流2kY。Turbo編碼器把原始信息數(shù)據(jù)碼流kD和校驗(yàn)碼流Y1k、Y2k一起傳送,經(jīng)過(guò)復(fù)用器調(diào)制后,生成了Turbo碼序列X。為了提高碼率,校驗(yàn)碼流Y1k、Y2k需要經(jīng)過(guò)刪余器,采用刪余技術(shù)從這兩個(gè)校驗(yàn)序列中周期地刪除一些校驗(yàn)位,形成校驗(yàn)位序列X。

3.Turbo乘積碼編碼的FPGA設(shè)計(jì)與實(shí)現(xiàn)

為了實(shí)現(xiàn)實(shí)時(shí)編碼,根據(jù)編碼數(shù)據(jù)流向?yàn)閱蜗蛐缘奶攸c(diǎn),本設(shè)計(jì)采用流水線結(jié)構(gòu)。整個(gè)編碼器分成三部分,第一部分為輸入數(shù)據(jù)緩存,第二部分為編碼,第三部分為輸出數(shù)據(jù)緩存。這種設(shè)計(jì)結(jié)構(gòu)可以使數(shù)據(jù)接收、數(shù)據(jù)編碼和數(shù)據(jù)輸出三部分流水進(jìn)行,從而大大提高了編碼速率。按照上述的設(shè)計(jì)結(jié)構(gòu),對(duì)TPC編碼器的FPGA設(shè)計(jì)實(shí)現(xiàn)進(jìn)行模塊的劃分。原理框圖如圖3所示。

3.1 編碼模塊的設(shè)計(jì)

行編碼模塊和列編碼模塊基本相同,因此放在一起介紹。行/列編碼模塊又劃分為三個(gè)子模塊來(lái)完成編碼功能,其子模塊框圖如圖4所示。

從FIFO或者RAM中把要進(jìn)行編碼的串行數(shù)據(jù)讀出,轉(zhuǎn)換成57bits的并行數(shù)據(jù),擴(kuò)展?jié)h明碼編碼模塊對(duì)輸入的57比特?cái)?shù)據(jù)進(jìn)行擴(kuò)張漢明碼編碼,加上校驗(yàn)位后為64比特。然后再經(jīng)過(guò)并串轉(zhuǎn)換為串行數(shù)據(jù)存入緩存中,為下一步編碼或編碼輸出做好準(zhǔn)備。

其中,串并/并串轉(zhuǎn)換可以通過(guò)移位寄存器來(lái)實(shí)現(xiàn),按照相應(yīng)的時(shí)鐘節(jié)拍,每輸入一位數(shù)據(jù)進(jìn)行相應(yīng)的移位。串并轉(zhuǎn)換實(shí)現(xiàn)的Verilog代碼為:

并串轉(zhuǎn)換實(shí)現(xiàn)的Verilog代碼為:

擴(kuò)展?jié)h明碼編碼模塊把并串轉(zhuǎn)換后57位寬的并行數(shù)據(jù),按照擴(kuò)展?jié)h明碼的編碼規(guī)則,在高位添加7個(gè)校驗(yàn)比特,輸出數(shù)據(jù)位64位寬的并行數(shù)據(jù),每一組數(shù)據(jù)代表一個(gè)擴(kuò)展?jié)h明碼組。按照擴(kuò)展?jié)h明碼的編碼規(guī)則,其核心部分的Verilog代碼如下所示:

其中,data_out[63]為所有前63位的奇偶校驗(yàn),data_out[62:57]為漢明碼校驗(yàn),data_out[56:0]為原始數(shù)據(jù)。

3.2 交織RAM模塊的設(shè)計(jì)

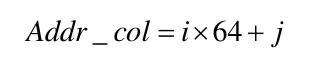

在編碼過(guò)程中要先進(jìn)行行編碼再進(jìn)行列編碼,中間必須進(jìn)過(guò)行列的交織。本項(xiàng)目中行列交織采用雙端口RAM實(shí)現(xiàn),行列交織時(shí)存在RAM地址的跳變,在設(shè)計(jì)時(shí)采用兩個(gè)計(jì)數(shù)器實(shí)現(xiàn),設(shè)兩個(gè)計(jì)數(shù)器分別為i[5:0]、j[5:0],則可按照以下公式計(jì)算跳變的列地址:

不難發(fā)現(xiàn),64=26,由于其特殊性,公式的乘法實(shí)現(xiàn)也相對(duì)比較簡(jiǎn)單,用Verilog語(yǔ)言可以描述為:

使用這樣的方法就很好地解決了編碼過(guò)程中的行列交織問(wèn)題,亦即先進(jìn)行行編碼再進(jìn)行列編碼的問(wèn)題。

4.結(jié)束語(yǔ)

本文采用可編程邏輯器件FPGA實(shí)現(xiàn)了一種先進(jìn)的前向糾錯(cuò)編碼Turbo乘積碼的編碼,使用Verilog硬件描述語(yǔ)言完成了編碼器的設(shè)計(jì)工作,在Xilinx FPGA芯片上完成了編碼器的硬件驗(yàn)證,從實(shí)驗(yàn)結(jié)果可看出設(shè)計(jì)的編碼器滿足預(yù)期指標(biāo)要求。

[1]劉東華編著.Turbo碼原理與應(yīng)用技術(shù)[M].北京:電子工業(yè)出版社,2004,1.

[2]王新梅,肖國(guó)鎮(zhèn)編著.糾錯(cuò)碼——原理與方法(修訂版)[M].西安:西安電子科技大學(xué)出版社,2001,4.

[3]田耘,徐文波,張延偉等編著.無(wú)線通信FPGA設(shè)計(jì)[M].北京:電子工業(yè)出版社,2008,2

[4]夏宇聞編著.Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程(第2版)[M].北京:北京航空航天大學(xué)出版社,2008,6

史亞維(1982—),女,陜西咸陽(yáng)人,碩士研究生,助教,現(xiàn)供職于咸陽(yáng)職業(yè)技術(shù)學(xué)院,主要研究方向:FPGA和數(shù)字電路設(shè)計(jì)。