64QAM調制的DSP實現*

李校林,劉文文

(重慶郵電大學 重慶市移動通信技術重點實驗室,重慶 400065)

正交振幅調制(QAM)是頻譜利用率很高的一種調制方式,相比于其他調制方式,具有更高的數據傳輸速率,在未來通信面臨的頻譜危機中有著很強的競爭力。為了適應不斷變化的無線信道,LTE采用了多種調制方式[1],根據無線信道質量動態地改變調制方式,使其傳輸性能最優。LTE最高支持64QAM的調制方式,大大提高了數據的傳輸效率。

64QAM將6個硬比特調制成一個復值符號,實部和虛部各由3 bit以相同的方式調制。本文按照64QAM的原理,設計了一種基于DSP的高效實現方法:將64QAM的8種調制后的量化幅度以表格形式存儲,采用查表方式調制;采用大端模式,外循環一次取96 bit;設計了高效的除法實現程序,用來計算外循環的次數。

1 64QAM的實現原理

在64QAM調制方式中,信號的振幅和相位作為兩個獨立的參量同時受到調制,這種信號的一個碼元可以表示為[2]:sk(t)=Akcos(ω0t+θk),式中 k 為整數,Ak和θk可以取多個離散值。展開為:sk(t)=Ikcosω0t+Qksinω0t。其中,Ik=Akcosθk,Qk=Aksinθk,Ik和 Qk相互獨立,所以64QAM是用兩個獨立的基帶信號,對兩個相互正交的同頻載波進行抑制載波的雙邊帶調制。

兩路信號經 2~8 V電平轉換后可得:±1 V、±3 V、±5 V、±7 V共8個電平。調制器 I輸出的 8個信號有:±cosω0t、±3cosω0t、±5cosω0t、±7cosω0t, 調制器 Q 輸出的 8 個信號有:±sinω0t、±3sinω0t、±5sinω0t、±7sinω0t, 兩路信號組 合共有64種不同的編碼值。根據星座圖,將8種幅度值制成表格[3]如表1所示。

根據64QAM形成的正交調幅法,先把待調制的比特流串并轉換成I路和Q路比特流,串并的方法是:偶數位置的比特提取出來放在I路,奇數位置的比特放在Q路 (這里假設第一個比特的位置序號是0),根據表1編碼,然后I路和Q路數據組合成復值符號。

本文選用TMS320C64系列作為開發使用的DSP芯片,該芯片屬于高速定點DSP,所以將浮點數進行定點量化后轉化為表2存儲,然后每次按照3個比特值計算偏移地址,進行相應64QAM的查表編碼。

表1 64QAM調制表格

表2 64QAM定點量化表格

2 DSP處理器[4]

TI公司生產的TMS320C6455芯片屬于C64x系列,是C6000系列中性能最高的定點數字信號處理器,主要特點是在體系結構上采用了甚長指令集VLIW(Very Long Instruction Word)結構。C64x系列CPU采用哈佛結構,其程序總線與數據總線分開,取指令和執行指令可以并行運行。程序總線為256 bit,每一次取指令操作都是取8條指令,可以實現高速運算。另外片內集成大容量SRAM,最大可達到8 Mbit。16/32/64 bit的高性能外部存儲器接口(EMIF)提供了與 SDRAM、SBSRAM和 SRAM等同步/異步存儲器的直接接口。

3 設計與實現

3.1 變量和內存區設計

本方案對變量的定義、內存的分配及其他說明如表3所示。

表3 變量定義及說明

以LTE-TDD為例,根據一個子幀的大小設計每個變量占用內存的大小。頻譜資源不超過110RB,每個RB有12個RE,一個子幀包含2個時隙,每個時隙有7個OFDM符號。其中每個比特占用一位,每個復值符號占用一個字的大小。內存設計如下:

_Data_input.uset"d_dest",13860

_Data_len.uset"d_dest",4

_Mod_out.uset"d_dest",73920

_Mod_out_len.uset"d_dest",4

3.2 詳細設計

64QAM調制是將6 bit調制成一個復值符號。而TMS320C6455寄存器只有32 bit,所以每次的取值不能在一個循環里面完成,此時采用大端模式,16次內循環為一次大循環,每次內循環處理6個bit。一次外循環處理的 bit數為 96,B0為外循環數,調用除法程序,由 bit流長度B4除以96得到。內循環分成四個部分,內循環次數B1初始值為16:

第一次:取 32 bit,B1取值為16~12,并且將最后 2 bit存入 A23;

第二次:取32 bit,后 4 bit存入A23,上次余下的 2 bit補充到 bit前,B1的取值為 11~7;

第三次:取 32 bit,后 6 bit存入 A23,用于第 4次處理,上次余下的4 bit進行填補,B1取值為6~2;

第四次:處理最后的 6 bit,B1取值為1。

在上面的4次取數據的處理中都要將拼接后的30 bit(第四次是6 bit)進行奇偶比特抽取,將奇數位置比特和偶數位置比特分別放在一個寄存器,每次內循環取前3 bit查表,分別獲得實部和虛部的值,然后拼接成一個復值符號存儲,并且將取過的3 bit移出。

外循環結束后,對于余下bit的處理。每進行一次處理,B16就減少 6,直到 B16為 0,即處理完剩余 bit數。剩余bit和上面循環一樣需要有一個計算內循環次數的計數器,初始值為16,如圖1所示。

設計的流程圖如圖2所示。

3.3 除法模塊設計

由于DSP不提供單周期的除法運算,所以必須調用外部寫除法的子函數。本文設計了一種除法算法,便于DSP實現,原理如下:

設 a是被除數,b是除數,且 a÷b=c…d,則 a-bc=d,a減去 b的 c倍,余數為 d。

由于數據在 DSP中是2進制,a和b可以寫成下面形式:

圖2 64QAM DSP實現設計流程圖

(1)若 a-b<0,則 c=0,d=a。

(2)若 a-b>0,則調用指令 LMBD分別計算 a和 b的最高有效位的位置,計算m-n,令t=m-n,將b左移t位。

若 a-2′b>0,則 c 的第 t位置 1,然后 a=a-2′b;

若 a-2′b<0,t--,則將 c 的第 t位置 1,然后 a=a-2′b。重復步驟(2),直到t<0,可以得到商c,余數d就是最后的差。

調用的主要指令有 SHL、SHR、SUB,這種算法不但解決了DSP定點除法難以實現的問題,而且耗費時間也比較少,在不用并行流水線的情況下大約要150 cycle,使用并行流水更能節省時間。

3.4 星座圖映射

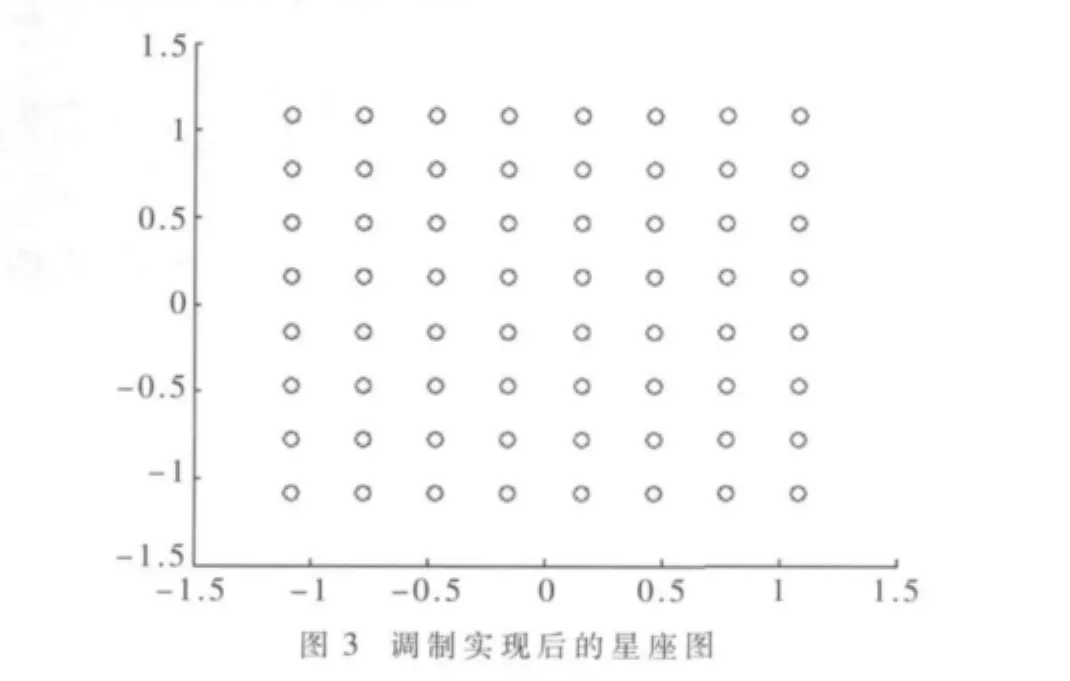

為了驗證該實現的正確性,把調制后的數據從CCS中導出,截取3 600個復制符號,導入MATLAB進行星座圖映射,結果如圖3所示。

4個象限共64個星座點,分布均勻,幅值、相位都正確。

64QAM是載波和相位同時調制的復合調制方式,提高了頻譜利用率,節約帶寬,在未來通信領域具有一定的發展前途。本文設計的DSP實現方案,利用查表方式,實現復雜度更低,更加靈活。其中大端模式的取比特的設計方法以及結合相關匯編指令設計的除法模塊,大大縮減了程序運行的周期,最后的星座圖映射證明64QAM的DSP實現的最終結果是正確的,可以應用于工程。

[1]曾召華.LTE基礎原理與關鍵技術[M].西安:西安電子科技大學出版社,2010.

[2]曹志剛,錢亞生.現代通信原理[M].北京:清華大學出版社,1992.

[3]3GPP.TS 36.211 v9.0.0 Evolved universal terrestrial Radio access(E-UTRA)Physical Channels and Modulation(release 9)[S].s.l.:3GPP,2009.

[4]TMS320C64x/C64x+DSP CPU and Instruction set reference guide[S].Texas Instruments Corporation.2008.