基于CPLD的LVDS數據傳輸系統的設計與研究

郭鵬翔, 祖靜, 尤文斌

(中北大學儀器科學與動態測試教育部重點實驗室,太原,030051)

0 引言

隨著信息化的高速發展,工程人員面臨著大數據量的高速傳輸問題。采用低電壓差分信號LVDS技術的設備電路系統可使傳輸速度每秒高達數百Mb,可以很好地解決這一瓶頸問題[1-2]。另外本設計中還引入了FIFO芯片作為緩沖給LVDS發送端,從而確保數據的高速傳輸不會中斷。同時應用CPLD對FIFO以及LVDS器件進行時序精確,邏輯準確的操作,以達到設計要求。最后應用Modelsim軟件對設計系統進行了時序仿真以驗證其達到了所需要求。

1 系統工作流程

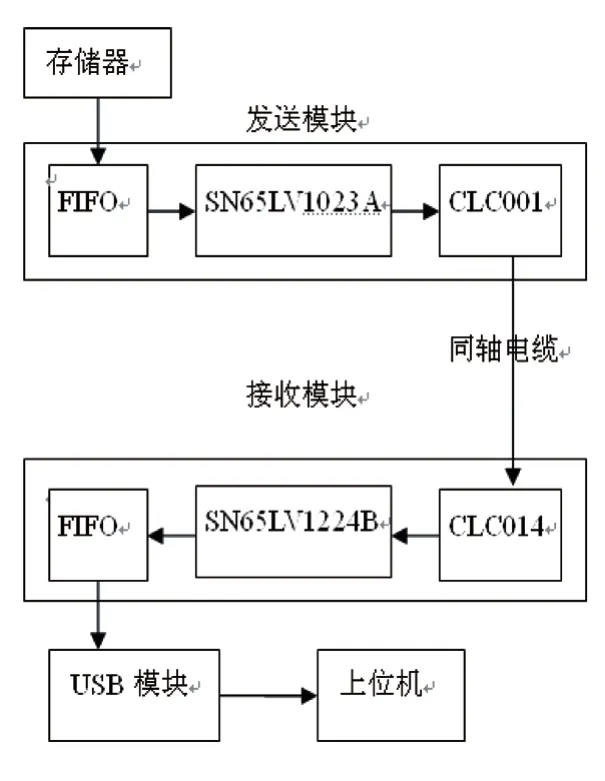

系統設計框圖如圖1所示。以模塊化設計,主要分為LVDS發送模塊,LVDS接收模塊,USB模塊。系統從存儲器中讀取的數據通過LVDS總線高速傳輸給USB模塊,可以在上位機進行存儲與實時顯示。

2 系統原理

本系統的LVDS器件選用美國國家半導體公司推出的10位總線型低壓差分信號芯片組SN65LV1023A、SN65LV1224B。其中SN65LV1023A是可將10位并行CMOS或TTL數據轉換為具有內嵌時鐘的高速串行差分數據流的串化器[3];而SN65LV1224B則是接收該差分數據流并將它們轉換為并行數據的解串器,它同時又可以重建并行時鐘[4-5]。采用該器件組進行數據串化時采用的是內嵌時鐘,這樣可有效地解決由于時鐘與數據的不嚴格同步而制約高速傳輸的瓶頸問題。

圖1 系統組成框圖

上電后,兩芯片分別置所有輸出管腳為三態,而后啟動鎖相環跟蹤并鎖定本地時鐘(對于串化器為TCLK,對于解串器為REFCLK)。當解串器檢測到LVDS輸入端的邊緣跳變后,它試圖鎖定到內部嵌入時鐘[6]。當解串器內部鎖相環鎖定到輸入的數據時,解串器LOCK輸出端為高;當解串器鎖定到LVDS數據時,LOCK輸出端變低。所以只有當LOCK為低時,此時解串器的輸出才是為輸入端的LVDS數據。在數據傳輸過程中一旦解串器中的鎖相環失鎖,LOCK位將變高。這時解串器鎖相環會在較短時間內自動再次鎖定到內部嵌入時鐘以達到再次同步[7]。

在實際情況下,如果出現失鎖,串化器會繼續發送數據,解串器會在很短時間內(小于500μs)重新完成同步[8],但是在這個時間內解串器輸出的數據并不是輸入端的LVDS數據。即輸入端的LVDS數據會有部分遺漏由于失鎖。對于大容量數據的高速傳輸,這部分遺漏的數據對接收端數據的完整性會有較大的影響。為此,本設計在CPLD內部設置了一選通功能,使得系統在失鎖的這段時間內,CPLD會內部發假數據給串化器輸入端,直至系統再次同步。并且在發假數據的同時,會發送標志位R8=0,從而在接受模塊接收數據時,可以根據R8的數值來甄別真假數據。

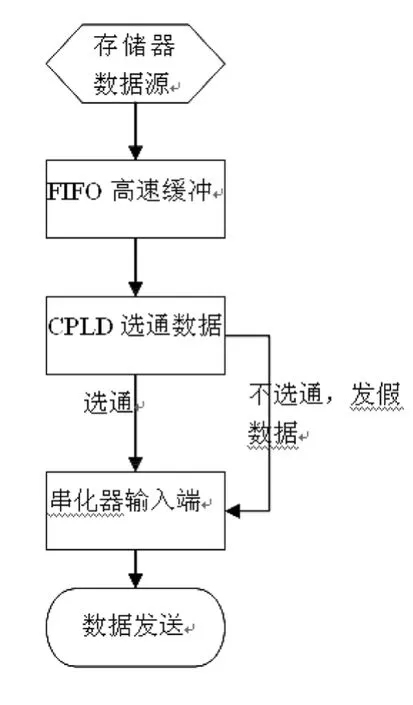

以發送模塊為例,它的工作流程如圖2所示。

圖2 發送模塊組成框圖

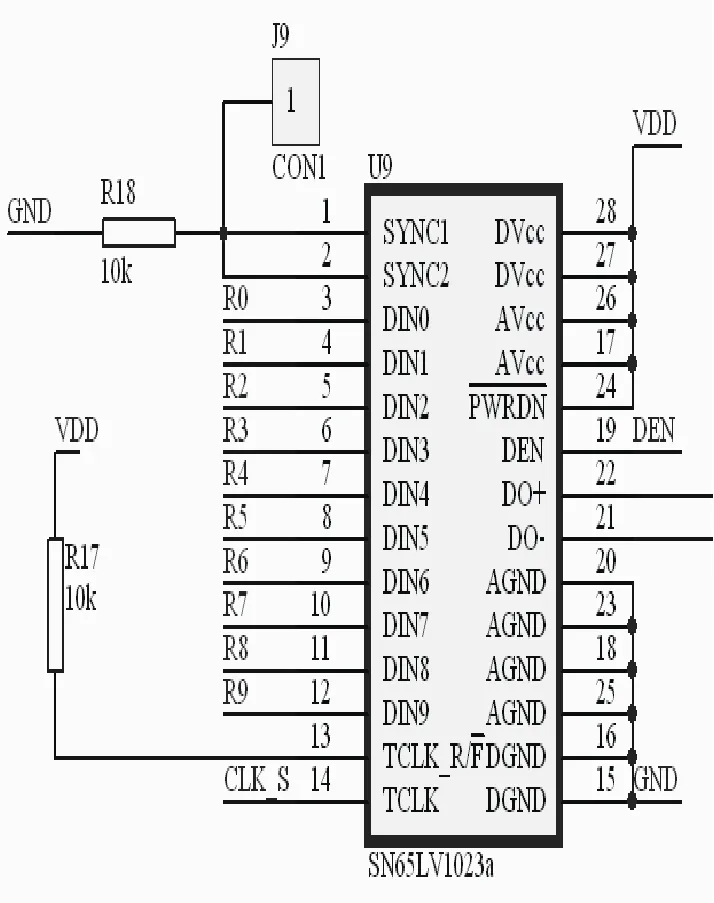

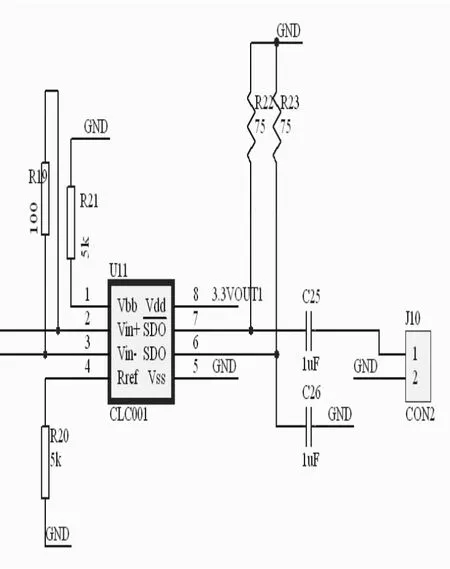

本設計中發送模塊采用的串化器SN65LV1023A的具體電路連接圖如圖3所示。高速驅動器CLC001的電路連接如圖4所示。在發送模塊中,由于是高速數據傳輸且在傳輸過程中可能會出現短時間(小于500μs)的失鎖,所以本方案中特地引入了FIFO芯片IDT72V241,從存儲器讀取的數據先寫入FIFO,在確認系統同步的情況下,再將FIFO中數據讀出賦給串化器。從而確保數據的有效性,且保證了數據高速傳輸的不間斷性。可見,在發送模塊中,通過CPLD控制FIFO芯片的讀寫操作是實現LVDS高速傳輸且不丟失有效數據的關鍵。

圖3 串化器SN65LV1023A連接圖

圖4 高速驅動器CLC001電路連接圖

3 CPLD程序設計

FIFO芯片IDT72V241的容量為4096x9 bit。CPLD采用XILINX公司的XCR3128,其內部程序采用模塊化設計。分為復位,寫FIFO,讀FIFO 3個模塊。

3.1 復位模塊

與許多芯片類似,FIFO芯片在正常工作之前,也需要進行復位操作。本設計中CPLD在檢測到EN信號變高后,會先賦給FIFO復位管腳RS端一個低脈沖(不小于120ns),使得FIFO芯片復位,以準備好下一步的工作。

3.2 寫FIFO模塊

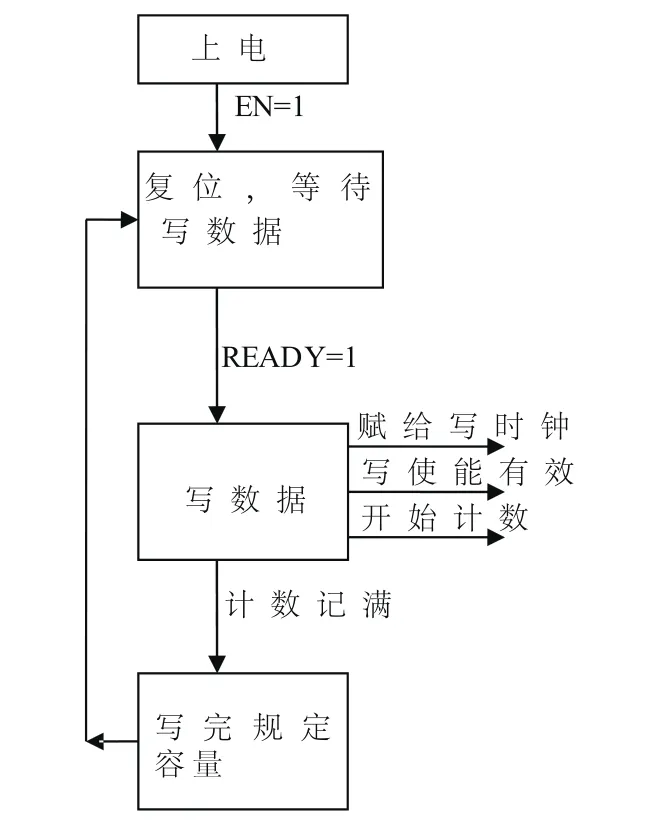

在本設計中,大容量的數據在進入LVDS系統傳輸前先經過FIFO芯片進行數據緩沖。用CPLD控制數據寫入FIFO的過程可以用狀態圖來表示,如圖5所示。

圖5 寫FIFO流程

3.3 讀FIFO模塊

FIFO中的數據都是有效數據,在被讀出后通過CPLD賦給串化器的輸入端,從而通過LVDS的數據形式發送出去。如前面所述,在這個傳輸過程中,可能會出現短時間(小于500μs)的失鎖,這是為了防止FIFO內有效數據的丟失,應停止讀取FIFO中的數據,并通過CPLD賦值假數據給串化器直到再次同步完成。

4 仿真結果

根據CPLD內部各模塊的設計思想,在XILINX ISE9.1環境下編輯程序,并在MODELSIM軟件中通過時序仿真來驗證構想的正確性。通過各仿真時序圖來看,程序很好地完成了設計要求。

各模塊仿真結果如下。

4.1 復位模塊仿真

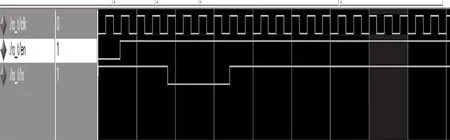

時序仿真如圖6所示。

圖6 復位模塊仿真圖

4.2 寫FIFO模塊仿真

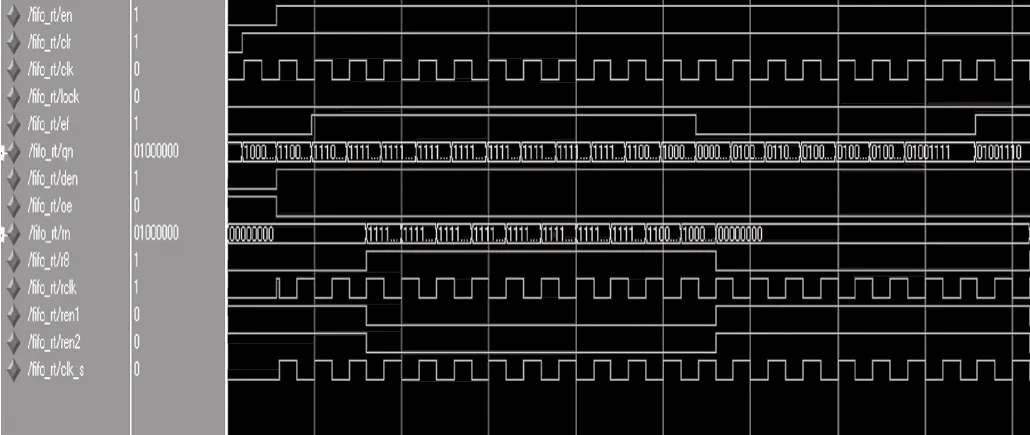

該模塊時序仿真如圖7所示。圖中wclk_f信號為FIFO的寫時鐘信號。WEN1為FIFO的寫使能信號,低有效。

圖7 寫FIFO模塊仿真圖

4.3 讀FIFO模塊仿真

該模塊時序仿真如圖8所示。

圖8 讀FIFO模塊仿真圖

5 結束語

本文設計的基于CPLD的LVDS總線高速數據傳輸系統,充分考慮了實際情況中可能出現的失鎖現象,做到高速數據傳輸的同時且不丟失有效數據。有著非常好的應用前景。

[1]陳一新.基于USB+LVDS的FPGA遠程測試系統[J].電子測試,2009(4):73-75.

[2]劉祥遠,陳書明.LVDS 高速 I/O 接口單元的設計研究[J].計算機工程與科學, 2001,23(4):54-58,62.

[3]來衛國.基于無線激光通信的數字視頻接收機的研究[J].國外電子元器件,2002(2).

[4]倪春波,應建華,劉三清,等.LVDS高速I/O接口電路設計[J].華中科技大學學報:自然科學版,2003,31(10):16-18.

[5]薛隆全,文豐,張時華.基于LVDS總線的高速長距數據傳輸的設計[J].電子設計工程,2009(2).

[6]楊建義.基于Visual Basic與RS232串行通信的溫度監測系統[J].電子測試,2007(12):47-50.

[7]National Semiconductor .LVDS Owners' Manual[R].National Semiconductor , Spring 1997.

[8]彭鄉琳.LVDS在長距離信號傳輸中的應用[J].兵工自動化,2006(7).