線陣CMOS圖像采集及編碼傳輸的實現*

江志東,高太長*,孫海洋,翟東力

(1.解放軍理工大學氣象學院,南京211101;2.南京眾華通電子有限公司,南京211101)

線陣圖像傳感器在圖像掃描、非接觸式尺寸檢測、位移測定和條形碼讀出等光電探測和光電成像領域有著廣泛的應用[1-2]。CCD圖像傳感器具有靈敏度高、頻率響應高和自掃描速度快等優點,最早應用于上述領域,但CCD圖像傳感器也有一些無法克服的缺點,如功耗高、制造工藝復雜難于單片集成,且由于CCD是高電容器件讀出速度慢。CMOS圖像傳感器以其功耗低、讀出速度快、易于單片集成日益受到重視[3]。隨著超大規模集成電路工藝技術的飛速發展,CMOS傳感器性能不斷完善,感光陣列不斷增多,在工業自動化、民用視頻、軍事偵察、空問遙感成像等領域得到廣泛應用[4]。隨著線陣圖像傳感器感光陣列的不斷增加,在高速圖像采集處理系統中,對系統存儲和數據實時處理也提出了更高的要求,需要解決圖像傳感器時序驅動、數據的緩沖、存儲和傳輸等一系列問題。

在氣象領域,基于CCD/CMOS傳感器陣列的成像技術獲取大氣粒子或者其他現象的二維或三維圖像,利用圖像處理理論確定大氣懸浮顆粒物[5]、云滴、雨滴[6]等粒子的濃度、尺度和速度分布信息,實現非接觸粒子檢測。在氣象業務中,儀器通常需要長期連續觀測且能夠實時進行數據處理,因此需要重點考慮數據的存儲、傳輸和實時處理等需求。

傳統的線陣數據高速采集系統通常數字處理器(DSP或FPGA)、高速FIFO、比較器模塊和傳輸接口芯片等組成,對于線陣CCD還需專門的驅動電路[7]。與通用DSP芯片相比,FPGA增加了設計的靈活性和適應性,縮短了產品上市時間[8]。本文介紹了基于FPGA和USB芯片CY7C68013實現的高速線陣CMOS圖像數據采集系統,解決了傳統采集方法中系統過于龐大和復雜的問題。針對高速采集數據的緩存、傳輸、實時處理及存儲等需求,設計完成了線陣CMOS的驅動時序,利用FPGA內FIFO核實現了原始像素數據的緩存和抽幀輸出,同時充分利用FPGA可編程特性,在FPGA內部實現了自適應閾值的比較模塊,在保留所需圖像信息的前提下,利用FPGA對比較后的二進制數據流數據進行壓縮編碼,降低了數據量,減少了對數據傳輸的要求,減輕了上位機實時數據存儲和實時處理的壓力。

1 系統總體設計與實現

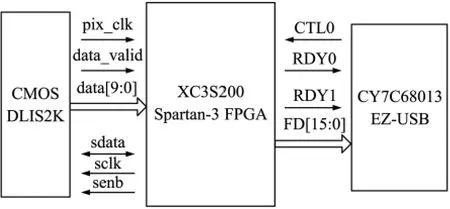

FPGA采用Xilinx公司Spartan-3系列XC3S200,主要完成傳感器的時序驅動、數據的采集緩存、比較編碼及傳輸邏輯控制等功能,該芯片容量為20萬門,片上有分布式RAM 30 kbit和塊RAM 216 kbit可用于構建FIFO和雙口RAM;圖像傳感器采用Panavision Imaging公司的DLIS-2K CMOS圖像傳感器,該芯片包含4行2 096個像素單元的線陣,每一行中有效像元個數2 080個,16個像元單元供暗電流檢測用,10位并行數字信號輸出,最大數據率為120 MHz。為便于數據緩存和傳輸,結合系統需求實際數據輸出取有效像素單元中的2 046個像素單元,每個像素單元數據用2個字節表示,結合幀數據頭每幀采樣數據量為4 kbyte(KB)。數據由USB芯片CY7C68013采用GPIF工作模式將數據上傳至上位機。USB工作采用 GPIF方式,利用CY7C68013的通用可編程接口GPIF模式實現與傳感器的無縫連接,可滿足圖像數據的實時傳輸[9]。

圖1 圖像采集系統硬件框圖

系統采用FPGA+USB的架構,該設計包括以下三個部分:線陣CMOS圖像傳感器、FPGA芯片和USB芯片CY7C68013。FPGA芯片為主控模塊,控制整個系統的工作時序和傳輸邏輯。根據需求系統可選擇工作在兩種模式下,即原始數據采集或編碼數據采集模式。在FPGA控制下,首先從CMOS傳感器的鎖存讀出圖像數據,進行數據位轉換,即將10 bit像素數據輸出補為16 bit,并加入一定格式的數據幀頭,然后將16 bit像素數據送至FIFO,再通過FPGA產生FIFO的讀寫控制邏輯和USB的接口傳輸邏輯,數據經USB芯片采用GPIF工作模式傳至計算機,至此可完成傳感器原始數據的傳輸。為減輕上位機存儲和實時數據處理的壓力,在保留所需圖像信息的基礎上,在FPGA中設計了數據比較編碼處理模塊,將原始像素數據和設定閾值進行比較,隨后將比較結果即二進制數據流編碼后的數據寫入FPGA的FIFO中,最后編碼數據仍由USB將數據上傳至上位機。

2 FPGA內數據采集、編碼功能的實現

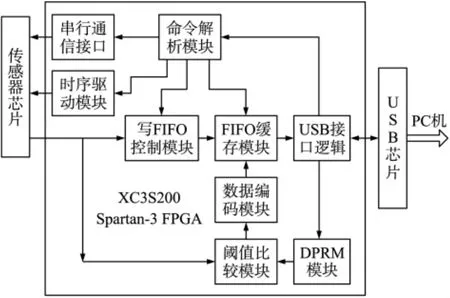

FPGA功能設計可分為接口模塊、緩沖存儲模塊、編碼處理模塊三部分。接口模塊負責前端傳感器時序驅動、FIFO讀寫控制和為USB提供傳輸接口邏輯;緩沖存儲器模塊作用有利用FIFO為不同時鐘域間數據傳輸提供緩沖,雙口RAM中可寫入經一定算法計算后的各點的像素閾值;編碼處理模塊根據設置的閾值,將實時采集的原始數據和每個像素單元的閾值進行比較,隨后將比較后的結果編碼輸出。FPGA內功能模塊設計如圖2。

本系統中,如何保證數據的完整性和準確性實現高速采集時大量數據的實時傳輸和處理是要考慮的重點。

圖2 FPGA內功能模塊設計

CMOS傳感器和USB芯片工作在不同時鐘域,如何在不同時鐘系統間實時準確傳輸數據是本系統的關鍵問題之一。常用的緩存有FIFO、SRAM及雙口RAM等,雙口RAM和SRAM存儲量大但需配以復雜的地址發生器,而FIFO數據順序進出,無需地址線,操作簡單。異步FIFO(First in First Out)可以解決不同時鐘域之間的數據傳輸問題,可以容納異步信號的頻率或者相位的差異[10],FIFO芯片廣泛常應用于圖像數據采集的緩沖[11]。因此如何設計一個高可靠性、高速異步FIFO存儲器及控制邏輯實現數據的緩存、傳輸時難點之一。

本系統中傳感器數據采樣幀頻需在10 kHz以上,而當傳感器的幀頻為10 kHz時,實時原始像素數據量即可達到40 MB/s(Mbyte/s)。在普通計算機中,硬盤的持續傳輸速率最高可達50MB/s,但在Windows操作系統下,應用程序很難達到這一速率。如何保留相關必要圖像信息,減少數據傳輸量,實現數據的實時處理是本系統的難點之二。

下面著重對系統的數據緩沖模塊和編碼處理模塊的實現及工作原理分別介紹。

2.1 數據緩沖模塊

利用FPGA片內異步FIFO作高速緩存,操作簡單,所用的FIFO IP核經過充分測試和優化,運行穩定、可靠。實際應用時只需根據FIFO產生的邏輯標志設計讀寫邏輯即可,而不需考慮FIFO設計中邏輯標志的產生和異步電路的亞穩態等問題[12]。

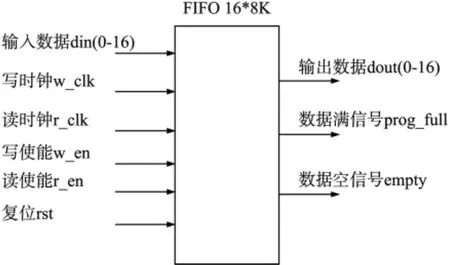

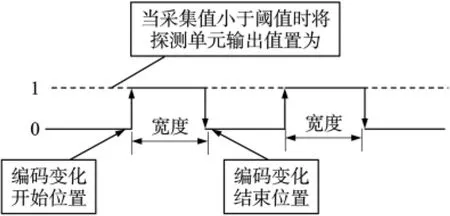

在ISE開發工具中創建FIFO_Core,選擇異步時鐘和使用內部塊RAM,設置其輸入輸出數據位寬為16,FIFO深度為8 096,設置可編程滿信號計數為4 095,當FIFO寫計數達到4 095時(注意此對應第4 096個數據),即達到一幀數據時觸發可編程滿prog_full信號,FIFO的功能示意圖如圖3。在FIFO的例化調用時,寫時鐘為傳感器數據輸出同步時鐘,讀時鐘為USB的GPIF模式的IFCLK。

圖3 FIFO結構圖

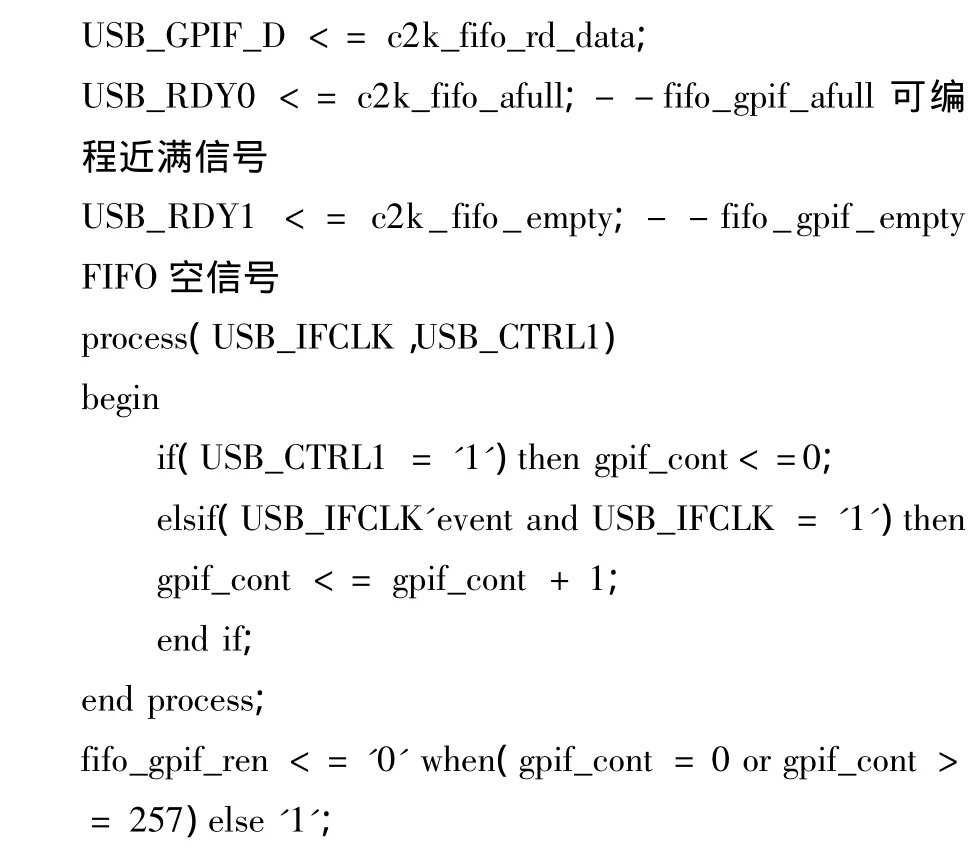

數據緩沖模塊的設計實際上是FIFO的讀寫邏輯的設計,即寫使能和讀使能的控制。FIFO采取單行復位的方式,檢測到有效數據標志上升沿后,啟動像素計數,當像素計數值為29時,FIFO復位,像素計數值在30到2 077之間時,FIFO寫使能有效。其中像素計數值為30和31時,寫入FIFO數據幀頭0×9 999,其后對應CMOS輸出有效的2 046個像素數據。原始像素數據實時采集時,當FIFO寫計數達到4 095時候,觸發可編程滿prog_full信號,由prog_full做為控制FIFO異步讀數據的狀態信號之一,當prog_full有效時,FIFO寫使能禁止。FIFO讀使能由prog_full觸發,由USB固件程序根據其端點FIFO狀態及FPGA內部FIFO的狀態信號控制。USB工作與GPIF模式,設置為Auto-In(自動打包)模式,每次傳輸數據量為512 B(byte),對應256個像素單元數據,滿足條件時無需外部控制器的干預可直接自動將FIFO中數據傳輸到上位機,完成CMOS數據的實時傳輸。下面給出了FPGA中和USB連接的部分邏輯代碼:

2.2 數據編碼壓縮模塊

為了減少數據傳輸量,減輕上位機數據存儲和處理壓力,結合系統自身功用,設計了數據編碼壓縮單元對原始像素數據進行處理。數據編碼壓縮單元包括閾值比較模塊、雙口RAM,數據編碼模塊三個部分。雙口RAM直接在ISE調用Core Generator生成,其參數為2 k·16 bit,其中A口設置為寫狀態,通過上位機可控制寫入經一定算法計算的每個像素點各自的閾值,B口為讀狀態,比較模塊讀入閾值和對應的像素數據比較。

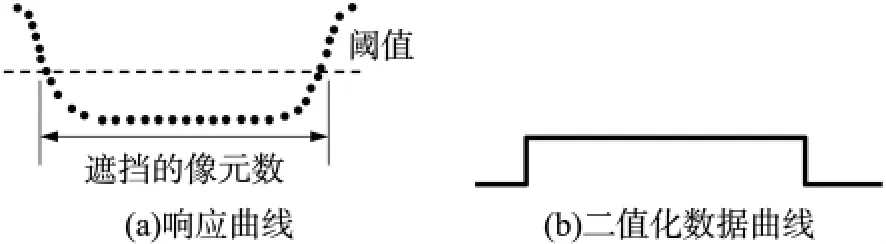

數據編碼壓縮前首先需將傳感器像素的響應曲線二值化,根據設置的閾值(此外設置為固定值,實際測量時可對每個像素點設置各自閾值),當相應像素光強響應值低于預先設置的閾值強度時,則認為該像素被完全遮擋,置為1,如圖4。數據編碼示意圖如圖5,當檢測到幀數據有效標志datavalid上升沿信號時,啟動讀像素計數,讀像素計數范圍為[30,2 077]時,觸發比較使能,在讀像素計數的觸發下,雙口RAM地址遞增,像素數據值和其對應閾值進行比較(實際應用時可根據相關算法寫入對應點閾值,示意圖中采用固定閾值),當所采集的像素數據值低于設置的閾值時則比較結果為1,否則為0。數據編碼模塊是根據比較結果數據流,即二進制序列,在檢測到比較結果的上升沿時記錄當前像素數據的位置同時觸發編碼計數,在比較結果下降沿記錄當前編碼計數,從而確定對應的編碼寬度。將比較結果數據流編碼輸出,輸出起始位置和編碼的寬度,這樣即保留了原始數據的信息,又可以減少數據量,確保數據的實時傳輸和處理。

圖4 原始數據二值化示意圖

圖5 編碼示意圖

3 仿真及試驗結果

為檢驗模塊的功能,利用Modelsim編寫測試向量對相關設計進行了仿真,同時將程序編譯后下載至數據采集板觀測結果。

3.1 FIFO邏輯的仿真及試驗

向FIFO寫數據必須滿足兩個條件:①數據總線有數據且數據有效,②FIFO寫使能有效。由于傳感器行有效標志data_valid有效時一直有數據輸出,而實際上我們只使用其中的2 046個數據(前兩個數據為數據幀頭),因此不能將data_valid直接做為FIFO的寫使能有效信號,FIFO寫使能標志由data_valid和FIFO的可編碼滿標志prog_ful共同確定。在檢測到行有效信號后觸發像素計數,當計數值為30和31時為數據幀頭數據,32~2 077為實際像素數據。時序仿真后波形如圖6(a)。將代碼下載至FPGA中運行發現上位機并不能實時完全處理及存儲每一幀數據,即存在丟幀情況。利用模擬數據測試傳輸模塊發現,正常情況下GPIF的傳輸數據率為20 Mbyte/s左右,此外上位機的實時處理也影響數據的傳輸。在實際應用中,原始像素數據的采集主要用于時域分析,即統計一定時間內各個像素單元響應光強的平均水平,為數據比較閾值的設置提供參考。因此沒有必要將每一幀原始像素數據記錄保存,寫FIFO控制采用抽幀的控制方式,即采用多級門控信號實現每幾幀數據輸出一幀,每一級門控信號由data_valid觸發,由多級門控信號同時觸發寫FIFO使能,如時序仿真波形圖6(b),采用每四幀輸出一幀,在此條件下可完整將輸出原始數據保存用于時域分析。經抽幀輸出控制,對應傳感器的數據采集幀頻為10 kHz時,原始數據的輸出量由40 Mbyte降至10 Mbyte,利用CYPRESS公司提供的USB驅動和固件程序框架無需優化即能夠實現數據的正常傳輸,上位機能夠將實時原始像素數據保存用于時域分析。

圖6 異步寫FIFO時序仿真圖

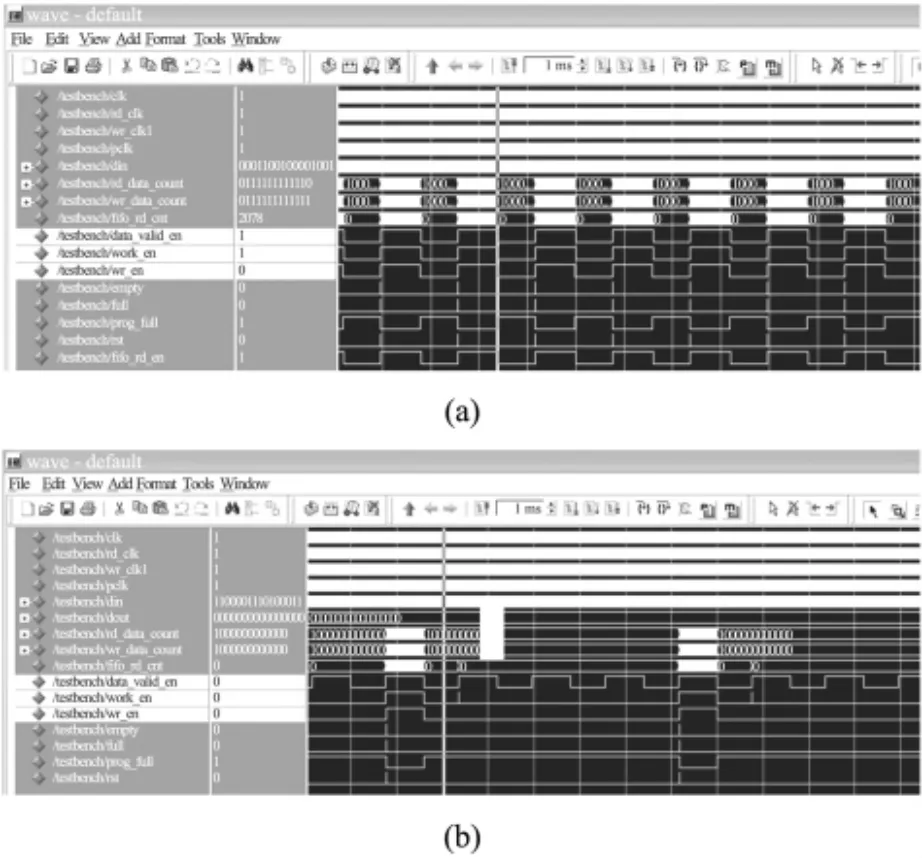

3.2 編碼功能的仿真及試驗

在測試向量中假設二值化起始位置為20和68,結束位置分別為52和244,則編碼結果應該為[20 32][68 176],仿真時序圖如圖 7。經編碼壓縮,對應傳感器的幀頻10 kHz時,系統的數據采集量由每秒40 Mbyte降至78 kbyte(每幀為數據頭加一組編碼數據時),傳輸系統能夠完全不丟幀降數據傳至上位機,上位機能夠實時存儲和解碼計算。

圖7 編碼功能時序仿真圖

4 初步試驗結果及小結

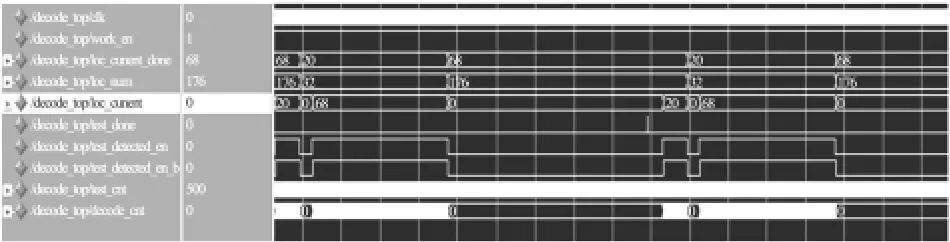

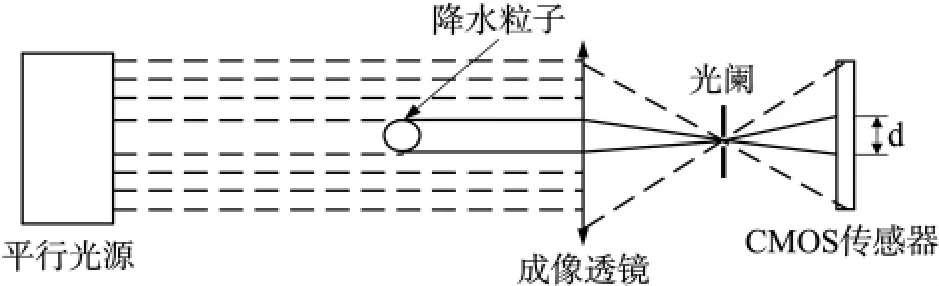

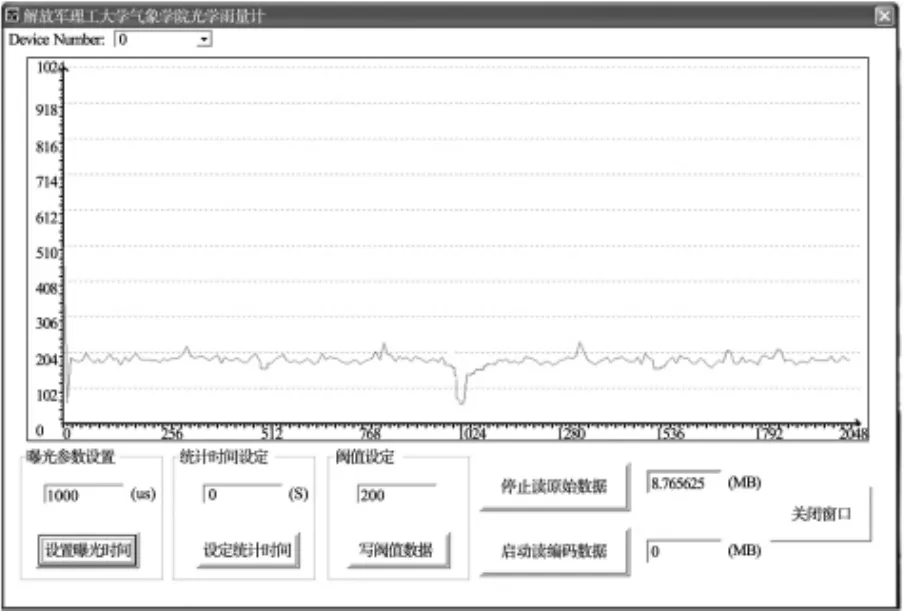

結合光學照明系統和成像系統,對數據采集板進行了初步調試。圖8為系統成像示意圖,當降水粒子遮擋光路時,在線陣傳感器上產生投影,引起光強響應的變化。光源采用激光平行光源,中心波長650 nm,功率30 mW。傳感器采樣速率為20 000幀/s,以0.2 mm的銅絲遮擋光路引起的光強響應變化如圖9。

圖8 系統工作原理示意圖

圖9 實際光強響應曲線

系統采用可編程邏輯器件FPGA和USB2.0接口技術實現了線陣CMOS的時序驅動、高速采集、閾值比較和傳輸,解決了以往采集系統中存在軟硬件過于復雜的問題,克服了大量數據傳輸和處理時對上位機處理帶來的壓力,充分利用了FPGA芯片的片內資源,結合自適應閾值統計方案,實現高速數據采集和比較編碼壓縮,達到了小型化、智能化和高性價比的有機結合。

初步試驗結果表明,系統滿足圖像數據實時采集和處理的要求,同時減輕了上位機數據存儲和處理的負擔。為實現不同尺度、不同下落末速度降水粒子的檢測,傳感器采樣速度應在15 000幀/s以上。DLIS-2K的最大數據輸出率為120 MHz,系統采樣典型的配置工作在60 MHz時,采樣速率約7 500幀/s,若設當修改傳感器參數配置、采用更高工作時鐘,可將CMOS數據采樣率提高到20 000幀/s以上。隨著FPGA的發展,利用帶有USB IP核的FPGA芯片可進一步實現系統的小型化。本系統可用于大氣粒子的非接觸測量,適當修改可應用到一維尺寸測量,邊緣檢測,位移測量等方面。系統初步實現了線陣圖像原始數據和編碼數據的采集,如何實現系統的業務化觀測,還需進一步確保系統野外運行時的穩定性及關注系統自檢和定標等功能的實現,此外對數據的后續處理及二次產品開發將另文探討。

[1]周根榮,姜平.基于線陣CCD的織物圖像采集系統[J].儀表技術與傳感器,2007,(8):51 -52.

[2]王玉田,楊妮,林曉琳.基于CCD技術的浮法玻璃厚度測量系統的研究[J].儀表技術與傳感器,2007(6):72-74.

[3]方杰.CMOS圖像傳感器[D].[碩士學位論文].上海:復旦大學,2004.

[4]曾桂英,潘金艷.基于FPGA的CMOS圖像傳感器采集系統設計[J].科學技術與工程,2010,10(03):692 -695.

[5]王丹青.基于分形理論的大氣懸浮顆粒物圖像識別[D].[碩士學位論文].武漢:武漢理工大學,2006.

[6]Baumgardner D,Greg Kok1,Dawson W,et al.A New Groundbased Precipitation Spectrometer:The Meteorological Particle Sensor(MPS)[C]//ams confex com,2002.

[7]虞益挺,饒伏波,喬大勇,等.一種新型CCD驅動電路設計方法[J].傳感技術學報,2005,18(2):388 -390.

[8]葉敏,周文暉,顧偉康.基于FPGA的實時圖像濾波及邊緣檢測方法[J].傳感技術學報,2007,20(3):623 -627.

[9]蘇建坡,馬海濤,唐玉國.基于USB2.0及GPIF的CMOS圖像傳感器視頻實時采集系統[J].儀表技術與傳感器,2006(9):35-37.

[10]張毅,周成英.高速同步FIFO存儲器在數字信號源中的應用[J].電子技術,2003,30(11):48 -50.

[11]汪曣,白玉潔,張艷超,等.基于CCD的膠體金試紙條光電檢測儀器設計及實驗研究[J].傳感技術學報,2008,21(8):1370-1373.

[12]楊軍,孔兵,宋克儉,等.基于FPGA的高速異步FIFO存儲器設計[J].云南大學學報,2007,29(6),560 -565.