基于FFT和閉環(huán)采樣控制的科氏質(zhì)量流量計信號處理系統(tǒng)*

陳 坤,鄭德智,樊尚春,趙建輝

(北京航空航天大學(xué)儀器科學(xué)與光電工程學(xué)院,北京100191)

科里奧利質(zhì)量流量計(Coriolis Mass Flowmeter,以下簡稱為科氏質(zhì)量流量計,即CMF)是一種利用被測流體在振動測量管內(nèi)產(chǎn)生與質(zhì)量流量成正比的科氏力為原理制成的一種直接式質(zhì)量流量儀表[1]。CMF能直接敏感被測流體的質(zhì)量流量,同時可以檢測流體的密度、體積流量,是一種應(yīng)用廣泛的新型多功能流量測量儀表[2]。

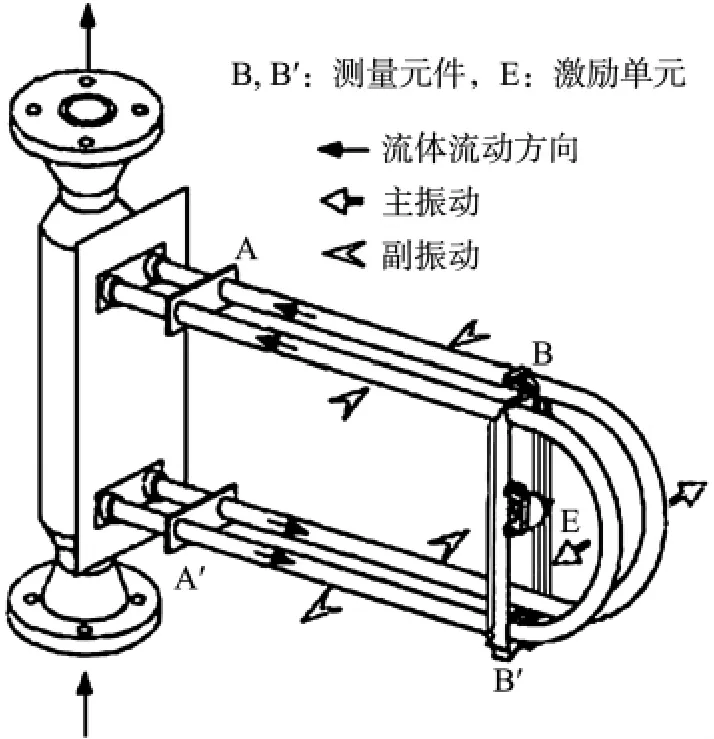

圖1為典型的雙U型管CMF,其振動測量管工作在諧振狀態(tài),流體在管中沿箭頭方向流動。由于科氏效應(yīng)(Coriolis Effect)的作用,U型管產(chǎn)生關(guān)于中心對稱軸的一階扭轉(zhuǎn)“副振動”。該一階扭轉(zhuǎn)“副振動”相當(dāng)于U型管自身的二階彎曲振動。同時,該“副振動”與所流過的質(zhì)量流量(kg/s)直接相關(guān)。因此,通過檢測U型管的“合成振動”在B,B'兩點的相位差就可以得到流體的質(zhì)量流量[3]。因此,科氏質(zhì)量流量計信號解算歸根到底是兩同頻率正弦信號相位差的解算。

圖1 CMF工作機理

傳統(tǒng)的CMF的信號處理方式大多為采用模擬電路對兩路拾振信號進(jìn)行濾波和過零點檢測的方法,對CMF傳感器輸出的兩路正弦信號進(jìn)行整形鑒相和高頻脈沖計數(shù)的方法獲得兩路信號的相位差和頻率[4]。但該方法需要大量使用模擬器件,噪聲和干擾對測量的影響較大,并且在相位差較小時,受計數(shù)時鐘精度的影響,測得相位差精度相對較低。北京航空航天大學(xué)鄭德智利用數(shù)字式的相位差檢測原理,采用DSP對采樣后的信號進(jìn)行時域分析,并采用曲線擬合的方法尋找曲線過零點,進(jìn)而算出零點間的時間差和相位差。該方法對于傳統(tǒng)的雙U型管CMF精度較高,但對于新型的直管型和類直管型CMF,由于其滿量程相位差微小,且工作頻率較高,時間差很小,該方法已難以滿足使用要求[5]。合肥工業(yè)大學(xué)徐科軍參考國外的專利采用可變的采樣頻率進(jìn)行采樣,利用DSP作為二次儀表的處理核心。針對非整周期采樣時的頻譜泄露,采用粗測,細(xì)測和頻率跟蹤的思路[6]。但是該方法僅能測量出跟蹤過程始末的頻率變化量,對于其中的變化過程無法檢測。并且由于在解算過程中是以解算結(jié)果作為控制采樣率的依據(jù),使得算法的實時性較差。在跟蹤頻率時,要不斷變化采樣頻率進(jìn)行采樣計算,再比較功率譜值的大小,以確定實現(xiàn)整周期采樣的頻率,其時間長達(dá)10 s以上,無法滿足儀表在使用上的實時性要求[7]。

1 相位差解算原理

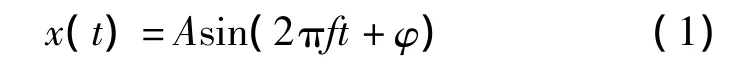

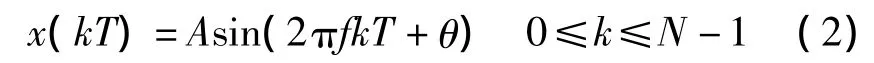

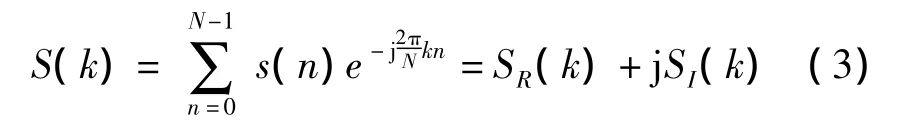

本系統(tǒng)算法的核心是利用快速傅里葉變換(FFT)算法計算離散后的兩路CMF信號的相位差。將CMF的輸出信號理想化抽象為

在一定的條件下對輸出信號進(jìn)行采樣,設(shè)采樣周期為T,采樣點數(shù)為N,則

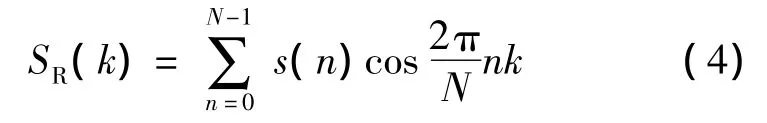

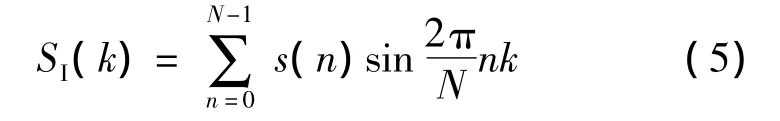

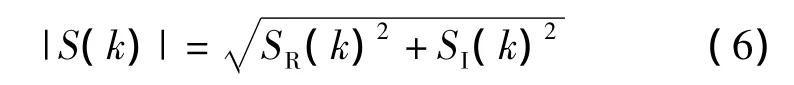

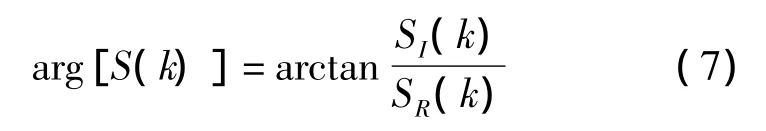

采用離散傅里葉變換,其功率譜表達(dá)式為:

其中實部表達(dá)式為:

虛部表達(dá)式為:

相應(yīng)的幅值表達(dá)式為:

相位表達(dá)式為:

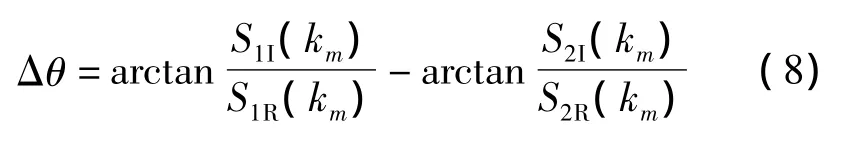

對采樣數(shù)據(jù)進(jìn)行處理后,進(jìn)行快速傅里葉變換,找到其最大功率譜對應(yīng)的k值,記為km,km對應(yīng)的頻率即為基波頻率,從而得到相位差的表達(dá)式:

式中:S1I(km)、S1R(km)、S2I(km)、S2R(km)分別為傳感器兩路信號經(jīng)FFT變換后其基波頻率所對應(yīng)的最大功率譜的虛部和實部[8]。

對于CMF輸出的周期信號,要保證FFT計算基頻和相位差的準(zhǔn)確性,要求對信號進(jìn)行整周期截取,并嚴(yán)格等時間間隔采樣,否則在頻域上將產(chǎn)生頻譜泄漏誤差[9]。這是由于FFT得到的頻譜是離散譜線,是將信號頻譜與矩形窗函數(shù)頻譜作復(fù)卷積后,按歸一化頻率分辨率Δω=2π/N等間隔抽樣的結(jié)果。如對周期信號進(jìn)行整周期采樣,即T0=mT。其中T0為窗函數(shù)長度,T為信號周期,m為整數(shù)。則可以得出

式(9)中f為信號頻率,Δf為頻率分辨率,對應(yīng)于頻譜圖上兩條譜線間的間隔。從式(9)可以看出被分析信號的頻率恰好為Δf的整數(shù)倍,即正好正對某一譜線,這時計算得到的信號頻率、幅值和相位將是準(zhǔn)確的。如果進(jìn)行非整周期截斷,截斷信號周期延拓后的新信號將不再等于原周期信號,造成信號波形的截斷,這就導(dǎo)致信號真實頻率和頻率分辨率之間的比值m不再是一個整數(shù),而是一個實數(shù)。實際上就是信號的頻率將處在離散頻譜的兩條相鄰譜線之間,而不再是正對某一譜線。這時因為頻譜泄漏的影響,由譜線反映出的信號頻率、幅值和相位就都存在一定的誤差,不能滿足測量精度要求。因此需要在軟件上和硬件上進(jìn)行額外的處理,使之盡量滿足整周期采樣的要求使頻譜泄漏的影響降到最低的程度[10]。

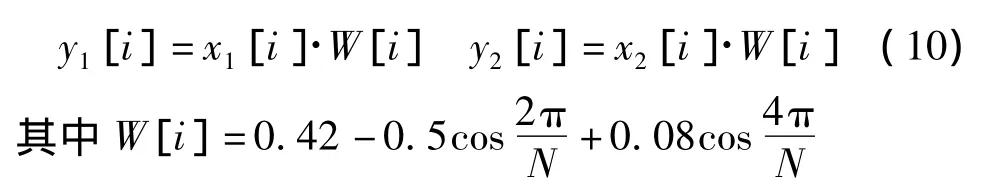

硬件上,設(shè)計實時的頻率跟蹤電路,根據(jù)CMF輸出信號的頻率變化實時改變采樣頻率,保證采樣頻率為信號頻率的整數(shù)倍,從而在最大程度上保證整周期采樣的實現(xiàn)[11]。軟件上,在進(jìn)行FFT運算之前,對采樣信號進(jìn)行加窗函數(shù)處理。對兩路信號分別加Blackman窗函數(shù),進(jìn)一步減少頻率跟蹤過程中的非整周期采樣因素造成的頻譜泄漏的影響[12]。

2 頻率跟蹤和閉環(huán)采樣的實現(xiàn)

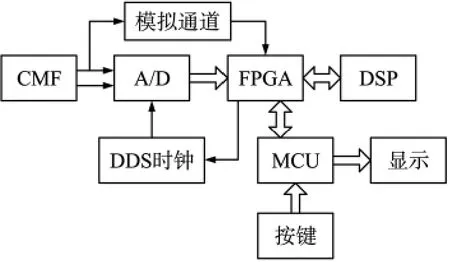

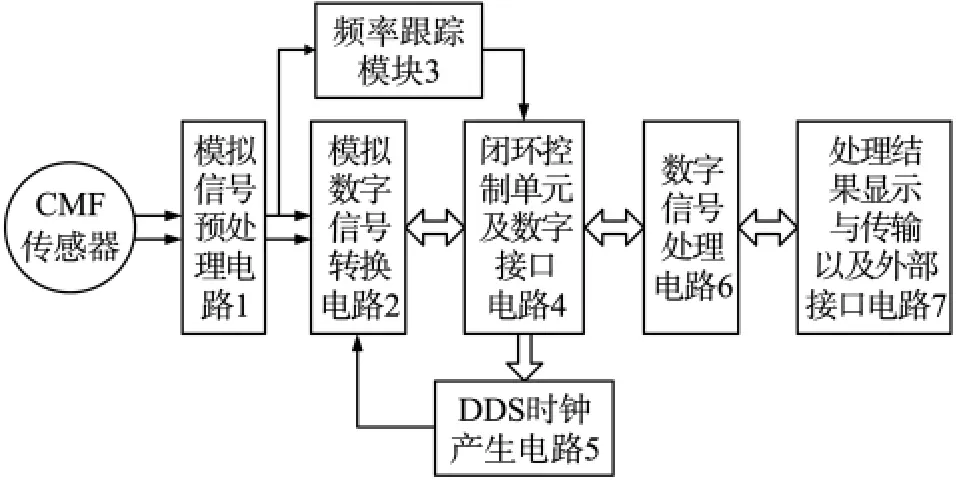

由于在CMF工作過程中由于流量的波動和外界的干擾工作頻率會發(fā)生緩慢的波動,為實現(xiàn)整周期采樣,必須進(jìn)行實時的頻率跟蹤,準(zhǔn)確獲取信號的當(dāng)前頻率,并以此頻率為依據(jù)控制AD采集,保證采樣頻率時刻為信號頻率的整數(shù)倍。為此,設(shè)計如圖2虛線框內(nèi)所示的實現(xiàn)整周期采樣的頻率跟蹤和閉環(huán)采樣模塊。

圖2 系統(tǒng)組成

傳感器輸出的兩路正弦信號經(jīng)過模擬通道的預(yù)處理,在模擬通道內(nèi)進(jìn)行放大濾波和整形后,正弦信號被整形成同頻率的方波信號,送入FPGA內(nèi)。在FPGA內(nèi)用高頻脈沖對分頻后的信號計數(shù),根據(jù)計數(shù)值和計數(shù)頻率就可以得到信號的當(dāng)前頻率。以此頻率為依據(jù),控制AD芯片以信號頻率的若干整數(shù)倍的采樣頻率進(jìn)行數(shù)字模擬量轉(zhuǎn)換,保證完整信號周期內(nèi)采樣整數(shù)個點。利用這種方法實時地進(jìn)行頻率跟蹤,當(dāng)信號頻率發(fā)生變化時,實時地改變采樣頻率,使得系統(tǒng)始終滿足整周期采樣的要求。

模擬數(shù)字轉(zhuǎn)換電路采用音頻編解碼(CODEC)芯片TLV320AIC23B。該芯片能夠?qū)崟r同步地采集兩路信號而不引入相位差,并且采樣頻率fs與芯片主時鐘fm成比例關(guān)系,可以根據(jù)芯片主時鐘靈活改變采樣頻率。本系統(tǒng)正是利用該芯片的這一特點,通過改變系統(tǒng)時鐘頻率的方式調(diào)整采樣頻率。其中采樣頻率被配置為芯片時鐘頻率的1/256,即fs=fm/256。系統(tǒng)采用DDS時鐘產(chǎn)生電路產(chǎn)生AD所需的時鐘信號,DDS芯片采用AD9850,其理論輸出的頻率分辨率為0.029 1 Hz,滿足系統(tǒng)設(shè)計要求。由閉環(huán)控制單元FPGA控制,根據(jù)當(dāng)前信號的頻率產(chǎn)生倍頻的時鐘信號輸出,經(jīng)過比較器整形為方波時鐘信號后直接驅(qū)動AD芯片進(jìn)行AD采集。本系統(tǒng)中fclk=65 536·f0,則fs=256·f0,即控制AD芯片每周期采樣256點,方便后續(xù)的FFT算法進(jìn)行2N點的運算。

閉環(huán)控制由ALTERA公司的FPGA(Field Programmable Gate Array)芯片EP2C20Q240實現(xiàn),內(nèi)部程序由Verilog硬件描述語言編輯實現(xiàn),是本系統(tǒng)的控制核心。一方面根據(jù)跟蹤到的頻率值進(jìn)行計算,輸出控制字驅(qū)動DDS產(chǎn)生相應(yīng)頻率的時鐘輸出,以實現(xiàn)采樣頻率的閉環(huán)控制;另一方面與AD采集芯片構(gòu)成數(shù)據(jù)接口,將AD采集回的數(shù)據(jù)做串并轉(zhuǎn)換并用乒乓操作的方式進(jìn)行緩存,并與DSP進(jìn)行數(shù)據(jù)通信,參與后續(xù)計算。

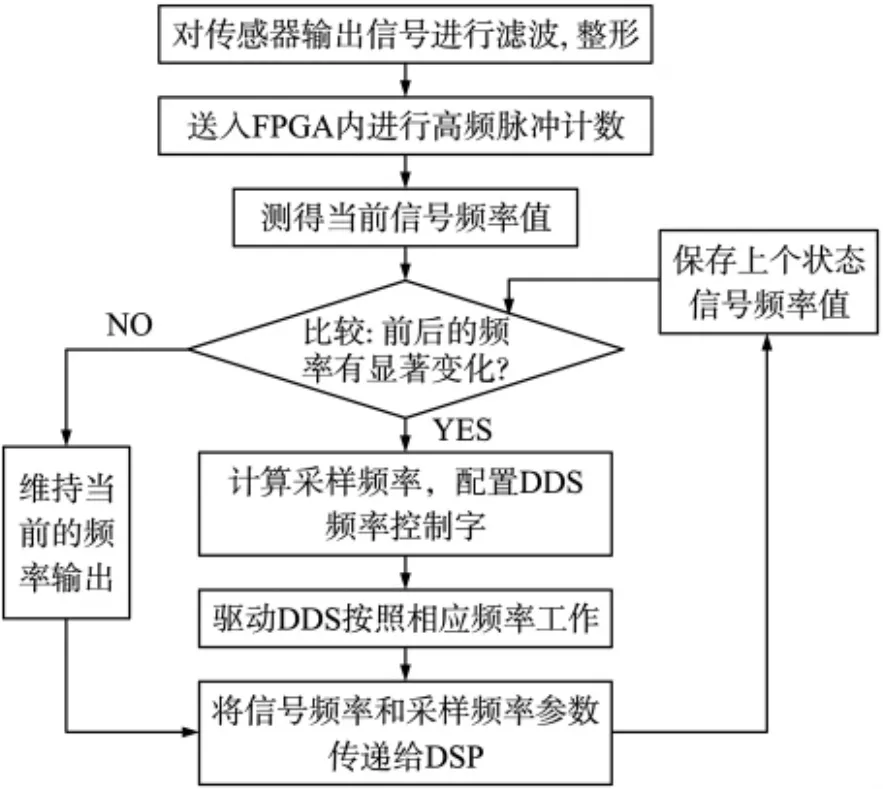

FPGA的硬件邏輯及外圍電路實現(xiàn)的頻率跟蹤算法流程如圖3所示:對傳感器輸出信號進(jìn)行濾波后放大,運放工作于飽和狀態(tài)將正弦信號整形成方波信號,送入到FPGA內(nèi)部。系統(tǒng)時鐘由75 MHz的晶振提供,在FPGA內(nèi)經(jīng)過PLL鎖相倍頻后利用150 MHz的高頻時鐘對分頻后的方波信號進(jìn)行高頻脈沖計數(shù),由計數(shù)值和計數(shù)時鐘頻率即可得到信號的周期值,進(jìn)而可得到信號的頻率。由于時鐘頻率較高,頻率計算的分辨率較高。將當(dāng)前頻率鎖存,待下個頻率值到來時進(jìn)行比較。如果頻率變化范圍超過設(shè)定閾值,則啟動DDS輸出控制模塊,根據(jù)當(dāng)前的頻率值乘以65 536,以此為依據(jù)配置AD9850使之輸出相應(yīng)頻率的AD時鐘信號。由于采樣頻率為時鐘頻率的1/256,故采樣頻率即為信號頻率的256倍,從而實現(xiàn)了整周期采樣,即每周期采樣256點,方便后續(xù)2N點的FFT計算,同時最大限度的減小頻譜泄漏。適當(dāng)設(shè)定頻率控制的閾值,便可實現(xiàn)實時的檢測信號頻率的變化,依據(jù)信號頻率實時改變采樣頻率實現(xiàn)采樣率的閉環(huán)控制,保證了全過程整周期采樣的實現(xiàn)。

圖3 頻率跟蹤算法流程圖

3 系統(tǒng)實現(xiàn)

如圖4所示,整個系統(tǒng)由模擬信號預(yù)處理電路,模數(shù)轉(zhuǎn)換電路,頻率跟蹤電路,閉環(huán)控制單元及數(shù)字接口電路,數(shù)字信號處理電路,顯示傳輸及外部接口電路等部分組成。其中頻率跟蹤和閉環(huán)時鐘產(chǎn)生電路構(gòu)成了閉環(huán)采樣控制模塊,是系統(tǒng)控制的核心,保證了系統(tǒng)整周期采樣的實現(xiàn),是系統(tǒng)算法準(zhǔn)確實現(xiàn)的前提。整周期采樣后的數(shù)據(jù)在FPGA內(nèi)以雙端口RAM(DPRAM)的形式與數(shù)字信號處理電路進(jìn)行數(shù)據(jù)通信,將數(shù)據(jù)送至DSP內(nèi)進(jìn)行加窗函數(shù)運算和FFT運算,實時解算出CMF輸出信號的相位差和時間差。數(shù)字信號處理電路采用TI的浮點型DSP芯片TMS320VC33,能夠滿足系統(tǒng)計算速度和精度的要求。解算結(jié)果經(jīng)過液晶顯示器顯示,并能夠查詢累計流量等信息,提供良好的人機界面接口,系統(tǒng)帶有10 kHz頻率信號和4~20 mA電流環(huán)輸出,滿足工業(yè)現(xiàn)場的需求。顯示與接口電路由單片機C8051F124控制液晶顯示模塊及外圍接口電路實現(xiàn)。

圖4 系統(tǒng)功能模塊

4 實驗驗證

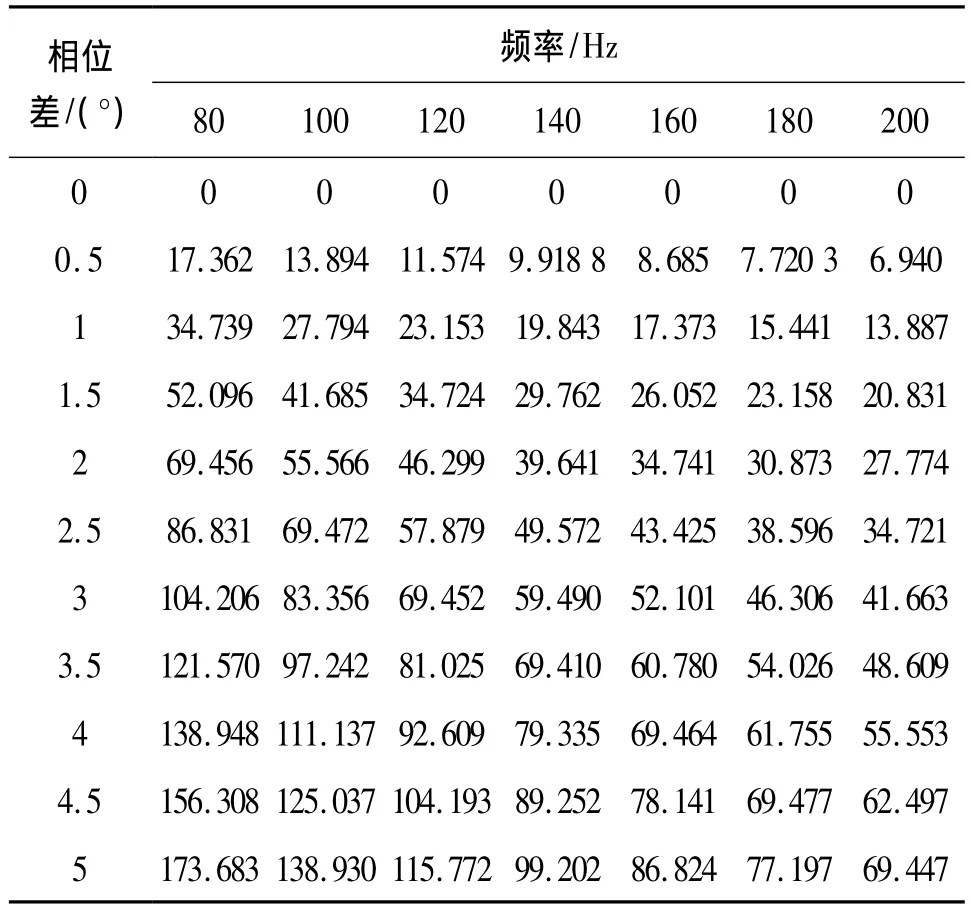

對系統(tǒng)進(jìn)行實驗驗證,利用雙通道高精度信號發(fā)生器(WF1946B,相位輸出精度為0.001°)產(chǎn)生同頻正弦信號,模擬CMF傳感器的輸出。為準(zhǔn)確模擬傳感器的輸出,加入了相對幅值為0.1的高斯白噪聲。利用該系統(tǒng)對兩路信號進(jìn)行處理,解算出兩路信號的相位差。由于CMF的流量與時間差成正比例關(guān)系,即Q=k*Δt,其中k為流量系數(shù),可以通過標(biāo)定得出。故直接解算出兩路信號的時間差,如表1所示。考察系統(tǒng)解算的精度和線性度。分別選取信號頻率為80~200 Hz,解算后的時間差單位為ns。

表1 時間差實驗數(shù)據(jù)記錄 單位:ns

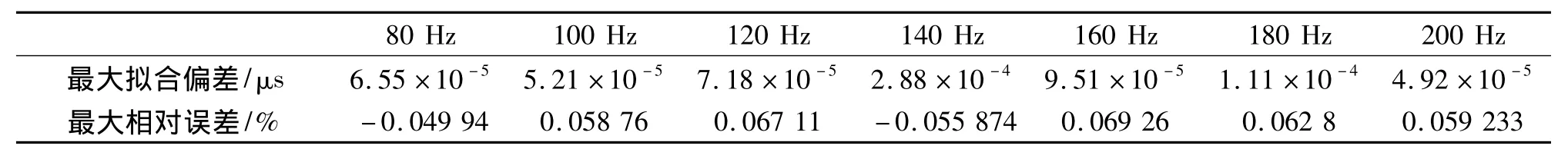

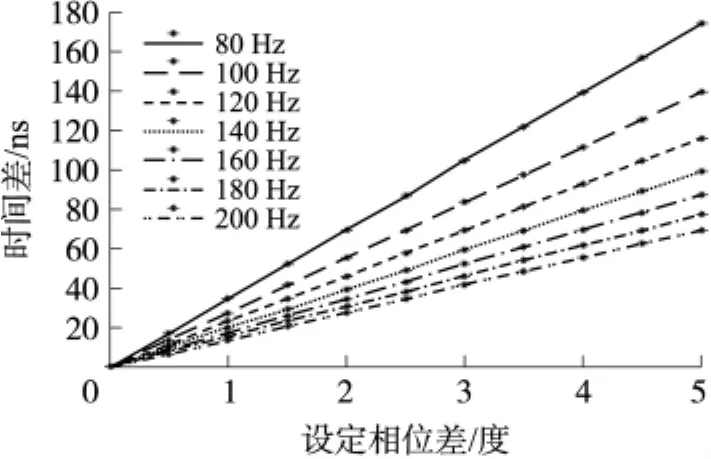

分析以上數(shù)據(jù),當(dāng)設(shè)定相位差為零時,將系統(tǒng)解算結(jié)果作為初始相位差,并且在不同工作頻率時初始相位差不相等,該初始相位差稱為系統(tǒng)的零點誤差,是由于解算系統(tǒng)硬件電路中的RC濾波網(wǎng)絡(luò)引入的。由于CMF穩(wěn)定工作于諧振頻率下,滿管和空管狀態(tài)下諧振頻率并沒有顯著差別,因此可以通過系統(tǒng)調(diào)零的方法減去系統(tǒng)零點誤差,實現(xiàn)精確測量。對同頻率的數(shù)據(jù)利用最小二乘法擬合直線,考察解算結(jié)果的線性度。在工作頻率下將所有測量數(shù)據(jù)減去系統(tǒng)的零點誤差,得到當(dāng)前的絕對時間差,根據(jù)頻率轉(zhuǎn)換為相位差,考察解算結(jié)果的精度。結(jié)果如表2所示。

表2 計算誤差及擬合偏差

圖5 實驗數(shù)據(jù)擬合直線

5 結(jié)論

針對新型的直管型和類直管型CMF基頻較高,滿量程相位差微小的特點,在FFT算法的基礎(chǔ)上,提出一種由硬件電路實現(xiàn)頻率自動跟蹤,實時調(diào)整AD采樣率,實現(xiàn)采樣率閉環(huán)控制的CMF信號處理系統(tǒng),減小非整周期采樣帶來的頻譜泄漏的影響,實現(xiàn)了實時準(zhǔn)確的相位差解算。實驗結(jié)果表明,該系統(tǒng)解算精度較高,測量誤差小于0.1%,測量頻率范圍廣,在新管型CMF的二次儀表中具有廣闊的應(yīng)用前景。

[1]Henry M P.Coriolis Meter Digital Transmitter Technology:Emerging Themes[J].IEEE Seminar on Advanced Coriolis Mass Flow-Metering.Oxford University,2003.

[2]邢維巍,樊尚春,鄭德智.科氏質(zhì)量流量計數(shù)字閉環(huán)系統(tǒng)的設(shè)計與實現(xiàn)[J].儀器儀表學(xué)報,2006,27(5):461 -465.

[3]鄭德智,樊尚春,邢維巍.?dāng)?shù)字科氏質(zhì)量流量計閉環(huán)系統(tǒng)及信號解算[J].北京航空航天大學(xué)學(xué)報,2005.31(6):623 -626.

[4]Henry M P,Clarke D W,Vignos J H.Digital Flowmeter[P].U.S Patent,2002.

[5]鄭德智,樊尚春,邢維巍.科氏質(zhì)量流量計相位差檢測新方法[J].儀器儀表學(xué)報,2005,26(5):441 -443.

[6]徐科軍,于翠欣,蘇建徽,等.基于DSP的科氏質(zhì)量流量計信號處理系統(tǒng)[J].儀器儀表學(xué)報,2002,23(2):170 -175.

[7]徐科軍,姜汗科,蘇建徽,等.科氏流量計信號處理中頻率跟蹤方法的研究[J].計量學(xué)報,1999,20(4):304 -307.

[8]楊新華,陳玉松,金興文.基于FFT譜分析算法的高精度相位差測量方法[J].自動化與儀器儀表,2006年第6期.

[9]張海濤,任開春,涂亞慶.科氏質(zhì)量流量計相位差的一種高精度估計方法[J].傳感器技術(shù),2005,24(3):67 -70.

[10]楊俊,關(guān)可,梁佳.DFT變換法在科氏質(zhì)量流量計相位差檢測中的應(yīng)用研究[J].傳感技術(shù)學(xué)報,2006,19(12):6.

[11]侯毅,施文康,遲穎.科里奧利質(zhì)量流量計的原理及其誤差分析[J].自動化儀表,2001,22(9):18 -20.

[12]吳俊青.相位差的數(shù)字化測量研究[J].應(yīng)用基礎(chǔ)與工程科學(xué)學(xué)報,2005,3:99 -104.