基于ARM與FPGA的嵌入式開放性運動控制器的設計與開發

萬林 唐厚君 賀超 黃維芳

(上海交通大學,上海 200240)

0 引言

在國內市場上已經出現了許多種類的運動控制器,這些運動控制器有著各自的硬件平臺和軟件平臺,這一方面反映了國內運動控制器市場的活躍,但另一方面暴露了阻礙國內運動控制器向開放式、模塊化方向發展的原因。隨著計算機技術和現代電子技術迅速發展與廣泛應用,深入研究基于新體系架構、新技術、高性能、低成本、開放式多軸聯動運動控制器具有重要的理論意義和應用價值[1,2]。本文基于ARM和FPGA的硬件平臺,研發了一種適用于現代制造系統需求的低成本的開放式嵌入式多軸運動控制器,其模塊化的設計思想使得該控制器非常適合于二次開發。

1 系統硬件方案的設計

嵌入式運動控制器通常有兩個控制核心。一個是MCU,主要負責人機交互部分并且與運動控制器的運算單元進行通信,另一個控制核心主要負責運動控制過程中的大量復雜的運算工作。這個核心的運動控制單元大致可以分為三種:DSP、專用運動控制芯片、FPGA。利用DSP通過軟件的方式實現運動控制中的插補運算,具有編程簡單、靈活等方面的優勢,但是無法達到像專用運動控制芯片那樣的高實時性,高可靠性,特別是對多軸控制更是如此;專用運動控制芯片雖然具備易使用,穩定性好,功能強大,實時性強等優點,但是專用的控制芯片可塑性和靈活性較差,很難根據客戶的具體要求定制;FPGA則是通過軟件代碼的方式生成對應的硬件電路,它兼備DSP和專用運動控制芯片的優點,同時隨著FPGA制造工藝的進步,FPGA芯片的集成度越來越高,單位邏輯資源的價格大幅下降,因此使用FPGA作為運動控制器的一個控制核心是一個非常好的選擇。對于運動控制器的另外一個核心MCU,本系統選用ARM,ARM在嵌入式市場上占有率非常高,具有非常出色的性能以及價格優勢,同時有許多第三方工具、軟件對ARM提供支持。

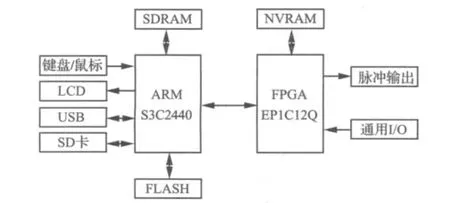

系統硬件結構如圖1所示。

圖1 運動控制器硬件結構圖

2 系統軟件方案的設計

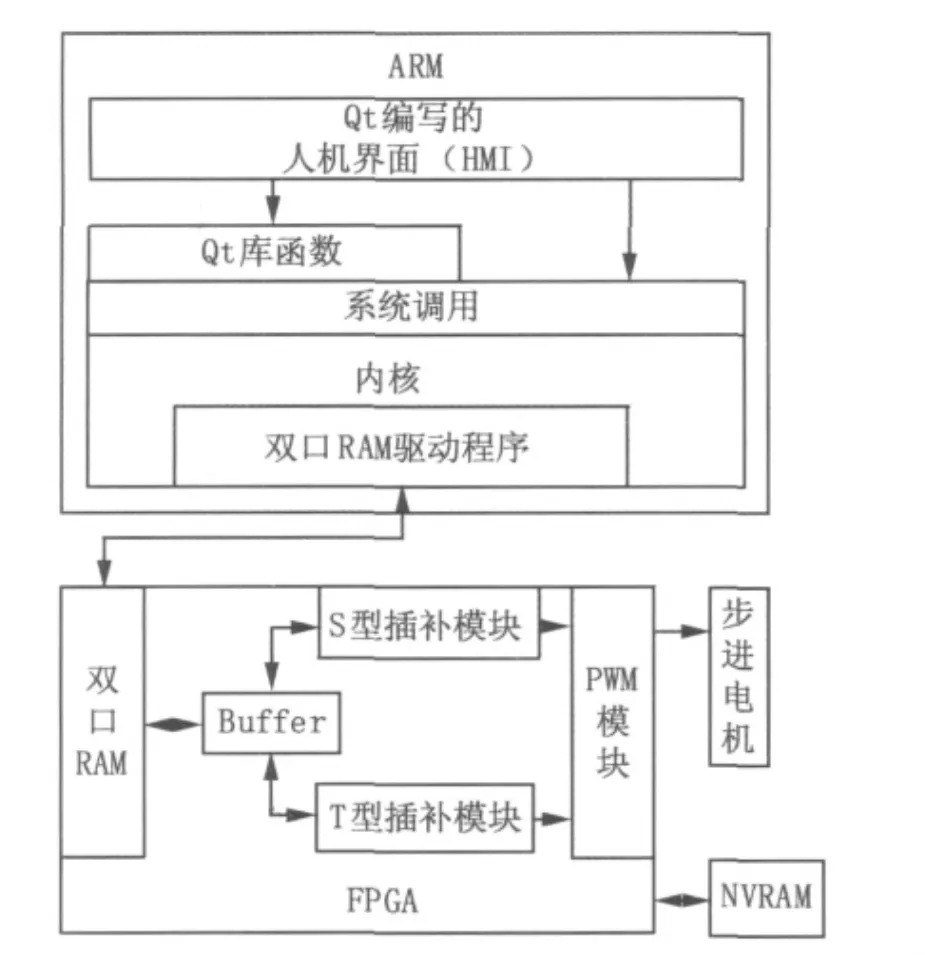

在該系統中ARM需要完成人機交互和與運動控制器的運算單元進行通信等多任務,這些可以借助于Linux實現。Linux是一種開源的操作系統,它以高效性和靈活性著稱,具有多任務的能力,同時Linux內核提供了對常規設備的支持:鍵盤、鼠標、SD卡等等;在該系統中人機交互界面通過Qt實現,Qt是一個跨平臺的C++圖形用戶界面的程序框架,同時是開源的,具有非常強的可移植性,并且Qt提供多達250個以上的C++類,可重用性非常好,給用戶的開發帶來了極大的方便。并且Linux和Qt都可以在一定的許可權限下免費獲得,這極大地降低了系統成本以及提高系統的開放性。

由于ARM上移植了Linux操作系統,因此ARM需要通過驅動程序才能夠訪問FPGA的硬件資源。FPGA具有非常豐富的硬件資源,可以實現各種硬件接口協議。實現接口較簡單的一種方法是在FPGA上實現一個雙口RAM,并借助于在Linux中編寫雙口RAM的驅動程序,ARM便能夠方便地和FPGA進行通信。ARM按照用戶的運動控制要求將規劃化好的運動代碼通過雙口RAM發送給FPGA,并且從雙口RAM處獲取運動單元的狀態信息。

在該系統中FPGA通過雙口RAM從ARM處獲取規劃好的運動代碼,而后通過插補算法將運動代碼轉化成一定數目且頻率可調的脈沖來驅動步進電機完成相應的運動,同時FPGA將運動單元的狀態信息通過雙口RAM反饋給ARM。

運動控制器系統的軟件整體結構如圖2所示。

圖2 運動控制器軟件整體結構圖

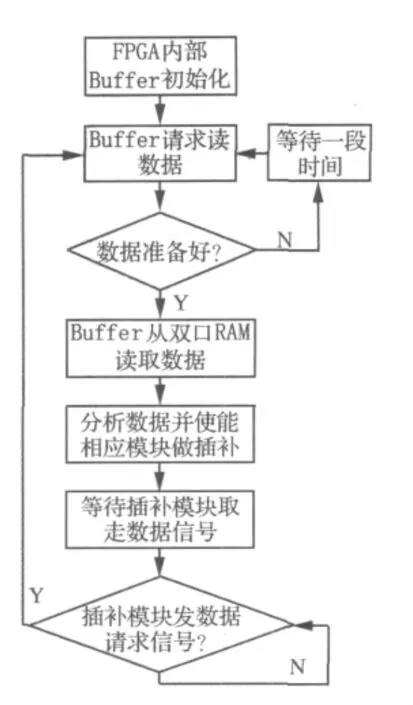

3 ARM和FPGA通信的設計

FPGA內部的雙口RAM分成兩部分:上行區和下行區。首先ARM會將規劃好的運動代碼寫到雙口RAM的下行區中,并且通知FPGA數據已經準備好,這時FPGA從雙口RAM的下行區中讀取數據,當FPGA取完數據之后便給ARM發出信號,之后ARM才能夠繼續向雙口RAM的下行區寫入數據。當FPGA處理完一段運動代碼后便將運動單元的狀態——當前坐標、誤差、速度、加速度等信息寫到雙口RAM的上行區,并且通知ARM準備獲取運動單元的狀態信息,這時ARM從雙口RAM的上行區中讀取數據,在此過程中FPGA停止向雙口RAM的上行區中寫入數據,當ARM取完數據之后便給FPGA發送數據已取完的信號,這時FPGA才能夠繼續向雙口RAM的上行區寫入運動單元的狀態信息。

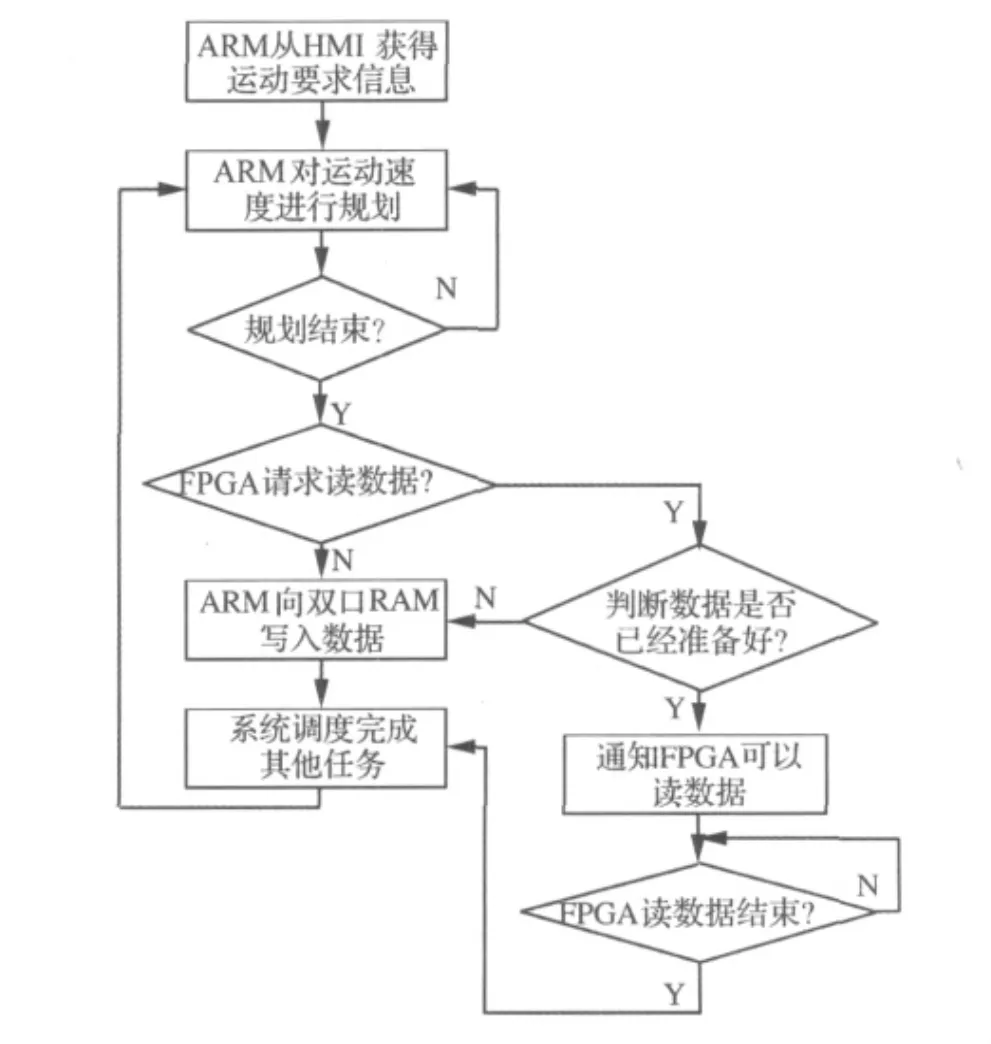

圖3、圖4分別說明了當FPGA從ARM處讀取運動控制信息時FPGA和ARM的程序流程:(注:ARM從 FPGA處獲得運動單元的狀態信息時ARM和FPGA的程序流程和該情況類似,這里不再詳述)

圖3 FPGA從ARM讀運動信息時FPGA程序流程

圖4 FPGA從ARM讀運動信息時ARM程序流程

4 運動控制器插補算法的設計

常見的插補方法有數字脈沖相乘法,逐點比較法,最小偏差法,數字積分法,目標點跟蹤法。其中數字積分法具有邏輯功能強的特點,可以實現一次、兩次甚至高次曲線的插補,適合于多坐標軸聯動控制[3]。本文利用數字積分法設計了多軸運動控制器的S/T型加減速的插補算法。

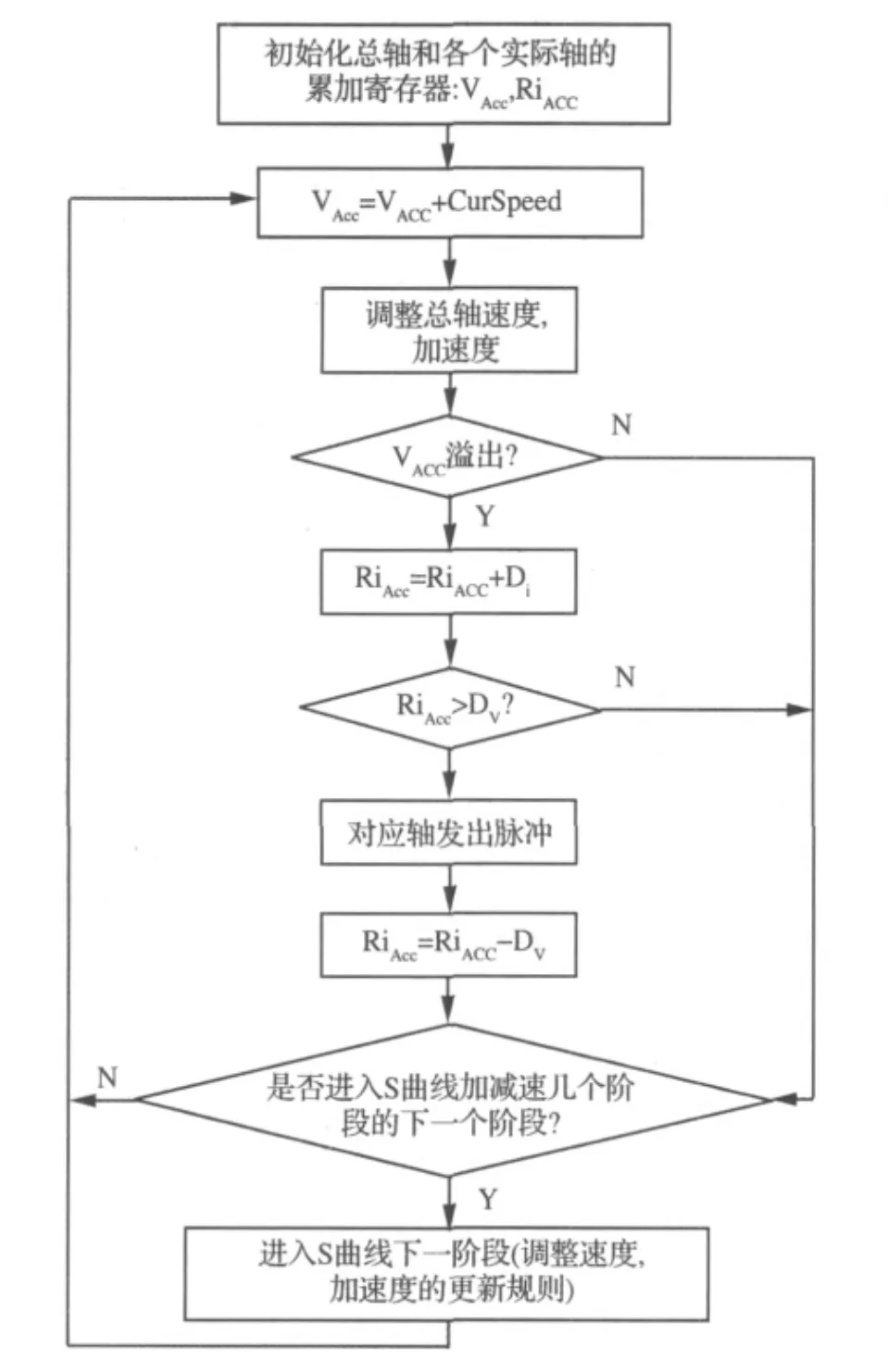

T型加減速的插補算法較簡單,本文主要討論S型加減速的插補算法,其具體的算法流程圖如圖5所示:(其中VACC為總軸的累加寄存器,RiACC(i=1,2,3...)為各個實際軸的累加寄存器,CurSpeed為總軸當前的運動速度,DV為運動總軸要運行的距離,Di(i=1,2,3...)為各個實際軸要運行的距離)

首先,FPGA通過雙口RAM從ARM那讀取規劃后的運動控制信息,包括各個軸合成的總軸的末速度,最大速度,最大加速度,加加速度,運動距離以及各個分軸的運動距離等。在每個插補周期中總軸累加寄存器累加當前時刻運動控制器總軸的運動速度,當總軸累加寄存器溢出時,各個分軸累加寄存器累加各個分軸的運動距離,當其中某個分軸累加寄存器中的值大于等于運動控制器總軸的運動距離時,此時該軸就會發出一個脈沖。在插補過程中必須在每個插補周期中對運動總軸的的速度,加速度以及運動距離進行控制。

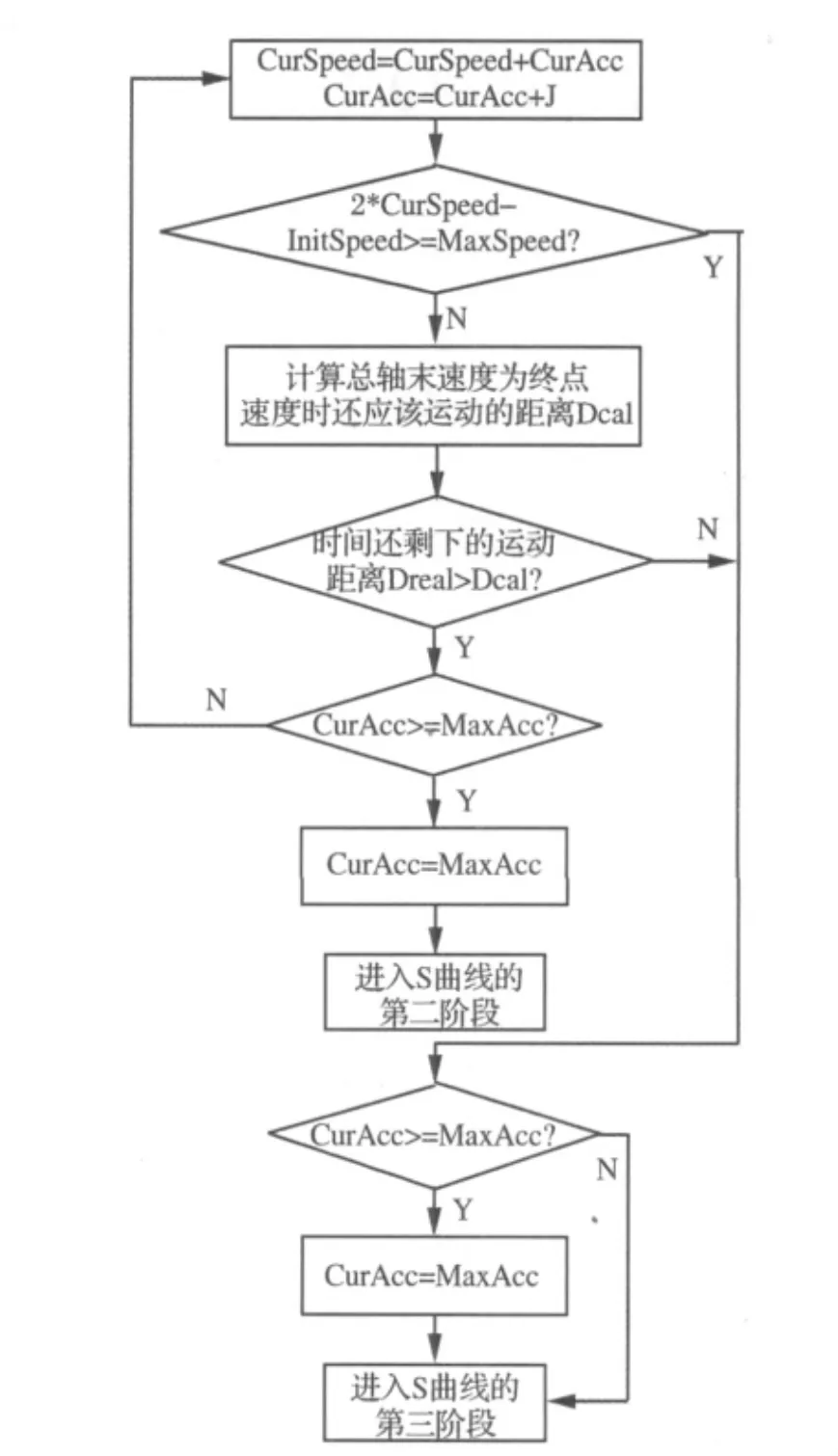

另外一個要討論的是在S型加減速中如何判斷運動單元何時該進入S型加減速的下一階段。S型加減速通常有七個階段,其中比較典型的是由S型加減速的第一階段進入S型加減速的下一階段,程序流程圖如圖6所示:(Cur Speed,Cur Acc,J,Init Speed,Max Speed和Max Acc分別為總軸當前速度,當前加速度,加加速度,初始速度,最大速度和最大加速度)

圖5 S型加減速程序流程圖

圖6 S型加減速由第一階段進入下一階段流程圖

5 結束語

本文討論了一種基于ARM和FPGA的嵌入式開放性運動控制器的硬件和軟件方案設計,在ARM上移植了Linux和Qt,利用Qt設計了人機交互界面,重點討論了ARM和FPGA之間通信的實現以及運動控制中S型加減速插補算法的實現。該控制器可根據用戶的要求很方便的裁剪,例如可以根據用戶的要求在FPGA模塊內部多增加一個不對稱型加減速插補模塊,而不需要對硬件電路以及FPGA的其他模塊的代碼做任何修改,再者可以在ARM上面實現網絡通信的功能,這樣就能夠遠程對運動控制器進行在線操作和診斷。

[1] GOODWIN G G,GRAeBE S F,SALGADO M E.Control System Design[M].International,Prentice-Hall International Englewood Cliffs,New Jersey,2001.

[2] 吳宏,龔小云,等.運動控制器的現狀與發展[C].CMES年會專輯.2004,(1):24-27.

[3] 李恩林.數控系統插補原理通論[M].北京:國防工業出版社,2008:75.