基于BiSS協議的編碼器及其在伺服驅動系統中的應用

霍海龍

(河南省神火煤業公司新莊煤礦 信息自動化中心,河南 476600)

0 引言

高性能的伺服驅動系統往往采用高分辨率和高通信速度的編碼器作為電機的位置傳感器,以獲得速度和絕對值位置等信息。而高分辨率和高速度的編碼器通常要求可以實現正余弦信號到位置參量的轉換,并且通過較少數量的導線傳輸高速的數字信號,以滿足伺服驅動系統對位置信息更高的精度和響應速度要求[1]。目前伺服驅動系統多采用絕對值編碼器,因為其分辨率比增量型編碼器顯著提高,這對于控制系統的初始轉矩和提高響應速度有很大的改善。

1 BiSS協議

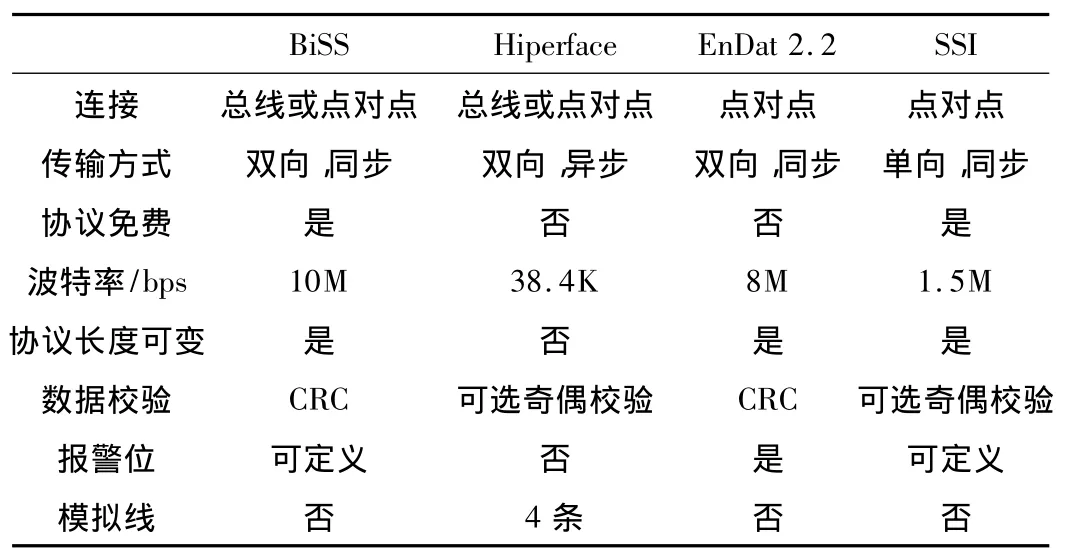

德國 IC-Haus公司提出的 BiSS(Bidirectional Synchronous Serial)協議是一種開放式協議,具有高速(10MHz)、全數字的特點,并且可以實現1個主站對8個從站的總線連接。其在通訊速度、產品適應性以及開發成本等綜合方面,遠比其他一些同類常用串行通訊協議更具優勢。下表為BiSS協議與其他一些主流通訊協議的比較。

由表1可知,BiSS協議通訊速率高于其它協議,總線連接方式、報警位、協議長度可調整,工業應用靈活性好,無協議產權成本,全數字接口無模擬量器件成本。可見,在通信速度、產品適應性、成本等綜合方面,BiSS協議具有很好的發展前景[5]。

表1 BiSS協議與其它同類協議對比

通過BiSS接口電路可以在編碼器和驅動器之間實現如下兩種工作模式[4]:

傳感器模式(Sensor-Mode):具有很高的位置傳感更新速度;

寄存器模式(Register-Mode):用于配置編碼器或驅動器。

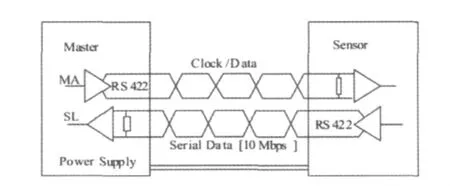

如圖1所示,在點對點的連接方式下由主機發送 MA(master)信號,編碼器返回 SL(slave)信號,SL的返回信號是和MA的時鐘同步的。

圖1 BiSS數據傳輸連接示意圖(點對點連接)

1.1 傳感器模式

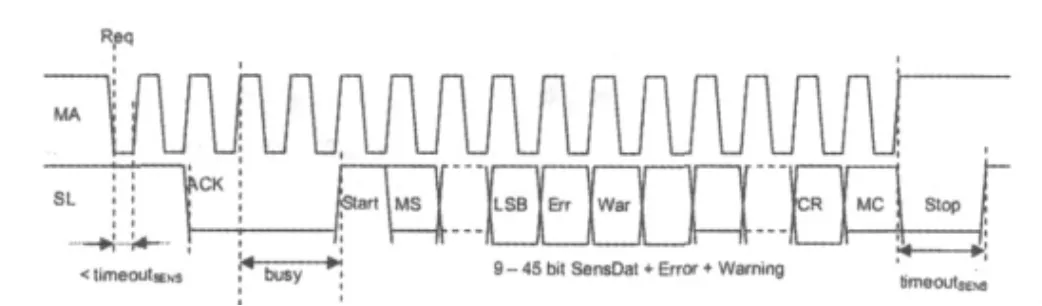

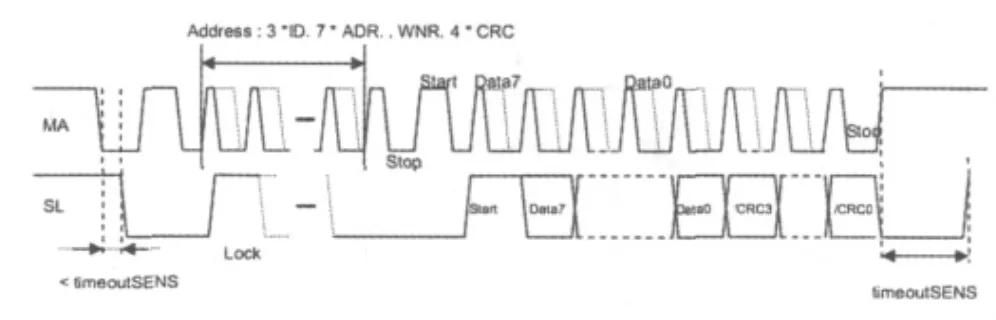

在運動控制系統中,編碼器將連續工作在傳感器模式下。目前伺服驅動的架構所采用的更新速度為16 kHz或更高,因此為了優化反饋控制環的性能,系統延時必須最小化[4]。在BiSS協議接口電路中,如果以10 MHz的時鐘速度來傳輸32位的位置信息(含6位的CRC校驗位),大約需要5 us(包括編碼器內部處理延時)。傳輸時間取決于編碼器位置信息的位數和系統延時。其傳輸波形如下圖2所示。

圖2 傳感器模式下數據傳輸波形示意圖

傳感器模式下,首先由MA發出一個下降沿脈沖作為請求編碼器位置信號,緊接著在小于協議所規定的時間(timeoutSENS)內發出高電平,然后繼續提供時鐘信號。編碼器在MA發出第2個上升沿時回發一個低電平作為對請求信號的應答。SL隨后的第一高電平作為開始發送編碼器有效位置信息的起始信號。從MA的第2個上升沿至SL的第一個上升沿之間的延時包含總線延時和忙延時,BiSS協議通過延時補償,即相應地延長MA時鐘信號,來保證高波特率時通訊的準確性[2]。

編碼器位置信息的長度取決于其具體型號,處于9到45位之間,另加一位報錯位和一位警告位,最長可達47位。這些數據是通過緊隨其后的6位CRC校驗位來保證其傳輸可靠性的。SL的最后一位為可選的多周期數據,當MA高電平維持時間大于timeoutSENS時,SL恢復至高電平,結束一幀數據的傳輸。

1.2 寄存器模式

BiSS協議的一個極大優點是,通過寄存器模式,既可以讀取編碼器參數,也可以存儲參數于編碼器,并且可以查看更詳細的報警和警告內容,比如污損、過壓、過熱、老化以及用戶自定義的溫度限制等。這些參數均可以存放于一個256字節的寄存器組。BiSS協議的上位機可以通過寄存器模式對編碼器內部的非易失存儲器(EEPROM)進行讀寫操作。

在寄存器模式下,MA在提供時鐘的同時,需要攜帶寄存器地址、寄存器值等信息。寄存器地址和寄存器值等信息是通過PWM(Pulse Width Modulation)編碼實現的,即采用兩種不同占空比的PWM分別來表示數據“0”和“1”[3]。當占空比在10% ~30%之間時表示數據“0”;當占空比在70% ~90%之間時表示數據“1”。BiSS寄存器模式下的數據傳輸速率在10 kHz~250 kHz之間,通常將BiSS寄存器模式下的時鐘頻率設為通訊速率的4倍,因此當PWM占空比為25%時,表示數據“0”;當PWM占空比為75%時,表示數據“1”。

圖3為寄存器模式下讀編碼器參數波形示意圖。MA通過第一個低電平的時間大于timeoutSENS,將SL的工作模式切換至寄存器模式。然后MA發送地址序列,包括1位起始位、3位SL ID、7位寄存器地址,隨后是WNR位(“0”)和4位CRC校驗位。當讀取內部寄存器時,編碼器并不需要額外的處理時間,將立即回發對應寄存器地址的參數;當讀取外部EEPROM參數時,SL的輸出因數據準備時間的影響將產生延時。每次讀取的8位寄存器參數均由4位的CRC校驗位來保證其準確性[2]。

圖3 寄存器模式下讀編碼器參數波形示意圖

圖4為寄存器模式下寫編碼器參數波形示意圖。對寄存器進行寫參數時,編碼器確認所在的工作模式,之后MA發送地址序列以及寫信號WNR(“1”)和CRC校驗位。在第二個起始位之后,MA傳送要寫的8位參數和4位CRC校驗位,此時編碼器以滯后于MA一個時鐘的延時按二進制逐位回發這8位參數和4位CRC校驗位作為確認。往EEPROM寫參數的操作是由編碼器后臺完成的,可以通過再次讀取來確認是否已經將參數寫進去[2]。

圖4 寄存器模式下寫編碼器參數波形示意圖

2 BiSS協議編碼器應用于伺服驅動系統

基于BiSS協議的各方面優點,目前已有德國IC-Haus,美國Danaher(Hengstler)等多家公司使用。同時,BiSS與SSI協議接口兼容,方便SSI使用者和廠商系統升級。因此,BiSS協議編碼器的應用領域也越來越廣。

國內外高端交流伺服驅動系統中普遍采用FPGA+DSP結構,DSP用來實現矢量變換和其它算法流程;FPGA用以實現譯碼、A、B、Z信號輸出、I/O擴展等功能,FPGA中尚有很多資源沒有得到充分利用。開發基于FPGA的BiSS協議編碼器接口,實現與BiSS協議編碼器的雙工通訊,接收高速數據流,替代廠家提供的專用接收芯片,不僅可以大幅度降低產品成本,而且可以減少焊接芯片所需的PCB板上的空間。

由于BiSS基于RS485/422技術,10MHz的時鐘頻率可以使編碼器的位置更新速度達到5 μs~20 μs。如此高的更新速度可以保證伺服驅動系統在低速時的超平滑控制性能,如切削加工。通常,絕對值系統會發生“當速度和轉矩抖動達到四倍線速時性能降低”,而BiSS沒有這個限制。所以帶BiSS編碼器的伺服電機可以幫助設計者實現更高的精度和響應速度要求。

3 BiSS的硬件設計和FPGA的實現

3.1 硬件設計

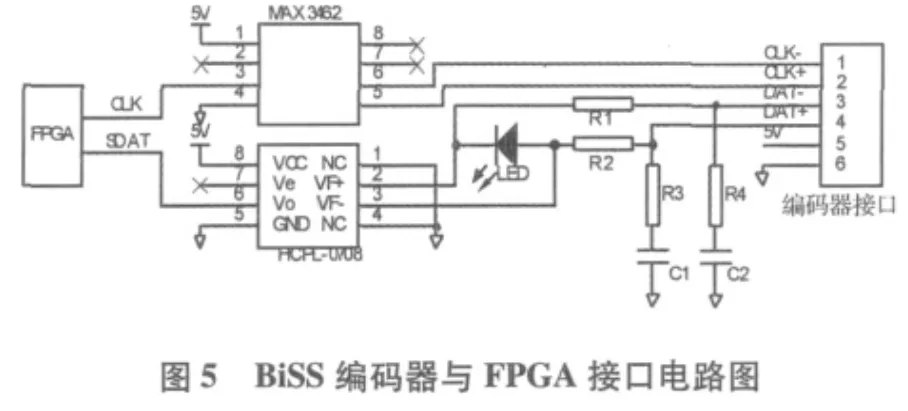

BiSS協議接口電路基于LFXP3C FPGA進行設計,BiSS時鐘信號采用MAX3462進行差分信號的發送,FPGA接收的差分數據信號采用高速光耦HCPL-0708進行電平轉換。接口電路如圖5所示。

3.2 FPGA 實現

軟件設計結構圖如圖6所示。

BiSS代碼采用VHDL語言編寫,在isp LEVER集成開發環境中進行編譯、綜合、布局布線之后,占用LFXP3C FPGA的40%左右的邏輯資源。在實際設計中,BiSS協議被設計成傳感器和寄存器兩個模塊。另外,還要特別注意對控制命令和寫數據進行鎖存,禁止在編碼器的一個讀寫操作內進行更新,以免發生讀寫錯誤。另外,在傳感器模式下,采用節拍技術對脈沖進行采樣,以增加數據傳輸的可靠性。實驗證明,在考慮到總線延時以及收發器上升下降時間等因素的影響,在第四個節拍上對編碼器回發的脈沖進行采樣所得到的數據比較準確可靠。

3.3 實驗測試結果

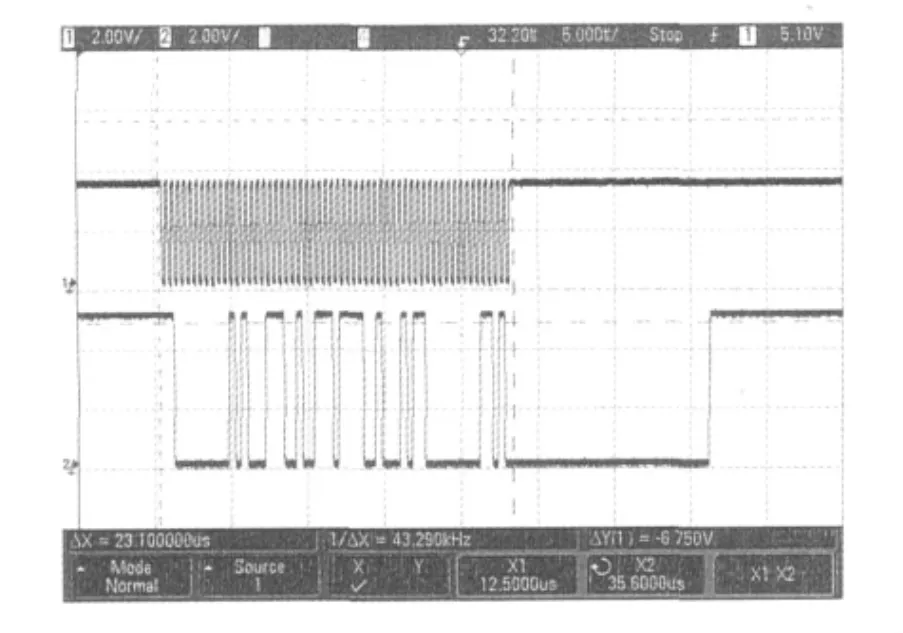

該實驗控制系統采用Hengstler AD34-1219編碼器進行測試,其多圈MT和單圈ST精度分別為12位和19位。

(1)圖7為閉環控制中,編碼器絕對值位置(MT+ST)數據傳輸波形圖。從圖中可以讀到 MT=1138,ST=244875,CRC=001101(二進制)。該傳輸速率為2.5Mb/s,傳輸一幀數據的總時間大約20us,如果采用10Mb/s通訊,則實際傳輸時間將減少到5us左右。

圖7 傳感器模式實測波形圖

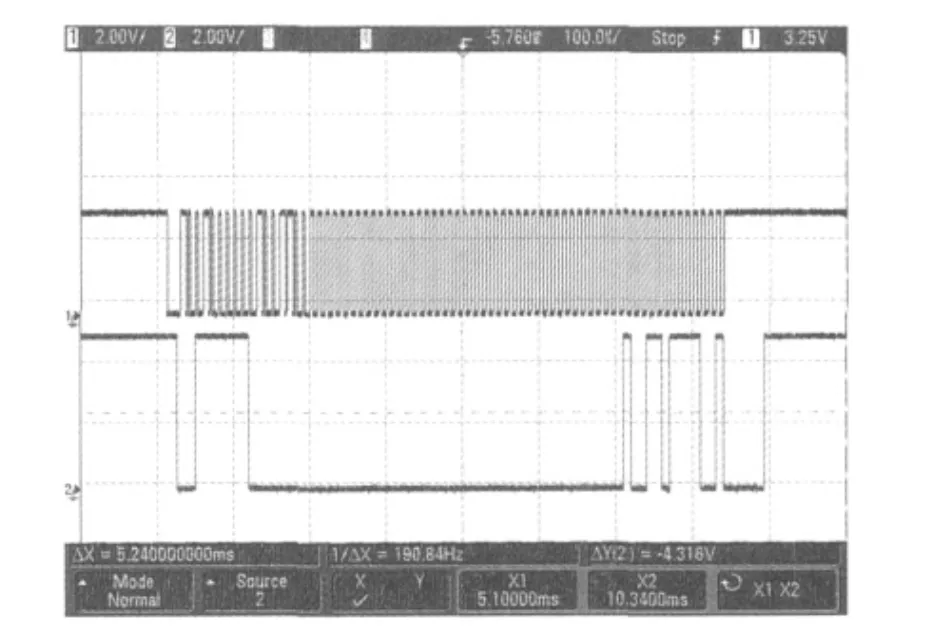

(2)圖8為讀編碼器寄存器地址0x81的數據37(BCD碼)的波形圖。傳輸速率為100Kb/s。

圖8 寄存器模式下讀編碼器參數實測波形圖

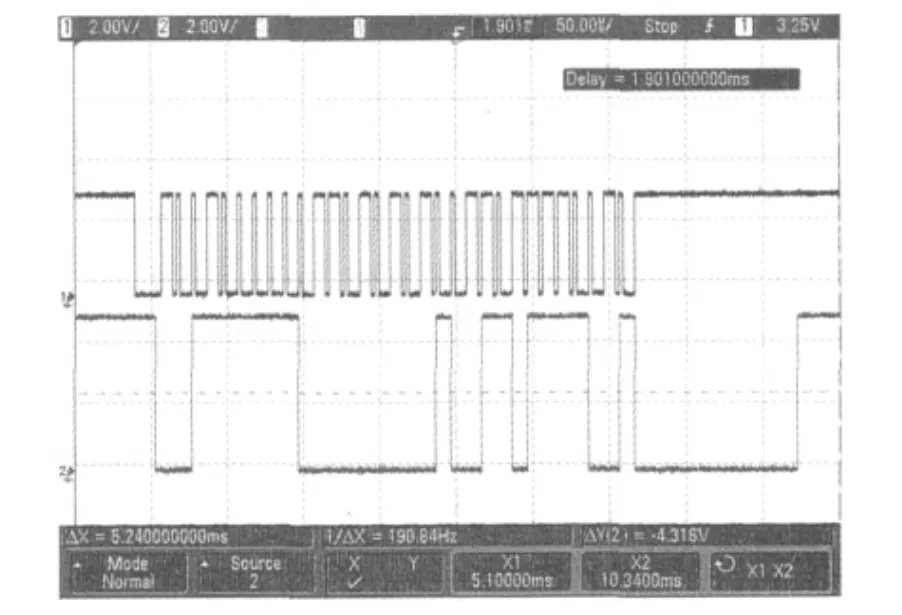

(3)寫編碼器寄存器數據波形圖

圖9為向編碼器寄存器地址0x81寫數據37(BCD碼)的波形圖。傳輸速率為100Kb/s。

圖9 寄存器模式下寫編碼器參數實測波形圖

3 結論

綜上所述,BiSS協議具有其他通信協議不可比擬的優勢。未來3年~5年內,以BiSS代表的高速雙向同步串行通訊編碼器,由于精度高,傳輸速度快(循環發送周期短),安全可靠性高和安裝調試方便等優點,必將成為伺服驅動領域編碼器的主流。

[1] JENS ONNO KRAN.基于正余弦編碼器反饋處理的FPGA在伺服驅動中的應用[J].電力電子,2008(1):12-16.

[2] HENGSTLER Technical Data sheet Interface:ACURO Interface SSI and BiSS_230606MHR[C].

[3] HENGSTLER APPLICATION NOTE:BiSS Interface Specifications[S].

[4] JENS ONNO KRAH.Resource Optimized BiSS Master Interface for High Resolution Encoders[C].PCIM EUROPE 2006PROCEEDINGS,479-484.

[5] 肖鯤.基于FPGA的BiSS協議光電編碼器通信模塊設計[J].電子測量技術,2008,31(7):188-191.