主子板結構的ΓОСТ18977多用途接口板設計*

,3

(1.空軍工程大學 工程學院,西安 710038; 2.空軍通信訓練基地,河北 保定 071051; 3.解放軍駐成都飛機工業公司軍事代表室,成都 610092)

1 引 言

俄羅斯標準ΓОСТ18977-79[1](以下簡稱ΓОСТ18977)和PTM1495-75[1](以下簡稱PTM1495)采用32位雙極性歸零串行數據(簡稱為32位碼)傳送方式來進行數字信息的傳送和交換。ΓОСТ18977規定的是飛機和直升機的成套機載設備功能互聯的類型、電信號的形式和電平,其中一部分規定了與美國標準ARINC429[1]相對應的串行碼信號的類型及其電氣標準,而與之配套的PTM1495技術資料中則規定了按照ΓОСТ18977采用雙極性碼進行信息交換的具體方法[1]。該標準在俄制軍用飛機的機載設備上得到了廣泛的應用。目前,我國對符合俄羅斯標準ΓОСТ18977的接口板不多,并且接口種類少,不能同時滿足多種主機接口的要求,影響了部隊戰斗力的提高,因此對符合ΓОСТ18977標準的多用途接口板的研制,具有重要的軍事意義和應用前景。根據以上需求,本文設計開發了一種能夠兼容USB、CPCI和PXI 3種接口的通用多用途接口板。

2 ΓОСТ18977總線簡介

在電氣標準方面,依照ΓОСТ18977的規定采用與ARINC429標準相同的雙極性歸零制的三態碼調制方式,而在對信號電平的定義上,ΓОСТ18977的定義見表1(表中所列均為A線到B線電位差)所示。

表1 ΓОСТ 18977信號的電平標準

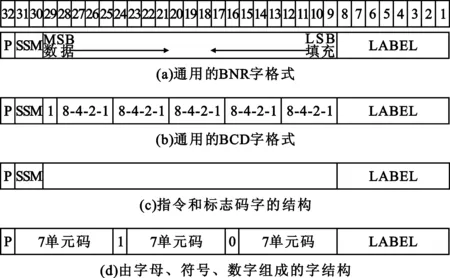

根據ΓОСТ18977和PTM1495的規定,采用二進制碼作為所有系統間、全套設備間通信的統一語言。而它同時又規定了通信中可以采用二進制碼、二-十進制碼(BCD)、指令和標志碼,以及由字母、符號、數字組成的字符碼等4種數據的格式。這4種數據的通信都要按照ΓОСТ18977規定的32位串行數據的方式來發送和接收,具體在32位的字中格式定義如圖1所示。

圖1 ΓОСТ18977傳輸字格式

3 系統硬件設計

3.1 硬件整體設計

目前國內外已有產品的接口電路均僅支持一種接口用途。這樣做的缺點是當需要更換為另一種主機總線接口時,不但要更改FPGA內的程序,還需重新設計接口電路,導致開發時間延長、經費增加。此外,國內的工控機普遍采用的是CPCI或PXI插槽,普通的臺式機電腦則采用PCI和USB接口,而在沒有PCI和PXI等插槽的筆記本電腦上均具有USB接口。因此,本系統采用主子板結合的方式同時實現USB、CPCI和PXI 3種接口用途的接口電路,可使該接口卡滿足當前各種主機的接口要求。

鑒于上述原因,本系統采用FPGA、USB、CPCI及PXI技術,依據ΓОСТ18977航空總線規范,設計并開發一種兼容3種接口的多通道總線接口板,可以滿足當前各種主機的接口要求,節省大量經費。并設計了采用雙口RAM IDT70V658S[2]作為FPGA和接口控制器件之間的共享存儲器,通過它來協調FPGA和各個接口控制器件之間傳輸的信息,從而實現系統多接口用途的設計。

本系統的硬件設計在結構上采用主子板的方式,主板主要由FPGA、雙口RAM和電平轉換3部分組成,子板主要由接口控制芯片和總線接口組成,具體分為USB接口子板、CPCI接口子板以及PXI接口子板3個子板。主板和子板間通過連接電纜相連,用戶需要什么接口便可選擇相應的接口子板與主板相連。系統總體結構如圖2所示。

圖2 系統結構圖

3.2 主板設計

主板主要由FPGA、DPRAM和電平轉換3部分組成,其功能主要是實現ΓОСТ18977航空總線協議。其功能分為兩部分:一是接收經過轉換成數字信號的符合ΓОСТ18977航空總線的數據并將其送入雙口RAM;二是將雙口RAM中暫存的數字信號按照ΓОСТ18977航空總線協議的數據格式輸出。

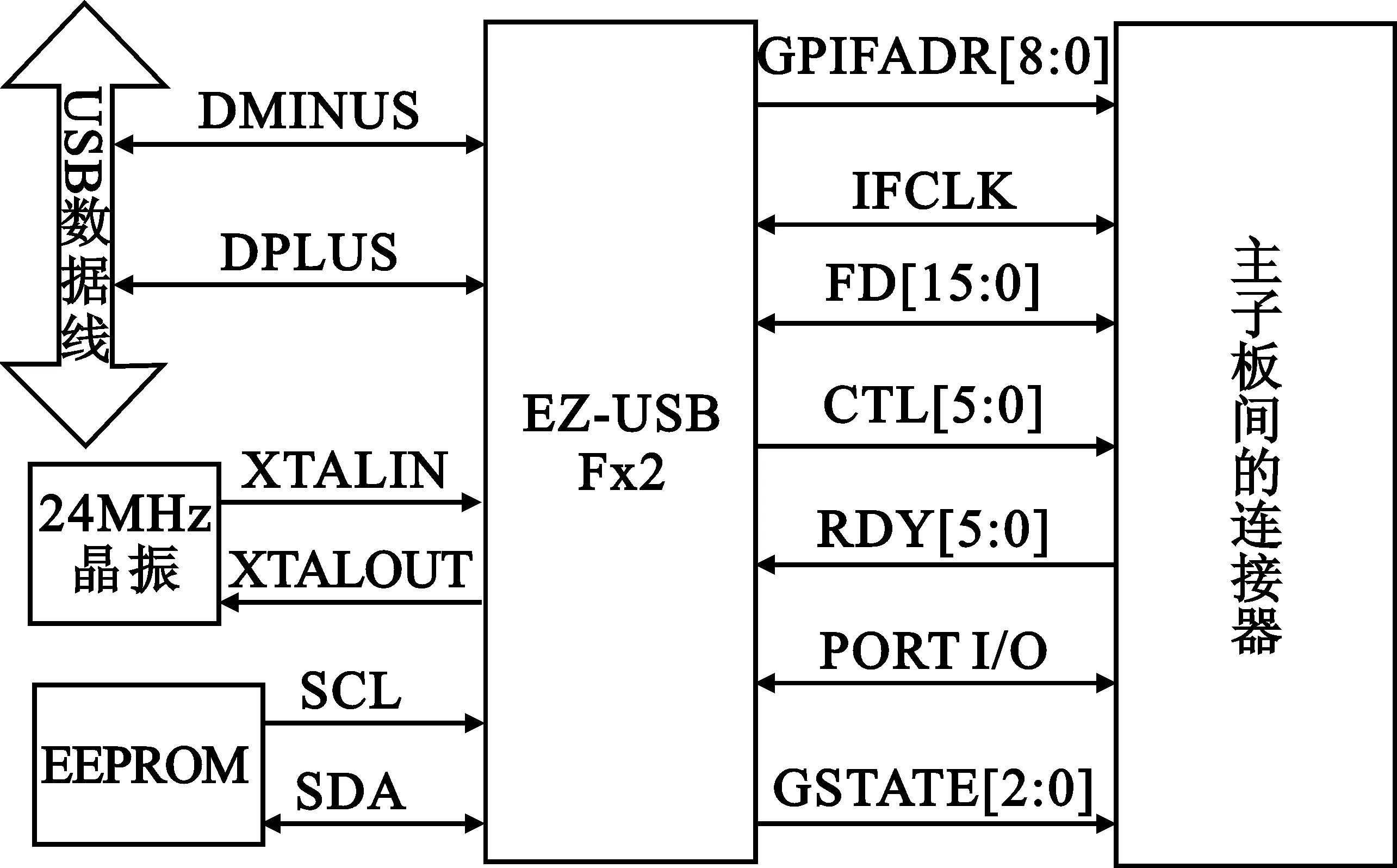

3.3 USB子板總體設計

圖3 USB接口子板結構圖

3.4 CPCI子板總體設計

CPCI接口子板主要由PCI控制器件PCI9054[3]和熱插拔控制器件LTC1644[4]組成。PCI9054主要用來處理CPCI接口的PCI特性,它將復雜的PCI總線的數據傳輸邏輯轉化為簡單的本地控制邏輯;LTC1644則主要用來處理CPCI接口的熱插拔特性。

CPCI接口子板的功能主要分為兩部分:一是將主機的CPCI信號轉換成并行信號傳給雙口RAM;二是將雙口RAM中暫存的并行信號轉換成串行信號通過CPCI接口傳給主機。CPCI接口子板結構如圖4所示。

圖4 CPCI接口子板結構圖

3.5 PXI子板總體設計

PXI接口子板主要由PCI控制器件PCI9054[3]、熱插拔控制器件LTC1644[4]和FPGA[5]組成。其功能主要分為兩部分:一是將主機的PXI信號轉換成并行信號傳給雙口RAM;二是將雙口RAM中暫存的并行信號轉換成串行信號通過PXI接口傳給主機。PXI接口子板結構如圖5所示[6-7]。

4 多接口用途的設計與實現

本接口卡支持3種接口用途,各個接口傳輸的數據字格式、控制信號等均有差異,所以采用了雙口RAM IDT70V658S[2]作為FPGA和接口控制器件之間的共享存儲器,通過它來協調FPGA和各個接口控制器件之間傳輸的信息,從而實現系統多接口用途的設計。另外,各個接口總線和ΓОСТ18977航空總線標準傳輸速率相差很大,采用雙口RAM可以很好地解決兩者之間讀寫速度問題。

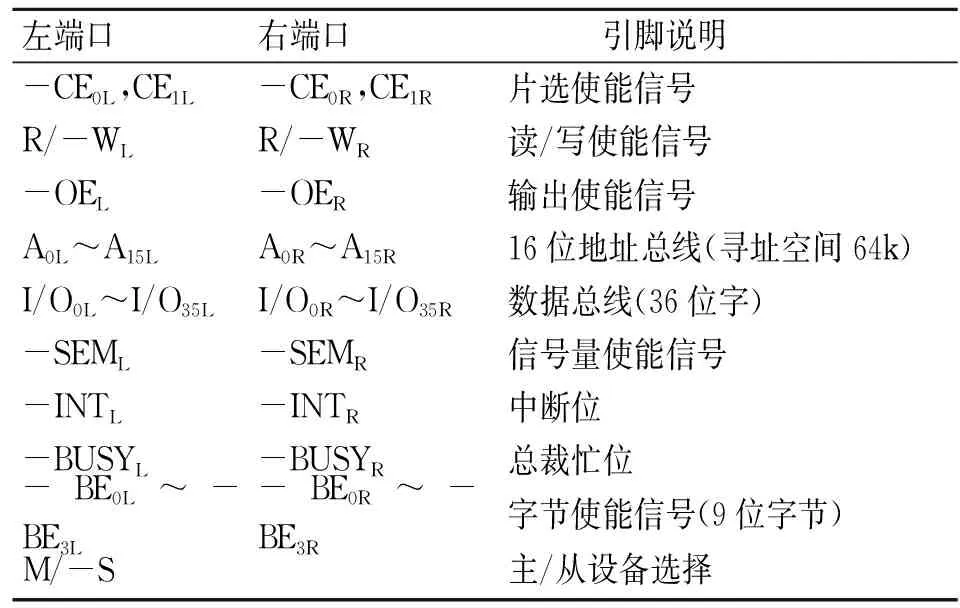

4.1 雙口RAM主要引腳設計

雙口RAM的存儲器端口一邊由各子板上的控制器件通過連接電纜來使用,另一邊由主板上實現ΓОСТ18977航空總線協議的FPGA器件來使用。存儲器的主要用途是保存ΓОСТ18977數據字,由于本系統可用于多種接口用途,存儲器訪問單元可根據需要選擇8位、16位或32位字,具體是通過控制信號-BE0L~-BE3L進行選擇。IDT70V658S共有36根數據總線,而ΓОСТ18977數據字為32位,所以設計時將IDT70V658S左端口的I/O8L、I/O17L、I/O25L、I/O35L數據線不連,呈高阻態。32位數據字從高到低依次為I/O34L~I/O26L、I/O24L~I/O18L、I/O16L~I/O9L、I/O7L~I/O0L。右端口的數據線連接與左端口相同。IDT70V658S主要引腳說明如表2所示。

表2 IDT70V658S主要引腳說明

使用雙口RAM時,若兩端同時對同一地址單元執行寫操作或者一讀一寫操作,就會發生沖突,造成寫錯誤或者讀錯誤,即爭用問題。該設計中選擇使用雙口RAM的硬件判優方式來解決這個問題。這樣,當存儲器兩端同時對同一地址單元訪問時,只有一方可以進行有效訪問,而另一端的訪問為不確定。所以存儲器使用-BUSY信號表示雙方訪問的有效性(-BUSY=0有效,-BUSY=1無效),即-BUSY有效的一方表示訪問不確定,不確定方訪問操作需要重復。在連線存儲器時,把存儲器左右端口的-BUSY都引入FPGA中。可以使用FPGA硬件邏輯對-BUSY進行判斷,使訪問無效一方重新訪問存儲器[2]。

4.2 雙口RAM存儲單元的劃分及數據緩沖區的維護

根據研制的需要,將雙口RAM分為發送、接收兩部分。結合對雙口RAM可以同時讀寫的特點,又將發送、接收RAM地址區各劃分為8部分,分別對應8個發送、接收通道。雙口RAM的分配見文獻[8-9]。

每個發送緩沖區的前5個單元用來存儲發送控制字、SPOS指針、RPOS指針,每個接收的前7個單元用來存儲發送控制字、LABEL標志、SPOS指針、RPOS指針。存儲發送命令或接收命令的單元均只用最后8位,這是由本設計中雙口RAM的最小訪問單元為8位所決定的。

將翻轉課堂應用到“射頻識別原理與應用”課程教學中,可以解決當前該課程教學中存在的問題,引導學生自主學習,促進師生之間的交流,提高學生的深度學習能力。目前,基于翻轉課堂的“射頻識別原理與應用”課程教學設計已經完成,還需建立一個“射頻識別原理與應用”課程的在線學習平臺或APP,將教學資源分類細化列出,學生可以通過這個平臺進行學習交流,老師在教學過程中可以不斷地去補充和完善教學資源和設計,并通過這個平臺針對學生的學習記錄和學習互動情況進行評價考核。

發送控制字位寬為8位;接收控制字位寬為16位;LABEL為8位標志數據;SPOS和RPOS為每個緩存區的兩個指針,每個指針大小為16位,用來控制讀寫,指針SPOS指向緩沖區中當前第一個空閑存儲單元,指針RPOS指向緩沖區中當前第一個保存有效數據的存儲單元。

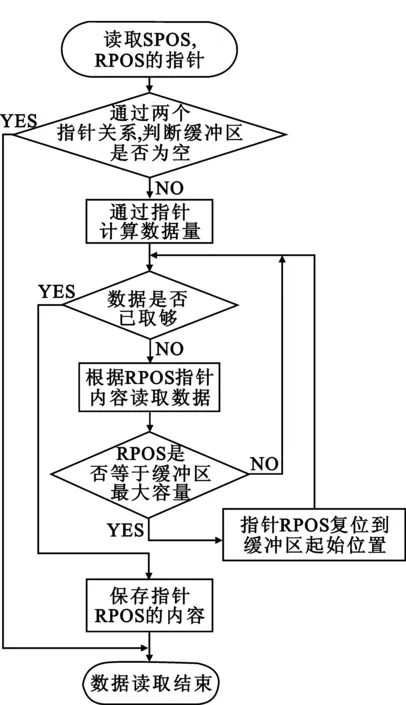

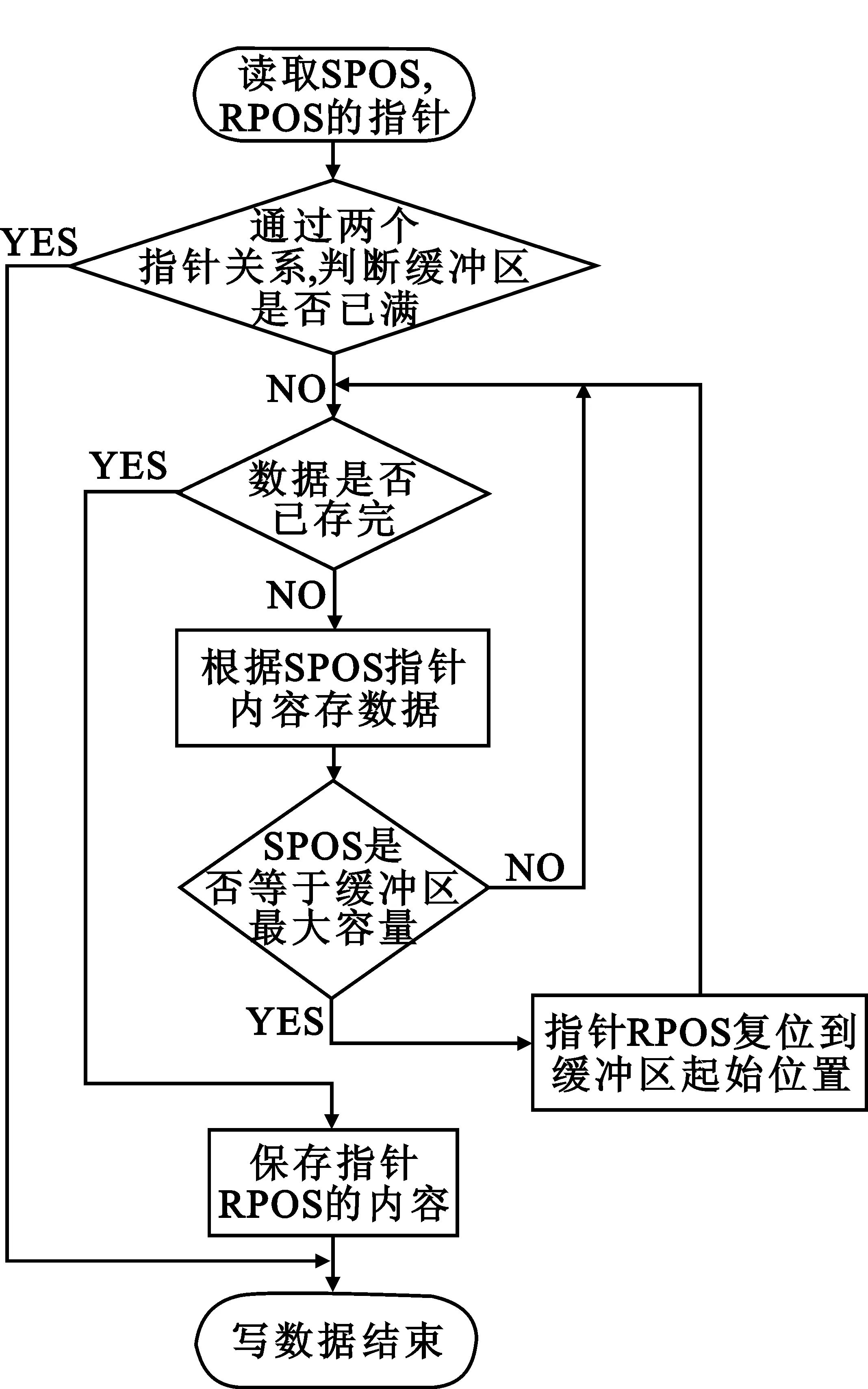

雙口RAM緩沖區的讀寫數據流程如圖6所示。

(a)讀數據流程

(b)寫數據流程

數據的保存采用循環緩沖區結構。雙口RAM的兩端通過讀取SPOS和RPOS兩個指針變量來判斷當前緩沖區的狀態是空還是滿。本系統規定緩沖區滿時存儲數據的容量為Δ-1,其中Δ為緩沖區最大容量。

在對緩沖區進行讀寫操作后,應用程序要判斷兩個指針內容。當兩個指針所指地址到達緩沖區終端時,應用程序把這兩個指針復位到緩沖區的起始地址,這樣即實現了循環緩沖區的存取。循環緩沖區結構見文獻[10]。

當讀數據一方進入緩沖區后,先讀取SPOS和RPOS指針變量,然后判斷當前緩沖區是否為空。如果緩沖區非空,則根據RPOS指針把數據取出。每取出一個數據后,應用程序要判斷RPOS指針是否已到達緩沖區終端,如果RPOS到達緩沖區終端,則復位該指針指向該緩沖區的起始地址。最后讀數據一方要把RPOS指針值更新到固定內存單元中。

當寫數據一方進入緩沖區后,先讀取SPOS和RPOS指針變量,然后判斷當前緩沖區是否已滿。如果緩沖區仍有空閑單元,則根據SPOS指針把數據存入存儲器中。每保存一個數據后,應用程序要判斷SPOS指針是否己到達緩沖區終端,如果SPOS指針到達緩沖區終端,則復位該指針指向該緩沖區的起始地址。最后寫數據一方要把SPOS指針值更新到固定的內存單元中。

5 結 論

本接口板具有USB、CPCI和PXI多接口的設計,使得該接口板具有很好的通用性和兼容性。經測試表明,采用雙口RAM作為FPGA和接口控制器件之間的共享存儲器,可以很好地協調FPGA和各個接口控制器件之間傳輸的信息,從而實現系統多接口用途的設計。另外,各個接口總線和ΓОСТ18977航空總線標準傳輸速率相差很大,采用雙口RAM也可以很好地解決兩者之間讀寫速度的問題。

參考文獻:

[1] 王勇,于宏坤.機載計算機系統[M].北京:國防工業出版社,2008.

WANG Yong,YU Hong-kun.Airborne Computer System[M].Beijing:National Defense Industry Press,2008.(in Chinese)

[2] Integrated Device Technology,Inc. High-speed 3.3V 128/64/32K 36 Asynchronous Dual-Port Static RAM[M].CA,USA:Integrated Device Technology,Inc.,2005.

[3] PLX Technology,Inc.PCI 9054 Data Book V2.1[M].CA,USA:PLX Technology,Inc.,2000.

[4] Linear Technology Corporation.LTC1644 Data Sheet[M].CA,USA:Linear Technology Corporation,2001.

[5] Altera Corporation.Cyclone-device-handbook[M].CA,USA:Altera Corporation,2008.

[6] 何光亞.基于PXI總線的QPSK解調模塊設計[D].成都:電子科技大學,2007.

HE Guang-ya.The design of a PXI bus-based QPSK demodulation module[D].Chengdu:University of Electronic Science and Technology of China,2007.(in Chinese)

[7] 聶玉慶.基于PXI總線的QPSK解調器設計實現[D].成都:電子科技大學,2007.

NIE Yu-qing. The design and realization of QPSK modulator based on PXI bus[D]. Chengdu:University of Electronic Science and Technology of China,2007.(in Chinese)

[8] 蔣謝芳.基于嵌入式微處理機和Compact PCI的ARINC429總線接口板的設計[D].西安:西北工業大學,2006.

JIANG Xie-fang. The design of ARINC 429 bus interface card based on the embedded microprocessor and Compact PCI[D]. Xi′an: Northwestern Polytechnical University, 2006. (in Chinese)

[9] 賓辰忠.基于MCF5206的ARINC429通信板卡的設計與實現[D].西安:西北工業大學,2005.

BIN Chen-zhong. The design and realization of ARINC 429 communication card based on MCF5206[D]. Xi′an: Northwestern Polytechnical University, 2005. (in Chinese)

[10] 嚴蔚敏,吳偉民.數據結構[M].北京:清華大學出版社,2004.

YAN Wei-min, WU Wei-min. Data Structure[M].Beijing: Tsinghua University Press, 2004. (in Chinese)