一種SoC片上調試與可測性的整合設計

虞致國,魏敬和

(中國電子科技集團公司第五十八研究所,江蘇 無錫 214035)

1 引言

在開發復雜SoC應用時,芯片的調試手段直接關系到開發的效率和進度,決定了應用的質量。沒有調試硬件支持的調試已經不能勝任復雜SoC的應用,SoC必須提供高效、可靠、強大的調試支持[1~3]。另一方面,測試是集成電路生產流程中必不可少的一個環節,在設計時一般要采用可測性設計。

然而,可測性設計與調試結構設計一般是分別進行的。由于測試邏輯和調試邏輯都具有相當的邏輯量,約占系統邏輯的5%~25%[4]。因此,所需額外硬件資源都較大。目前,芯片的調試接口一般是基于JTAG標準而設計的。基于JTAG的可測性設計與片上調試設計相互獨立又相互聯系,二者可通過JTAG接口進行部分整合[5]。

本文基于已有的SoC提出了一種片上調試與可測性設計的一體化設計,有效整合了調試與可測性的接口。它既具有完整的片上調試能力,又能滿足可測性要求,提供了SRAM內建自測試和邊界掃描測試的能力。

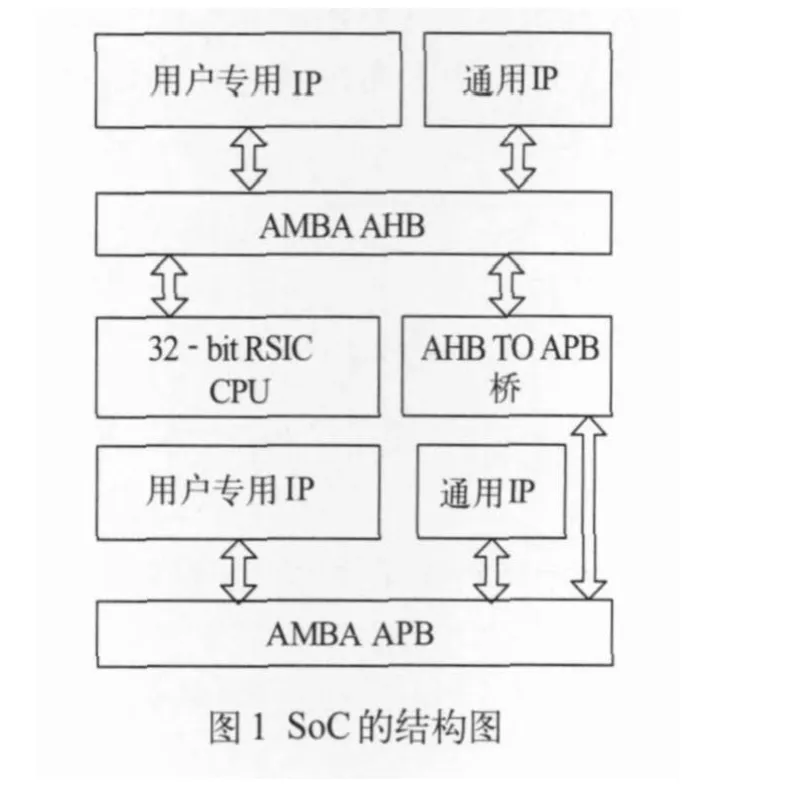

2 32-bit SoC的結構

該款SoC結構可以簡單的用圖1所示的結構表示,主要包括CPU核、SRAM、通用接口IP和用戶專用IP。SoC片上總線采用AMBA總線(包括AHB總線和APB總線),CPU為32位硬核,具備從JTAG接口進行片上調試的能力,能夠實現單步、斷點、觀察點等調試特征。

3 SoC片上調試與可測性的一體化設計

3.1 總體設計

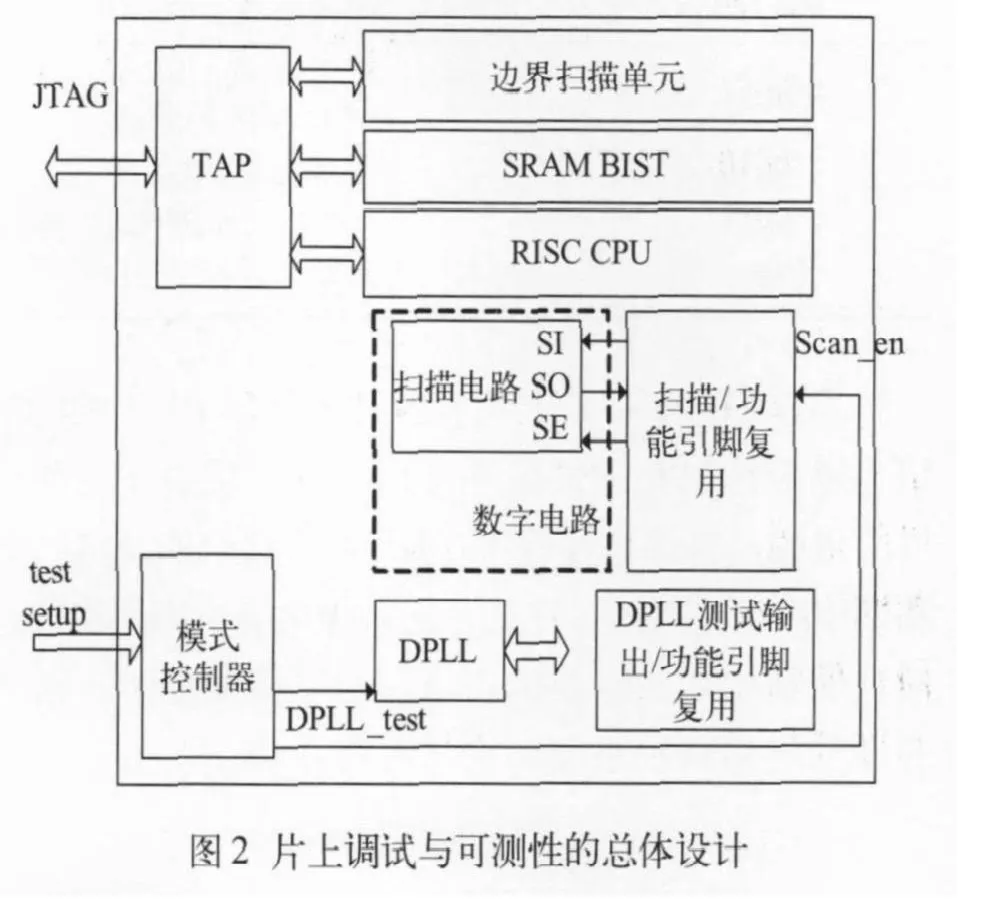

調試系統的設計目標是充分利用CPU核原有的調試結構,并通過JTAG進行有效的調試。可測性的設計目標是在利用較低的測試時間和較小的測試面積實現較高的測試覆蓋率和故障覆蓋率。因此,總體的設計思路是盡可能地利用JTAG復用相關調試與測試入口,并針對不同的模塊利用不同的測試策略。針對測試來說,通過JTAG接口可以集成邊界掃描測試、存儲器內建自測試等。測試策略實現了在測試覆蓋率和測試代價之間的一個有效折衷。測試代價包括芯片面積、芯片引腳數、功耗和芯片工作頻率、測試時間長度等。總體的設計結構如圖2所示。主要的設計思路如下:

(1)構建了一個芯片級別的調試與測試模式控制器;

(2)基于JTAG集成了邊界掃描測試(BSD)、存儲器內建自測試(SRAM BIST)和CPU片上調試等接口;

(3)對數字IP和用戶自定義邏輯采用掃描測試;

(4)復用第三方提供的CPU測試向量;

(5)對于嵌入式SRAM實現內建自測試;

(6)對于DPLL實現功能測試。

3.2 調試與測試模式控制器

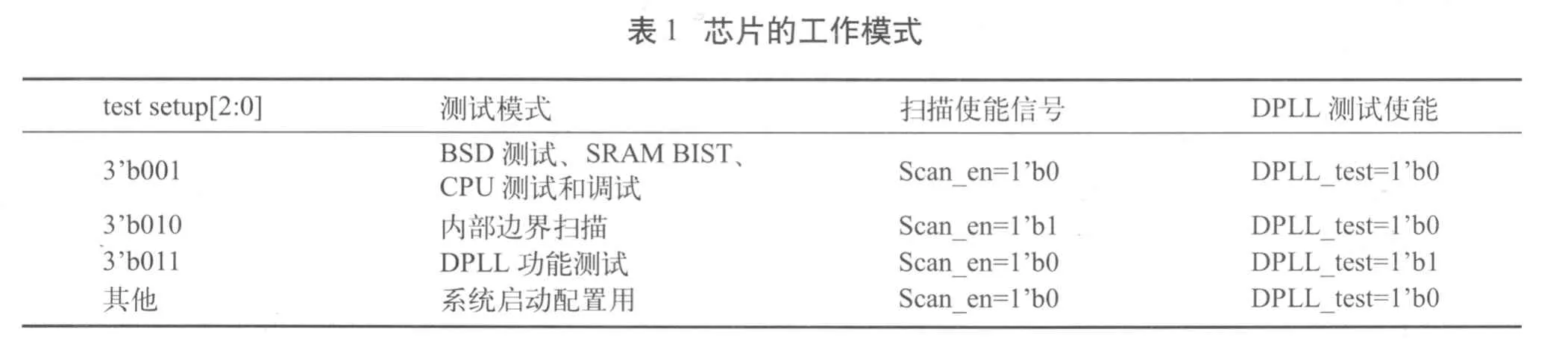

除了正常的工作模式外,SoC還有完備的調試與測試模式。芯片的模式控制由引腳testsetup[2:0]所控制。測試模式的描述見表1所示。

芯片內部有多個時鐘域,主要包括TCK、內部系統時鐘、掃描時鐘。調試模式使用的是邊界掃描時鐘TCK;正常工作模式使用的是經鎖相環倍頻的時鐘,其他掃描模式使用的是系統外部時鐘。

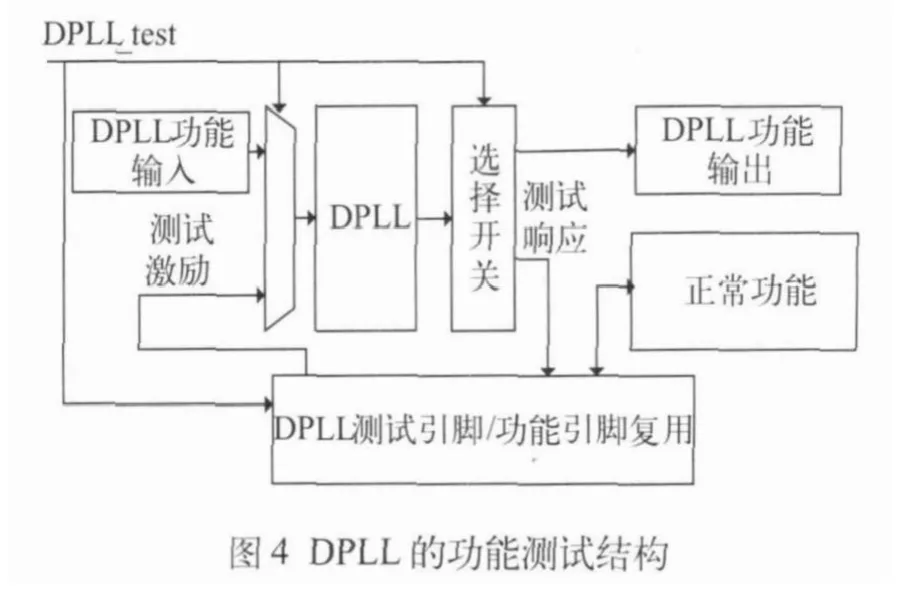

在掃描鏈的插入過程中,為了避免因可測性設計帶來引腳的大量增加,采用了測試引腳和功能引腳復用的結構。為了能有效在工作模式與測試模式間進行切換,增加了掃描使能信號scan_en。當處于測試模式時,scan_en有效,引腳處于掃描模式。為了在對DPLL功能測試時能輸出相關狀態,增加了DPLL測試輸出使能信號DPLL_test。

3.3 SRAM BIST

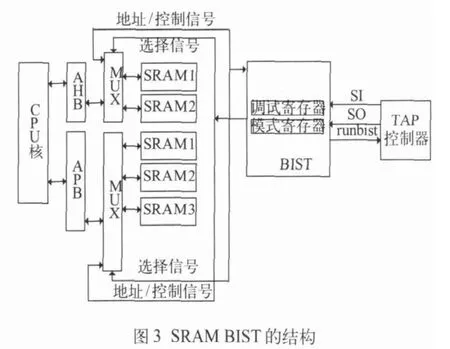

對于高密度嵌入式SRAM來說,BIST是一種有效的測試方法,它能夠全速實現高覆蓋率的測試。SRAM BIST電路是由EDA工具自動生成的。

在設計的某SoC設計中,有多片SRAM,分別在ABH總線和APB總線上。SoC中采用的SRAM BIST的結構如圖3所示。CPU核和BIST電路通過MUX開關與SRAM相連。在正常工作模式下,CPU核可以通過AHB或APB來訪問SRAM。在測試模式下,SRAM的選擇信號、地址、數據及控制信號由SRAM BIST電路根據MBIST算法產生。MBIST算法包括March LR、March C-、MATS++ and Retention等,算法由模式寄存器的值來選擇。

通過JTAG的TAP控制器對SRAM BIST的測試信號進行控制和測試結果進行查詢,擺脫了對測試機的依賴。自測試過程中,BIST將獲得的測試結果和期望的結果將進行比較,比較結果pass/fail將被返回存儲到模式寄存器中。當一個錯誤發生時,錯誤的詳細信息將被跟蹤到調試寄存器中。

3.4 DPLL功能測試

DPLL是一個全定制宏模塊。DPLL功能測試結構如圖4所示。當外部信號DPLL_test置于1時,SoC進入DPLL功能測試模式。功能測試模式時,測試引腳輸入/輸出來自于外部引腳。

4 實現與結果

該SoC采用SMIC 0.18μm 1P6M邏輯電路工藝。芯片總共有管腳391個,包括PAD在內,芯片的面積為7.76mm×7.76mm,測試面積占芯片面積的6.89%。芯片的設計結果如下:

(1)總共有10條內部掃描鏈,每條掃描鏈的長度約為3000;

(2)數字IP和用戶自定義邏輯的覆蓋率是97.2%;

(3)SRAM的測試覆蓋率為100%;

(4)CPU核和DPLL采用功能測試的方法;

(5)全芯片的測試面積占芯片面積的6.89%。

5 結論

片上調試與可測性設計是嵌入式系統和SoC設計中的重要環節。本文提出了一種可測性設計與調試系統一體化的結構設計策略,其重點在于將現有的測試方法與系統的調試結構整合到一個結構中。被整合的測試方法包括掃描鏈插入、SRAM BIST、功能測試等,同時有效地降低了測試邏輯規模。本文提出的結構對其他SoC設計具有一定的參考價值。

[1]趙巖,張果,張春,等.一種擴展的片上實時調試系統設計[J].計算機工程,2006,32(8):283-285.

[2]金輝,華斯亮,張鐵軍,等.基于JTAG標準的處理器片上調試的分析與實現[J].微電子學與計算機,2007,24(6):116-121.

[3]成杏梅,劉鵬,鐘耿.嵌入式MPSoC的調試功能實現[J].計算機輔助設計與圖形學學報,2008,20(4):438-444.

[4]李少青,鄧勤學.故障測試結構與調試結構的一體化設計[J].計算機工程與科學,2006,28(8):99-100.

[5]嚴明.嵌入式微處理器可測性設計與片上調試技術的研究與實現[D].碩士論文,國防科學技術大學,2005,11.

[6]劉洋、吳王華,周曉方.一種基于JTAG的軟硬件協同SoC調試接口[J].微電子學與計算機,2007,24(11):34-37.

[7]IEEE Standard Test Access Port and Boundary Scan Architecture. IEEE Std 1149.1-2001(Revision of IEEEStd 1149.1-1990).