確好芯片商業化的關鍵問題

龍 樂

(龍泉天生路205號1棟208室、成都 610100)

1 引言

確好芯片KGD(Known Good Dip)是各種各樣的多芯片組件MCM、多芯片封裝MCP、系統封裝SiP或SoP、微系統封裝MSP、疊層封裝SCP、堆疊封裝PoP、3D堆疊封裝、微波功率組件MPM、混合集成電路HIC封裝、版上芯片COB、可更換芯片組件RCM、功率模塊、分立器件復合化(陣列化)的基礎和先導。以MCM為例,其中單純的芯片成本就占總成本的50%以上,有的甚至達到70%~80%,芯片品種多而雜,KGD成為組件及多芯片封裝技術的必要條件。隨著微電子技術和專用設備的發展,芯片制造加工工藝的成熟以及生產線工藝和質量控制能力的增強,半導體器件的失效總體表現為芯片本身失效減少,這進一步推動KGD技術迅猛發展,對各類KGD的推廣應用推波助瀾,利用未封裝KGD每年封測生產數十億塊集成電路及其他類別半導體器件產品,其市場可達到數千億美元,KGD商業化的問題值得關注。

2 KGD的概念及分類問題

多芯片組件、多芯片封裝、功率組件、系統封裝等產品需采用多種或一些不同的裸芯片復合組裝在同一封裝結構中構成產品,未封裝的裸芯片相對于封裝的器件也有其單獨的優勢:可極大程度地減少器件和模塊的體積;減少了芯片封裝所帶來的引線電阻;在組件及封裝或電路的設計時,具有更大、更多的靈活性與自由度。

目前,行業缺少科學統一的KGD概念,導致出現不同的術語定義,例如:KGD是指裸芯片成功通過和其封裝芯片一樣的電測試與可靠性檢驗試驗;理想KGD具有很高的封裝成品率,其可靠性高,芯片無缺陷,并經過裝配、老化、環境應力篩選等試驗仍無失效;KGD是指有著與封裝產品相同質量和可靠性的裸芯片,即采用KGD技術可對裸芯片進行常溫、高溫、低溫測試和高溫老化篩選等試驗,經功能和參數測試來剔除有早期失效或有缺陷的芯片;也有廠家將KGD定義為已知良好芯片或完好芯片、被確認的優質芯片、信得過芯片、足夠好芯片、測試好芯片、合格芯片,在KGD概念上“和而不同”,滿足客戶采購芯片和研發組件、整機要求。

政府部門、產業界、芯片制造廠商組成聯盟,推進KGD技術及產品開發,KGD一般分為如下四類,向客戶提供KGD產品或為裸芯片提供KGD篩選服務,確保進入半導體后工序芯片的質量滿足封測廠商要求。

(1)工藝方法類

KGD高成品率通過6 σ管理、圓片級篩選或特殊工藝的改進,這一方法只適用于半導體制造商和控制定制IC芯片設計公司。

(2)設計方法類

包括在芯片周邊內建自測試、邊界掃描等可測試性設計,在專門預測試的IC上耗費多余焊盤等,通過預測試對芯片分類。

(3)統計抽樣類

將足夠數量統計的芯片封裝到單芯片內,并充分測試以證實整個批次,從而對芯片批次進行分類。該方法需要耗費數百個測試樣品以保證0.99級KGD,上千個樣品保證0.999級KGD。

(4)測試每塊芯片類

通過圓片探針、芯片測試插座、適應各種封裝形式(BGA、CBGA、FBGA、PLCC、QFN、SOP、DIP等)測試和老化插座/載體/夾具系統以及TAB(載帶自動焊技術)、微芯片載盒或其他方法對所有芯片進行檢驗試驗、測試而分類芯片。開發出數十種不同的測試方法,可歸納為壓力接觸和金屬連接兩大類,保證KGD質量和可靠性。

KGD產品供應商根據不同客戶的質量要求,可提供多個質量等級的KGD,所進行的檢驗試驗項目和規定也不同,分別按有關技術標準進行篩選或補充篩選、二次篩選。

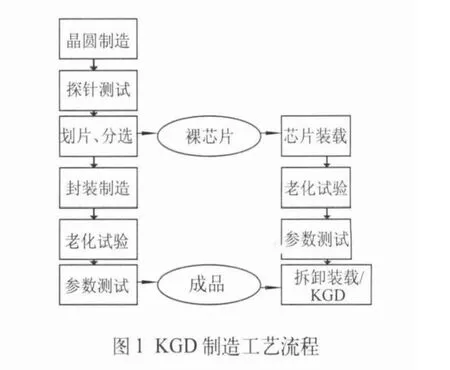

3 KGD工藝流程問題

成熟的生產工藝技術是保證KGD質量的重要有效途徑。產品質量不能只靠檢驗試驗獲取,擁有高素養的人才、先進的生產設備、高水平穩定的工藝、嚴格的質量管理與控制,才能制造出滿足要求的KGD產品。

芯片在切割劃片后呈未封裝狀態時,難以全面老化測試,及時篩選剔除早期失效或有缺陷芯片。KGD工藝流程即從劃片后開始,如圖1所示,經裝載、老化、可靠性預應力、功能和參數的全面電測試、拆卸裝載、包裝標示、貯存運輸等流程,KGD達到封裝成品的質量與可靠性要求,其中KGD夾具和裝/卸載、測試與老化篩選技術是關鍵。一些公司開發了三大類測試夾具:永久性夾具、半永久性夾具和臨時性夾具,期望隨用量增加而降低成本。

夾具為襯底提供一個機械支撐,既可以保護裸芯片免遭機械損傷,又為測試和老化的插座提供了一個機械界面。建立電連接到裸芯片上進行測試和老化的一個夾具和裝/卸載系統,需要滿足這樣一些要求:在整個測試、老化的全溫度范圍具有穩定的連接;每個連接處的低電阻和低阻抗;能夠連接到芯片上所有的輸入/輸出;對于干擾后裝/卸載的芯片不會造成損壞;為電源和接地連接提供足夠的電流能力;無大的性能障礙(串擾、反射、衰減);連接方法需要與出現在待測試不同芯片的輸入/輸出焊盤各種不同的金屬化兼容。

3.1 芯片載體壓力接觸

采用各種各樣接觸界面的微型探針、芯片插座/載體或臨時性載盒,包括施加壓力(或依賴于壓力)的金屬合金凸點、薄膜觸點、導電膜或導電膠等方法。歐美日多家公司推動KGD芯片載體壓力接觸測試、老化插座/載體及數種獨特壓力接觸探針卡技術發展,研發出倒裝焊探針、膜探針、枝狀晶體倒裝焊探針、TAB引線探針、鍍探針、硅膜探針、導電膠探針、導電板探針、載體插座等方法。一般而言,臨時性夾具通常采用探針接觸是壓力接觸,尤其是解決功率裸芯片的散熱和電極連接問題。例如,裸芯片可倒扣在內裝薄膜導電布線基板(襯底)上,芯片上的壓焊區與襯底上的金屬凸點接觸,芯片上方的蓋板帶有彈簧裝置,通過彈力蓋板對芯片形成一個可控制的壓力,以形成芯片電極與襯底的金屬凸點的適當接觸,實現良好的電連接。把安裝有裸芯片的夾具系統裝到測試插座及其封裝載體內,即可以進行芯片老化和全溫度范圍的電性能測試。

3.2 芯片載體金屬連接

一般而言,金屬連接的電阻值更低,穩定性更好,多應用于半永久或永久性夾具,KGD方法中使用三種類型金屬連接:在兩個(熱壓、超聲、熱聲絲焊和TAB)之間,當兩個連接部分通過相互擴散原子連接在一起時,形成焊接接點;以一個低熔點金屬將兩個連接部分濕潤并鍵合,形成熔接的接點;當原子被沉積到IC焊盤上形成連接軌跡時,形成電鍍/沉積的接點。金屬連接也可以是臨時性封裝載體,為KGD篩選而做在一起的,在測試之后拆卸下來恢復原來的裸芯片結構,進入裝配封測業。

4 KGD的老化篩選問題

在GB/T4589.1-2006中,老化的定義為規定時間內對批中所有器件施加熱應力和電應力,以檢出并剔除潛在的早期失效器件;篩選是對一批中所有器件進行的檢驗或試驗。KGD篩選通常進行特性參數電測試、檢查篩選、壽命篩選、環境應力篩選以及其他機械和環境試驗,承制單位按有關技術標準和訂貨合同為依據進行篩選,例如:環境應力篩選包括振動加速度、離心加速度、溫度循環和熱沖擊等;壽命篩選中包括高低溫貯存、電功率老化、高溫壽命、電耐久性試驗等;特性參數電測試法篩選是最常用的手段,包括直流和交流參數測試、功能測試、熱阻測試、熱敏參數快速篩選等。裸芯片是未封裝的器件,老化篩選可以參照封裝器件試驗方法和程序進行,在KGD的老化篩選上,現沒有統一成熟或系統化的方法,一般按用途和客戶需要選擇篩選方法,視具體情況和對可靠性要求而確定。

尤其是功率KGD值得關注,要通過綜合分析,結合實際需求,采用合適的測試和老化篩選方法。其原因為功率裸芯片是未經封裝的功率器件,一些篩選功率管的方法并不完全適合功率KGD。例如:在規定條件下測量晶體管的熱阻,保證芯片良好的沾附完整性,特別適合完整封裝的器件,同時通過試驗,為改進器件內部各種結構材料的熱匹配設計以及管殼散熱性能,盡量降低器件熱阻和峰值結溫,提高器件工作壽命提供依據,因此熱阻測試篩選法不能被功率KGD選用;篩選與測試功率裸芯片要受到大電流與高溫度的制約,裸芯片本身不能提供散熱的途徑,夾具導熱散熱能力不強,因此,電功率老化法不能直接被應用于功率KGD老化篩選,而需要采取控制芯片結溫的附加措施。采用其他的KGD篩選方法時,也需要考慮未封裝裸芯片的實際具體問題,以達到測試和老化篩選目的。

4.1 熱敏參數快速篩選法

快速篩選方法就是通過短時間(數秒)內對晶體管施加超額定功率,使其結溫迅速接近或達到最高結溫,再快速檢測熱敏參數:HFE、ICEO等加功率前后的變化量,并根據有關熱敏參數失效判據來對晶體管進行快速篩選。這種快速篩選試驗方法適用于剔除易產生早期失效的器件,改善產品批的質量和可靠性,以熱敏參數的變化量或變化率預測被試管的熱穩定性,考核被試管承受沖擊的能力,估計被試管熱阻大小和范圍,可作為功率KGD測試與篩選中一種輔助篩選方法。其不足是以參數變化量的大小作為判據的,確定失效判據需要統計分析大量的實驗數據;另外,無法暴露如電遷移、氧化層缺陷、電化學腐蝕等與時間有關的失效機理。

4.2 結溫控制功率老化篩選法

工信部電子五所率先從2001年進行KGD技術國內研發,現完成了KGD臨時封裝載體的開發制作,建立KGD質量與可靠性保證試驗線,并能對低頻信號、單面的電極常規裸芯片進行測試和老化篩選,在功率裸芯片的測試與老化篩選上,采用結溫控制功率老化篩選法,既解決功率裸芯片篩選時存在的高溫、大電流問題,又不降低施加電功率條件,達到剔除有隱患或那些有制造缺陷隱患的器件。

結溫控制功率老化篩選法通過紅外熱像儀測量晶體管結溫分布和最高結溫,經計算處理后建立功率-結溫的定量關系,參照最高結溫175℃,通過降低老化環境溫度或降低工作電流(功率),控制結溫老化裸芯片,擬定出合適的直流功率篩選條件。另外,采取加脈沖功率,結溫值可通過測量敏感參數(如Δ Vbe)的值來確定,在短時間內加熱,然后調整冷卻或散熱條件,待結溫下降到一定程度時,再繼續施加電功率,以達到持續老化的目的。

功率老化與穩態工作壽命試驗的目的是檢測器件是否存在表面沾污、界面狀態不穩定、燒結不良等缺陷隱患。為了能有效地檢測出存在缺陷隱患的產品,功率老化和穩態工作壽命試驗時,應使器件達到GJB128A-97中規定的最高結溫175℃。試驗時,在相同的功率下,其電壓與電流的組合可以有多種選擇,中小功率以電壓應力為主,大功率以電流應力為主。器件的失效與時間和應力有關,是在施加電應力的作用下使器件的缺陷提前暴露的最可靠、最常用的方法,通過電功率老化篩選能暴露出器件的大部分缺陷,若未經老化,這些器件在正常使用條件下會早期失效。

4.3 高溫電壓反偏應力篩選法

在高溫反偏老化中,裸芯片被同時加上高溫環境應力和反向偏壓電應力,其內部無電流或只有微小的電流通過,消耗的電功率很少,產生的熱量也相應較少,有利于散熱條件要求苛刻的功率裸芯片,對剔除具有表面效應缺陷的早期失效裸芯片特別有效。芯片制作過程中易受到某些有害堿金屬離子的沾污,這些堿金屬離子會使器件的電參數在使用時產生嚴重漂移失效,高溫應力的作用是激發芯片界面上的有害離子如Na+,提高Na+的運動速度;反偏應力的作用是強迫已加速的Na+沿反偏電場方向做定向運動,通過檢測老化后器件的反向漏電流和擊穿電壓,鑒別和剔除表面有缺陷的器件,減少老化時間,降低成本。

4.4 溫度循環和熱沖擊

溫度循環(空氣-空氣)或高低溫沖擊以及熱沖擊在半導體器件的測試與篩選中是必用方法,通過在劇烈的高低交變環境條件下,產生熱脹冷縮的效應,以考查芯片中各種不同材料之間的熱匹配能力,溫度循環確定器件耐極限高溫和低溫的能力及交替暴露到這種極限溫度下的影響,熱沖擊確定器件耐受突然暴露到極端變化的溫度中的能力及交替暴露到這種極限溫度下的影響,可以篩選出具有微裂紋、氧化層臺階的金屬化缺陷和襯底表面等缺陷的器件。

4.5 高溫貯存

高溫貯存是一種加速性質的高溫壽命(非工作狀態)篩選試驗,對器件施加溫度應力,加速失效過程,對表面沾污、鍵合不良、氧化層缺陷和表面漏電等缺陷有較好的剔除作用,而對性能良好的器件則有穩定性能的作用。目前,一些廠家將高溫貯存改為高溫反偏,即在高溫貯存中加電壓,其反偏電壓的選擇取決于被測器件,通常選取pn結的反偏壓為額定電壓的75%,以有效地揭示與氧化層沾污有關的機理,也稱為電耐久性試驗。

半導體器件的一些其他失效分析方法和程序,也在積極地探討是否可應用于KGD老化、篩選,成為KGD的一部分,例如:電性能測試、內部檢查、探針電測試、鈍化層缺陷分析、金屬化層缺陷分析、氧化層缺陷分析、剖面分析等等,并進一步提高器件電參數的一致性,主要電參數、工藝過程缺陷率的控制或關鍵工藝參數指標的Cpk達到不小于1.33,使器件質量和可靠性水平提高0.5到1個數量級。

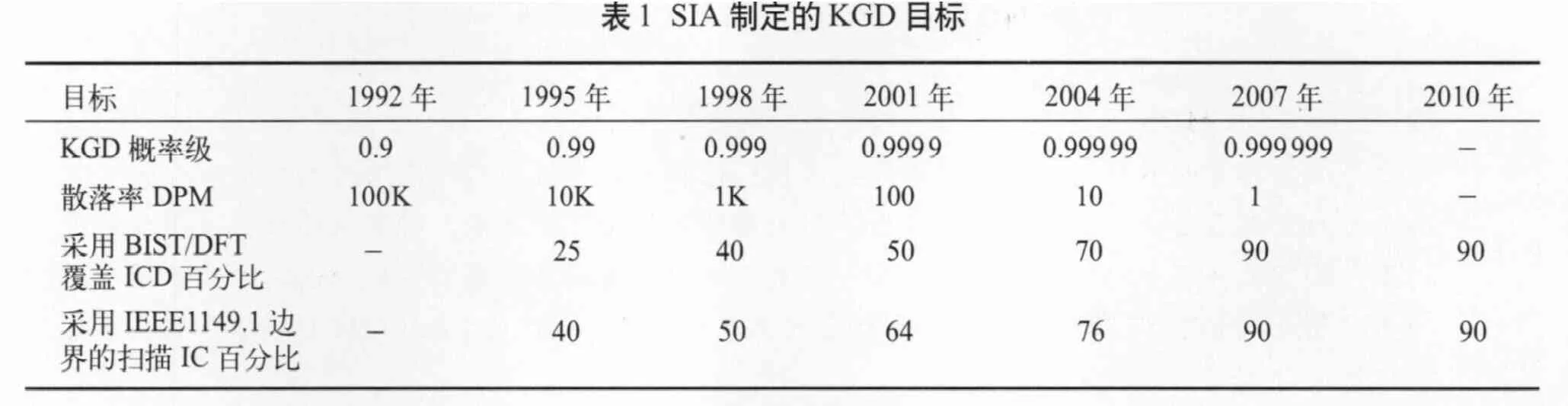

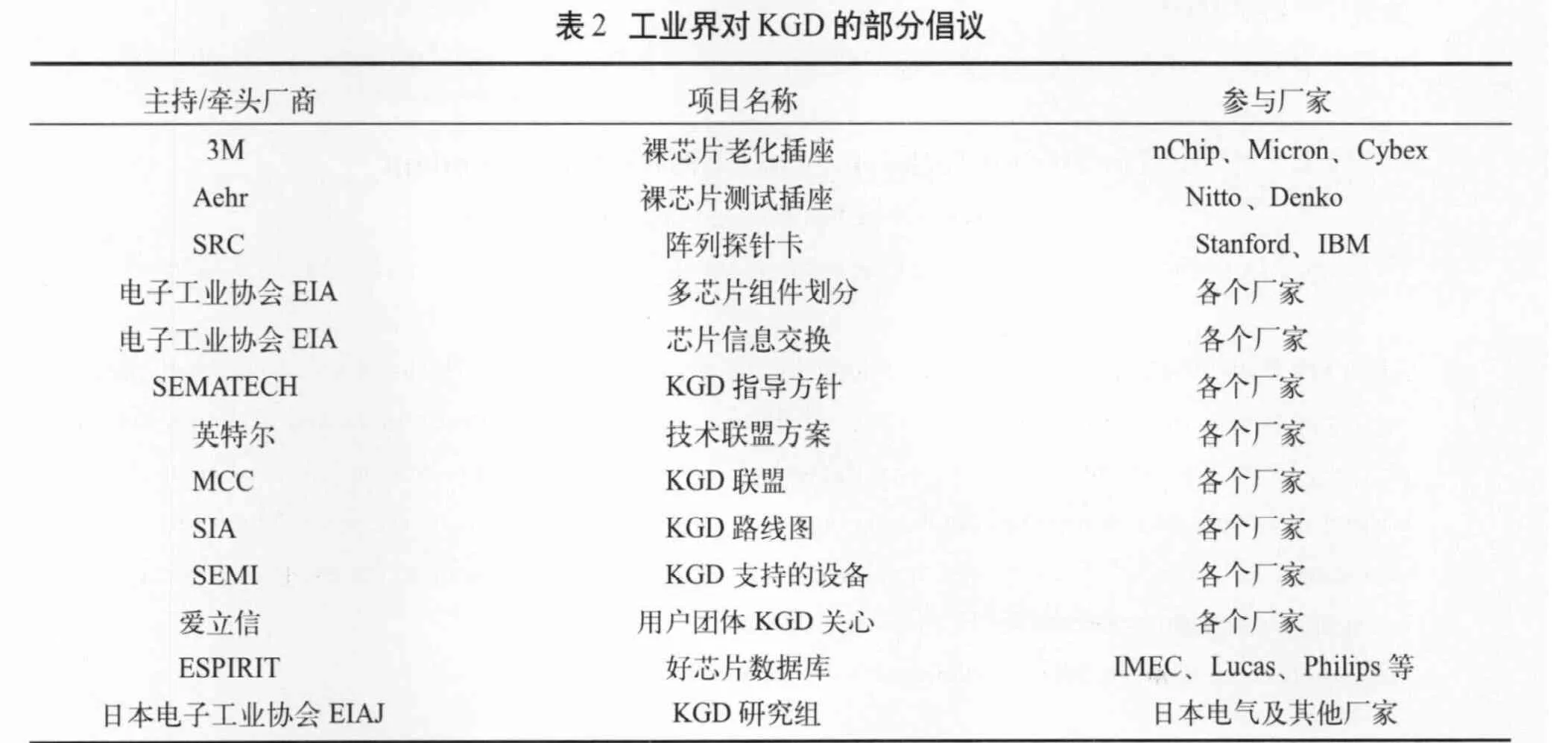

5 KGD的標準問題

KGD技術尚處于不斷發展之中,產品的質量和可靠性最終需固化在標準或詳細規范上,以標準分解目標,以標準固化要求,以標準評價水平,以標準保持連續批量生產產品質量,既要考慮當前的研制/生產可能條件,也要著眼客戶的使用要求,表1列出美國半導體行業協會SIA制定的KGD路線圖。政府部門積極推動KGD技術和基礎發展,產業界在KGD開發工作上覆蓋很多范圍,如表2所示出。微電子與計算機技術中心MCC和SEMATECH首先聯合制定針對KGD采購與KGD技術開發問題的四種詳細規范,在產業界、聯盟和政府的倡議下,制定多個業界標準,例如:EIA/JESD49 Standard KGD、EIAJ/JEDR4703、倒裝焊FCKGD、TAB-KGD、技術評估指導方針TAG-KGD等,為制定或評價KGD技術提供指導。提供KGD的公司包括半導體制造商、第三方芯片加工商和測試站,標準日趨成熟并獲得工業支持,其市場進入成熟期間,芯片買賣雙方特別關注芯片質量和可靠性的預期與供貨水平,規范和指導方針解決開發、采購和使用KGD所需要的關鍵問題和信息,標準化芯片級數據表的制定、芯片產品應用支持與戰略聯盟,所開發的KGD數據庫可更好地提供客戶需要的KGD產品數據。

EIA/JESD49標準制定使高可靠裸芯片形式的集成電路或分立器件KGD的采購和使用更為便利,對制造方在交付高等級KGD產品時提出產品編號和抽樣方案、KGD設計數據、電測試數據、質量保證、可靠性預計等方面的具體要求和指南,提供給客戶的資料、包裝、運輸、芯片貯存環境等要求以及制造方對客戶就KGD的使用提出的建議。此外,該標準還指出KGD客戶在適當應用、處理、組裝和長期環境保護裸芯片產品上承擔很大的責任。EIAJ/JEDR4703是日本電子工業協會制定的KGD質量保證指南,規定裸芯片的3個質量等級、裸芯片制造方交付產品時應提供給客戶的資料(含電路設計、物理設計、質量保證等信息)、包裝要求、貯存要求以及不合格的處置。國際頂級半導體廠商的大多數制造商都宣稱可提供某種KGD,最積極的廠商已提供其芯片交換信息格式的KGD數據,交換格式制定了某種篩選,以保證真正的KGD。產品標準制定與產業化密切相關,純粹采取劃片后測試和老化篩選不能完全確保產品,大規模、復雜性、系統性的HIC、MCM、SiP等封裝所使用裸芯片的品種多而雜,改善KGD芯片制造環節也是一種方法,KGD標準制定要從芯片開始著手。

6 結束語

KGD是上世紀九十年代提出并迅速發展的一項適用技術,伴隨著芯片封裝的不斷研發及市場需求而一步一步前進,這兩者在進行有效的整合,為芯片制造和封裝測試開拓新平臺,目前其商業化水平能實現令人信服的利益和創新封裝機遇,深入解決KGD工藝、老化、篩選、測試、標準、成本與可靠性等關鍵問題,是芯片與封裝科學和諧發展的必備條件。

[1]GB/T4589.1-2006分立器件和集成電路總規范[S].

[2]SJ/T10415-93晶體管熱敏參數快速篩選試驗方法[S].

[3]GJB128A-97半導體分立器件試驗方法[S].

[4]CHARLES H K. Tradeoffs in Multichip Module Yield and Cost with Known Good Die Probability and Repair [J].Microelectronics Reliability,2001,41(9):715-733.

[5]黃慶安.微系統封裝[M].南京:東南大學出版社,2005.

[6]王傳聲,葉天培,等.多芯片組件技術手冊[M].北京:電子工業出版社,2006.

[7]黃云,恩云飛,師謙,等.KGD質量和可靠性保障技術[J].半導體技術,2005,30(5):40-43.

[8]馮玲玲.淺述KGD測試技術及質量保證[J].混合微電子技術,2006,17(3):43-48.

[9]http://WWW.mcc.com/projects/kgd [EB/OL].

[10]http://WWW.imec.be/kgd [EB/OL].

[11]http://WWW.gooddie.com [EB/OL].