EEPROM冗余糾錯設計技術

張國賢,王曉玲,周昕杰

(中國電子科技集團公司第五十八研究所,江蘇 無錫 214035)

1 引言

自摩爾定律提出以來,集成電路持續地按此定律增長,這是基于柵長不斷縮小的結果,器件柵長的縮小基本上依照等比例縮小的原則,促進其他工藝參數的提高。目前集成電路CMOS基本單元已經進入納米時代。和CMOS發展趨勢一樣,存儲器具有更大容量、更小體積和更低功耗的發展前景。對于EEPROM來說,從問世至今幾十年的時間里,發展速度驚人,目前容量已經發展到幾十兆。EEPROM的發展是以EEPROM的單元結構的變革為基礎的。良好的EEPROM單元結構具有以下特點[1]:

(1)簡化的工藝。如何采用簡化的工藝做出EEPROM是進行EEPROM單元結構變革的首要考慮因素;

(2)減少單元面積。在保證性能的前提下,面積必須做得盡可能小,以提高集成度;

(3)提高可靠性。耐久度和保持特性是EEPROM的兩個重要的可靠性參數。單元的設計優化是保證EEPROM具有良好耐久性的基礎。

2 EEPROM冗余糾錯技術介紹

由于存儲器容量不斷地增大,存儲器陣列在生產過程中出現缺陷的可能性將大大增加。為了提高產品的可靠性及經濟效益,冗余設計技術被提出來。利用冗余設計技術,將有誤的數據發現并糾正。冗余糾錯技術包括:硬件冗余糾錯和軟件冗余糾錯。硬件冗余糾錯指用冗余的單元替代正常陣列中有缺陷的單元。軟件冗余糾錯是指用編碼技術,插入糾錯碼,將錯誤的存儲信息糾正。

2.1 硬件冗余糾錯技術

硬件冗余糾錯技術主要有以下幾類:列冗余、行冗余、行列冗余。

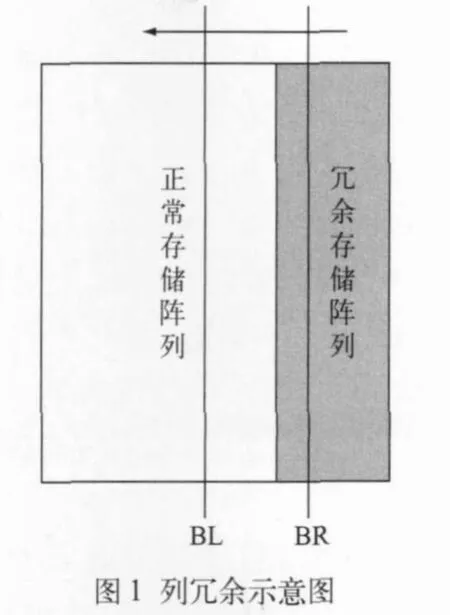

列冗余是指對位線,即Y方向上的冗余。如果正常存儲陣列中在位線(BL)即Y方向單元存在缺陷,以位線為單位,使用冗余的位線(BR)替代有缺陷的位線(BL)。圖1所示為列冗余示意圖。

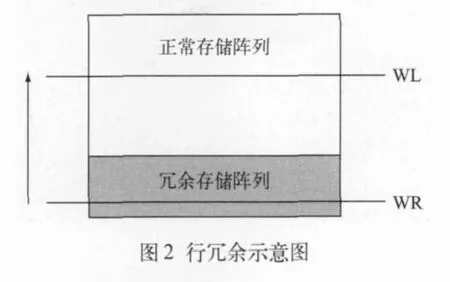

行冗余是指對字線,即X方向上的冗余,如果正常存儲陣列中在字線(WL)即X方向單元存在缺陷,以字線為單位,使用冗余的字線(WR)替代有缺陷的字線(WL)。圖2為行冗余示意圖。

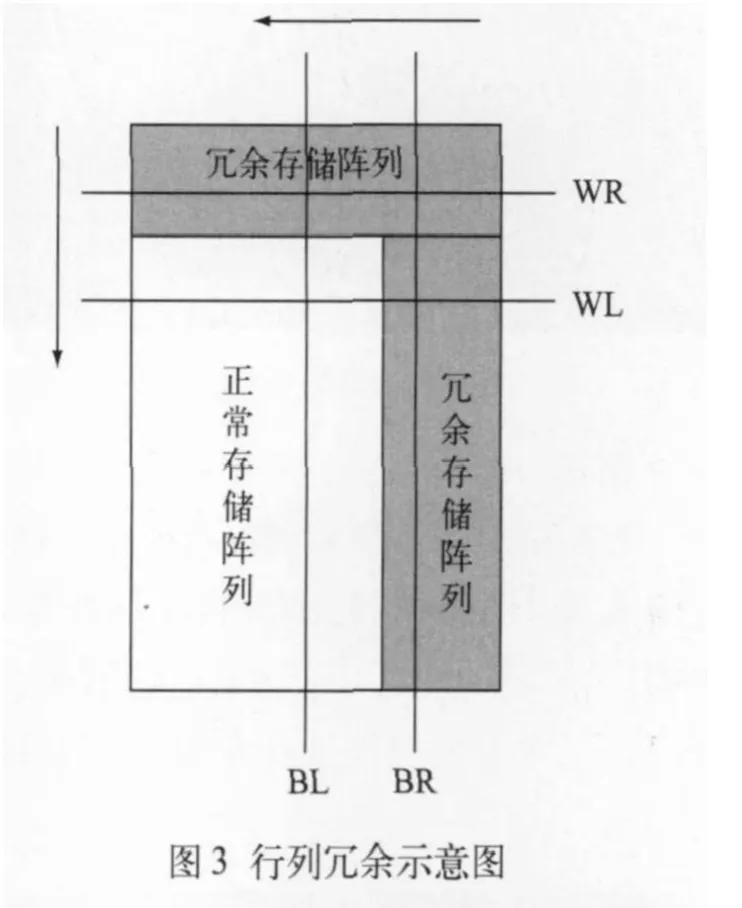

行列冗余是指對字線和位線,即X、Y方向均添加冗余,如果正常存儲陣列中在字線(WL)即X方向,位線(BL)即Y方向單元均存在缺陷,以字線或者位線為單位,使用行列冗余線(WR、BR)替代有缺陷的字線(WL)和位線(BL)。圖3為行列冗余示意圖。

上述的三種冗余糾錯技術,采用哪種技術,要根據芯片缺陷地址的分布來決定。如果存儲陣列中的缺陷單元主要集中在位線上,則使用列冗余;如果存儲陣列中的缺陷單元主要集中在字線上,則使用行冗余;如果存儲陣列中的缺陷單元在字線和位線上都存在,則使用行列冗余。

硬件冗余糾錯操作電路包括地址接收電路、地址譯碼電路。地址譯碼電路接收地址輸入信號后,可以在存儲陣列中找到唯一對應的存儲單元,然后完成各種讀寫操作。

若所選中的操作存儲單元存在缺陷,那將不能完成正常的存儲功能(包括編程、擦除、讀),則希望能夠使用正常的冗余存儲單元來替代這些缺陷單元,為此必須增加CAM(Content Addressable Memory)單元和地址比較電路。CAM單元的作用是存儲缺陷地址,地址比較電路的作用是在地址譯碼前將輸入地址與缺陷地址進行比較,并將比較結果送到行或列譯碼器,根據比較的結果以決定是否需要進行冗余替換。

當正常的存儲陣列中存在缺陷單元時,首先要將缺陷單元地址寫入CAM單元,每次譯碼電路啟動前,都需要將存儲陣列單元地址和CAM單元進行比較,如果比較結果顯示為缺陷地址,標志為1,啟動冗余譯碼電路,同時屏蔽正常的譯碼電路,有缺陷的單元被替換,完成冗余替換操作。如果比較結果顯示為非缺陷地址,標志為0,則不啟動冗余譯碼電路,仍然對正常陣列中的單元操作,不進行冗余替換。冗余替換電路如圖4所示。

在外圍第一個冗余代替存儲單元中存儲數據為20H,代表第32頁存儲陣列存在缺陷,將被替代。當地址輸入為20H時,冗余替代電路經過判斷后,Y<0>輸出為“1”,用冗余陣reduan1代替有缺陷的存儲陣列。冗余替代電路工作正常,仿真結果如圖5所示。

2.2 軟件冗余糾錯技術

軟件冗余糾錯技術考慮采用海明碼編碼技術,指在內部增加校驗邏輯[2]。發現并糾正錯誤的數據。

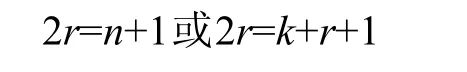

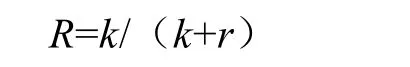

海明碼是R. Haiming提出的一種可以糾正一位錯的差錯控制碼,海明碼是利用在信息位為k位,增加r位冗余位,構成一個n=(k+r)位的碼字,然后用r個監督關系式產生的r個校正因子來區分無錯和在碼字中的n個不同位置的一位錯。它必需滿足以下關系式:

海明碼的編碼效率為:

式中:k為信息位位數;R為增加冗余位位數。

我們以8位存儲數據適于編程的方法舉例說明海明碼的編碼和解碼。

(1)海明碼的編碼

已知信息碼為:“11001100”(k-8),把冗余碼A、B、C…順序插入信息碼中,得海明碼碼字:“A B 1 C 100 D 1100”,碼位:12345678 9101112,其中A,B,C,D分別插于2k位(k=0,1,2,3),碼位分別為1,2,4,8。

冗余碼A,B,C,D的線性碼位是:

A:1,3,5,7,9,11;

B:2,3,6,7,10,11;

C:4,5,6,7,12;(注5=4+1;6=4+2;7=4+2+1;12=8+ 4)

D:8,9,10,11,12。

把線性碼位的值的偶校驗作為冗余碼的值(設冗余碼初值為0):

A=Σ(0,1,1,0,1,0)=1

B=Σ(0,1,0,0,1,0)=0

C=Σ(0,1,0,0,0)=1

D=Σ(0,1,1,0,0)=0

海明碼為:“10111000 1100”。

(2)海明碼的解碼

已知接收的碼字為:“10011000 1100”(k=8)

設錯誤累加器(err)初值=0

求出冗余碼的偶校驗和,并按碼位累加到err中:

A=Σ(1,0,1,0,1,0)=1 err=err+20=1

B=Σ(0,0,0,0,1,0)=1 err=err+21=3

C=Σ(1,1,0,0,0)=0 err=err+0=3

D=Σ(0,1,1,0,0)=0 err=err+0=3

由err≠0可知接收碼字有錯,碼字的錯誤位置就是錯誤累加器(err)的值3。

糾錯,即對碼字的第3位值取反得正確碼字:“101110001 100”。把位于2 位冗余碼刪除得信息碼:“11001100”。

由以上海明碼理論,擴展存儲塊存儲位數為12位,其中有4位是冗余位,放置糾錯碼,增加了外圍邏輯電路對存儲數據的糾錯,從而保證數據的正確性。具體實現電路如圖6所示。

用00001111一組數據進行模擬糾錯仿真,生成的糾錯碼為0001,為驗證糾錯功能,我們修改了一位數據,修改后數據連糾錯碼一起組成新的一串數據:100011110001,代入驗證。結果糾錯電路將我們自行修改的10001111數據,該回00001111。電路實現了預期的功能,仿真波形如圖7所示。

3 小結

由于EEPROM存儲器容量不斷的增大,存儲器陣列在生產過程中出現缺陷的可能性將大大增加。為了提高產品的可靠性及經濟效益,本文引入了冗余設計技術。利用冗余設計技術,將有誤的數據發現并糾正。冗余糾錯技術包括:硬件冗余糾錯和軟件冗余糾錯。硬件冗余糾錯指用冗余的單元替代正常陣列中有缺陷的單元。軟件冗余糾錯是指用編碼技術,插入糾錯碼,將錯誤的存儲信息糾正。

利用硬件和軟件冗余糾錯技術保證了EEPROM的可靠性,為目前的工作提供了技術基礎,并為以后的EEPROM設計工作提供了良好的技術借鑒。

[1]于宗光,郝躍.電可改寫非揮發存儲器[M].北京:國防工業出版社,2002.

[2]張鈺,鄭陽明,等.皮衛星星載計算機存儲模塊的容錯結構設計[J].宇航學報,2008,(29):2057-2016.