級聯MOSFET均壓測試方法研究

付明,王子才,張華,張東來

(1.哈爾濱工業大學 航天學院, 哈爾濱 150001; 2.深圳航天科技創新研究院,廣東 深圳 518057; 3.哈爾濱工業大學(深圳) 機電工程與自動化學院,廣東 深圳 518055)

0 引 言

級聯MOSFET經常應用在高壓半導體開關中,采用均壓措施的級聯MOSFET能實現高壓、大電流的開關切換[1-5]。均壓驅動控制方法是級聯MOSFET研究領域中的一項關鍵技術,開關動態均壓測試是評判級聯MOSFET均壓效果最直接的措施[6],因此均壓測試方法的精度及可信度對均壓驅動控制方法研究以及高壓開關產品檢驗具有決定性的意義[7-10]。

采用隔離度高、靜態電流小、寄生電容小的高壓探頭可顯著提升均壓測試效果,但該測試方法過于昂貴,且不當的測試方法同樣也會引入干擾和誤差[11]。文章通過對比常規均壓測試方法帶來的問題,給出了一種新的級聯MOSFET均壓測試方法,并實驗驗證了該測試方法中高壓探頭寄生參數對級聯MOSFET均壓效果的影響。

1 級聯MOSFET型高壓開關

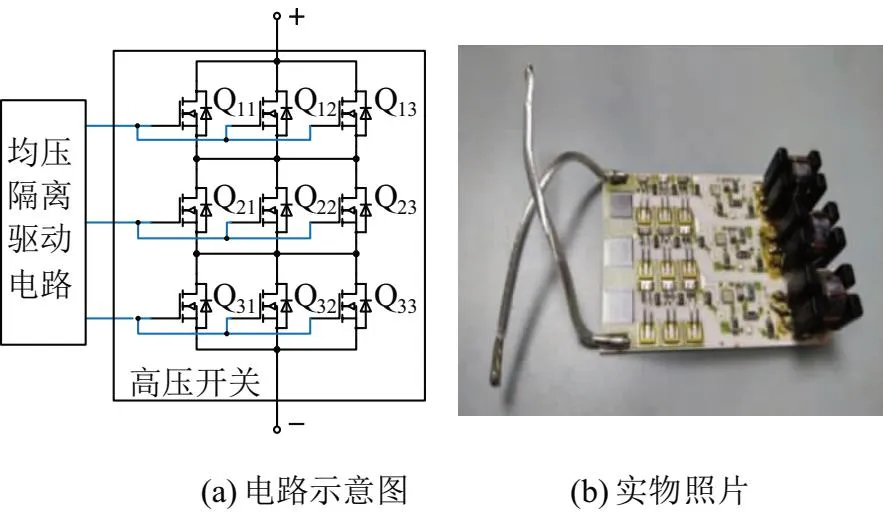

圖1(a)所示為一種級聯MOSFET配置方式,其采用3個MOSFET并聯構成1組用來擴展電流能力,3組串聯用來擴展耐壓能力。均壓隔離驅動電路通過對串并聯MOSFET的門極進行控制,確保所有的MOSFET同時開通和關斷,從而達到并聯均流和串聯均壓的目的。

SiC基MOSFET具備高壓大電流的特點,對該型MOSFET的串并聯研究非常廣泛[12-13]。圖1(b)為已驗證均壓效果良好的級聯MOSFET型高壓開關,其采用厚膜工藝將圖1(a)所示的3串3并MOSFET裸芯片(選用CREE公司的SiC基MOSFET裸芯片,型號為CPM2-1200-0025B)集成在了一個厚膜陶瓷板上,該封裝有利于串聯均壓和并聯均流,并能顯著減小高壓開關體積。該高壓開關器件最大開關電壓3 600 V,通流能力50 A。下文將以該級聯MOSFET組成的高壓開關驗證所提出的均壓測試方法。

圖1 級聯MOSFET高壓開關

2 傳統均壓測試方法

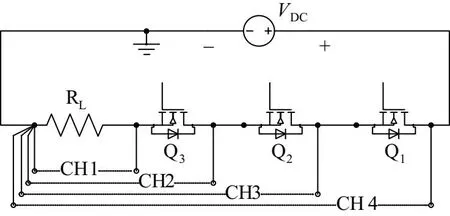

將圖1(b)所示級聯MOSFET的高壓開關放置在高邊,對每一組串聯MOSFET的DS電壓進行測試,通過判斷DS電壓波形的畸變來評估均壓測試方法對均壓效果的影響。

2.1 直接均壓測試方法

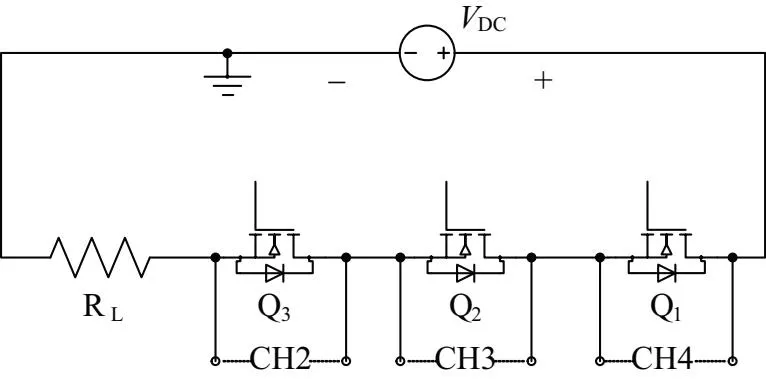

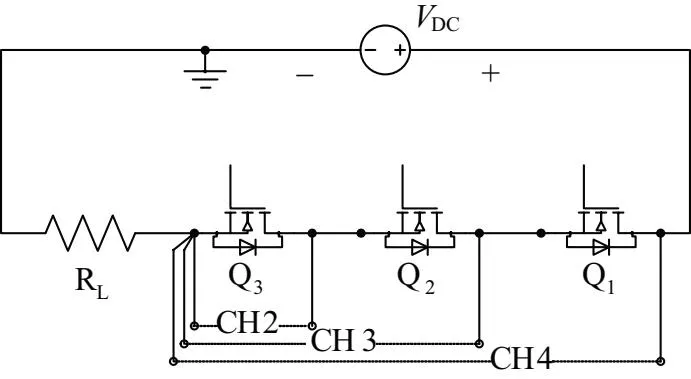

常規均壓測試方法是采用高壓隔離探頭直接測試每一組MOSFET在開關瞬間的DS電壓波形,通過判斷瞬態DS電壓波形的一致性來看均壓效果。圖2為使用3個高壓隔離探頭直接測試均壓效果的示意圖。電源電壓VDC=1000 V,負載為純阻性RL=410 Ω,高壓開關切換控制信號為0.5 Hz的方波。

圖2 高壓隔離探頭直接測試均壓效果的示意圖

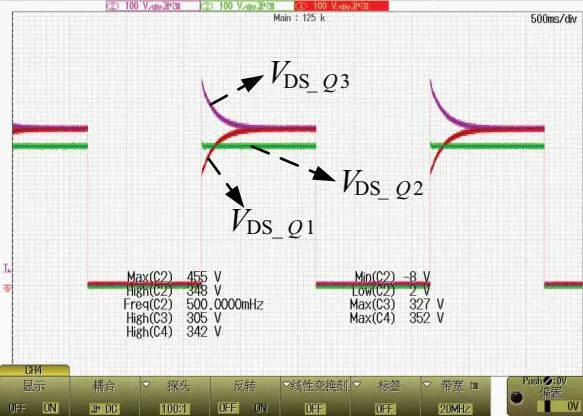

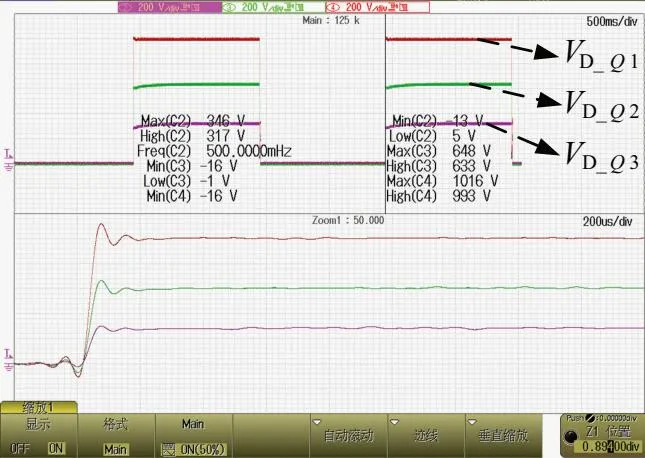

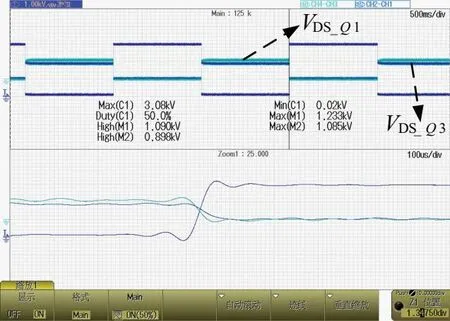

圖2中3個高壓隔離探頭分別對3排MOSFET的D、S端電壓進行測試,通道CH4測試Q1(代表第一排MOSFET)的DS電壓波形,CH3、CH2分別測試第二排Q2、第三排Q3的DS電壓波形。圖3為直接均壓測試波形,結果表明均壓一致性很差,因均壓措施經校驗是符合要求的,所以判斷該直接測試方法中,隔離探頭的寄生參數影響了級聯MOSFET的均壓效果。

2.2 隔離探頭寄生電容對測試誤差的分析

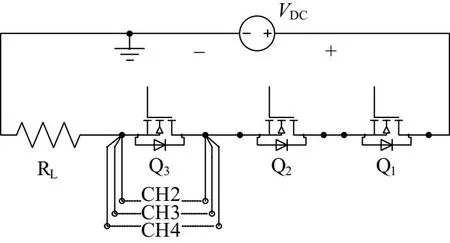

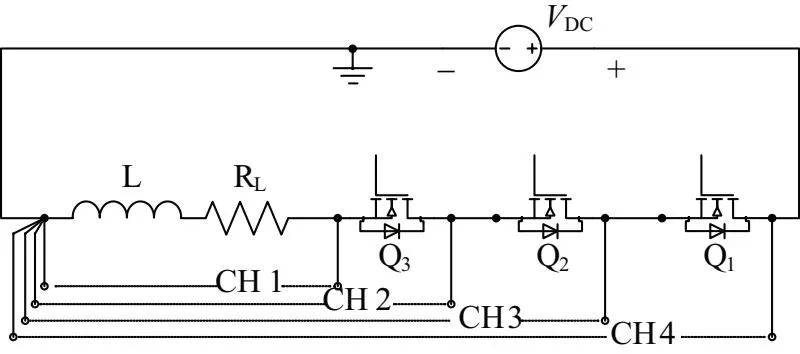

為評估隔離探頭寄生參數對均壓效果的影響,如圖4所示,通過改變Q3的D、S端測試探頭的數量,驗證探頭寄生參數對Q3的VDS測試影響。

圖3 直接測試均壓效果的示意圖

圖4 研究隔離探頭數量對Q3的均壓效果測試示意圖

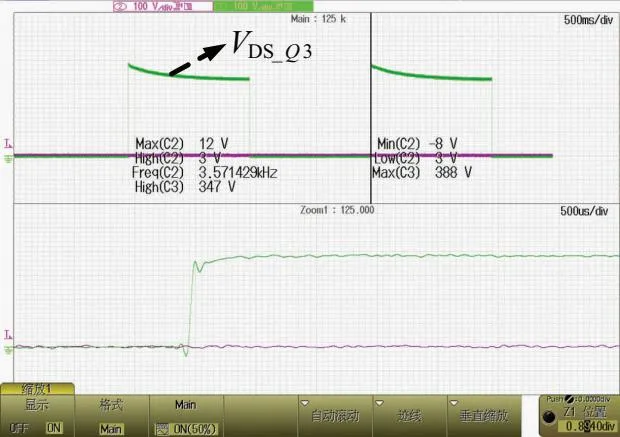

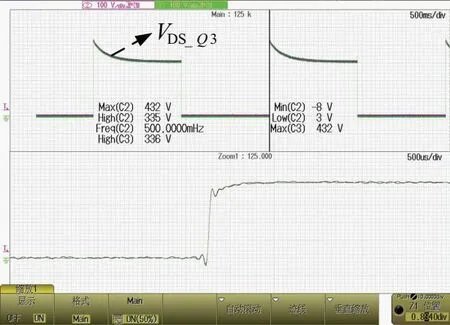

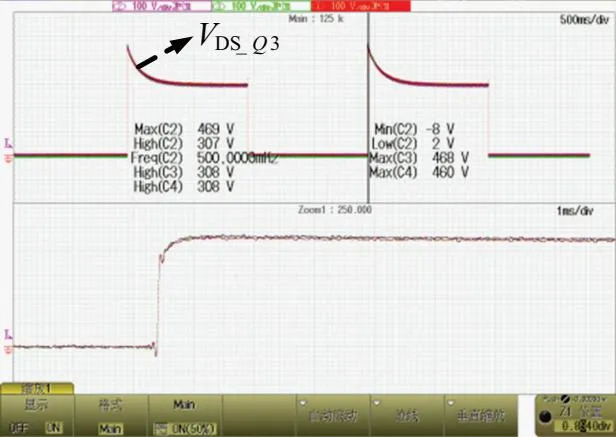

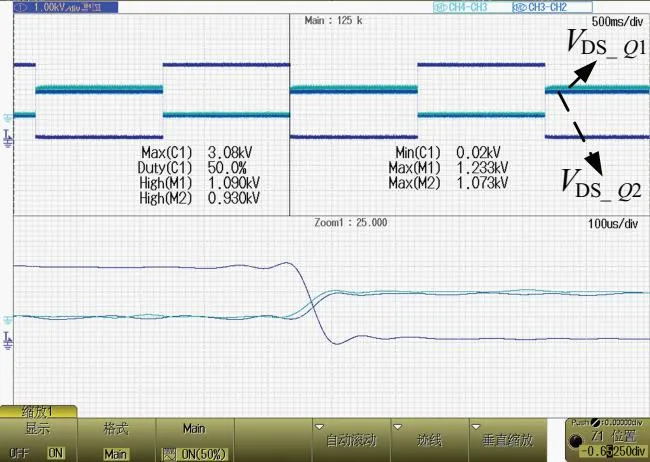

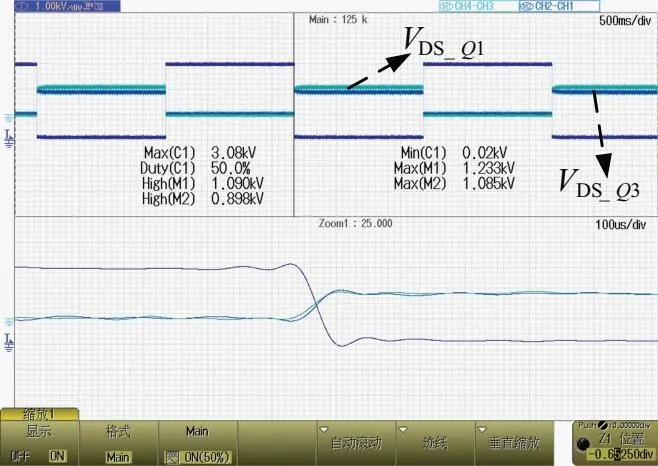

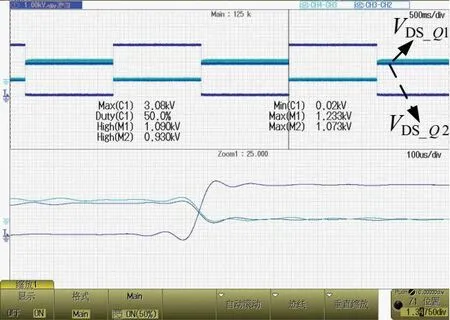

圖5~圖7分別為一個、兩個、三個隔離探頭測試Q3的VDS波形。測試結果表明,相同型號隔離探頭數量越多,Q3的VDS在關斷瞬間峰值電壓越高,與關斷后的穩態值偏差越大,從而導致均壓效果變差。這說明測試引入的寄生參數越大,對被測對象的均壓效果影響越大。

圖5 一個隔離探頭測試Q3的VDS波形

圖6 兩個隔離探頭測試Q3的VDS波形

圖7 三個隔離探頭測試Q3的VDS波形

3 減法均壓測試方法

基于上一節測試結果表明隔離探頭寄生參數對級聯MOSFET的均壓效果有明顯的干擾作用,本節將主要從減小寄生參數干擾的方面提出一種改進型均壓測試方法,即減法均壓測試方法。

3.1 提出的減法均壓測試方法

改變隔離探頭的接法,將所有探頭的地同時接Q3的S極,探頭的正端分別接Q1、Q2、Q3的D極,再通過示波器減法計算出Q1和Q2的VDS波形。圖8為提出的減法均壓測試方法示意圖。

圖8 減法均壓測試方法示意圖

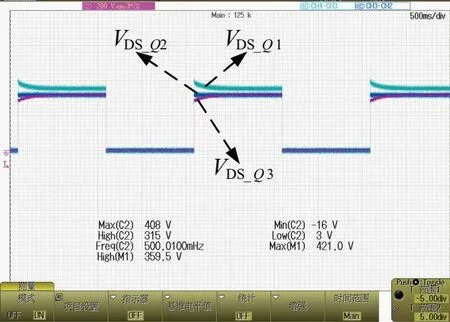

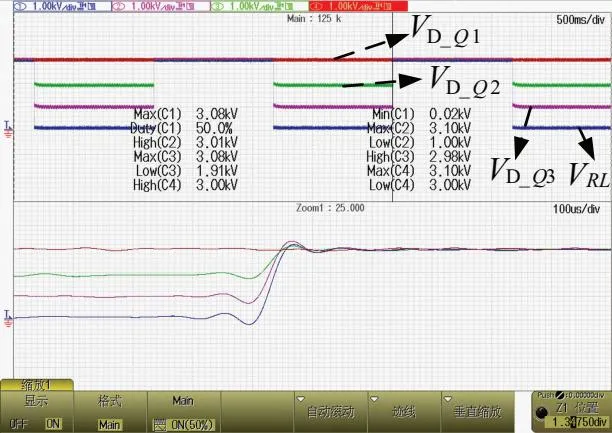

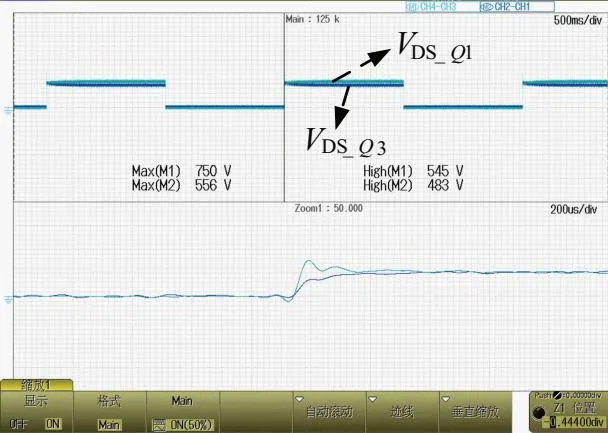

圖9為減法均壓測試方法的測試電壓波形,三個電壓波形在關斷時的穩態電壓值成線性比例。圖10為減法運算后的3個VDS波形,其中運算1(CH4-CH3)為圖8中Q1的D端對地電壓波形減去Q2的D端對地電壓波形得到Q1的VDS波形,運算2(CH3-CH2)為減法得到Q2的VDS波形。從圖10的電壓波形減法結果可知,均壓測試一致性要比圖3所示的直接均壓測試電壓波形精度要高,但均壓測試偏差仍超過了平均值的26%,提示測試方法有待進一步改進。

3.2 改進后的減法均壓測試方法

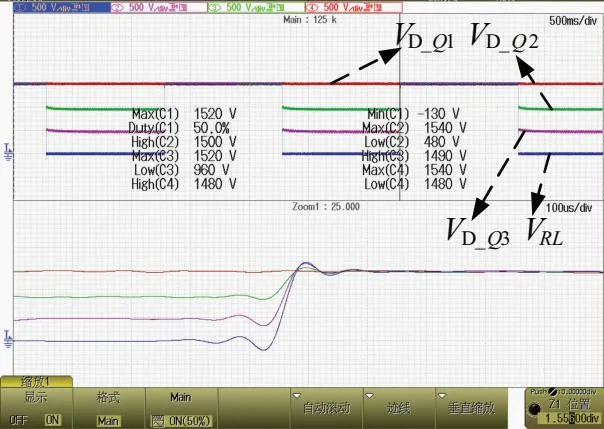

為減小探頭寄生參數對減法均壓測試的進一步影響,圖11所示為改進后的減法測試方法,將負載包含在均壓隔離探頭的測試跨度范圍內,采用4個探頭進行測試:CH1接Q3的S極,CH2接Q3的D極,CH3接Q2的D極,CH4接Q1的D極,所有探頭的地直接與測試電源的地相連。

圖9 減法均壓測試方法的測試電壓波形

圖10 減法運算后的3個VDS波形

圖11 改進后的減法均壓測試方法示意圖

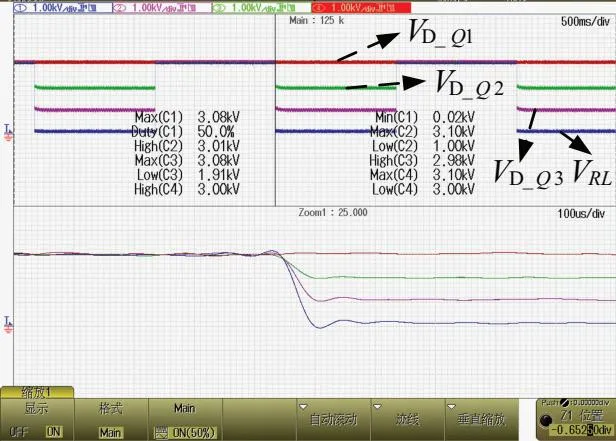

設置VDC電壓為3 000 V,負載電阻RL為6 kΩ。圖12為3組MOSFET均壓測試的VDS波形及關斷瞬間的展開圖。

圖12 均壓測試的VDS波形及關斷瞬間展開圖(條件1)

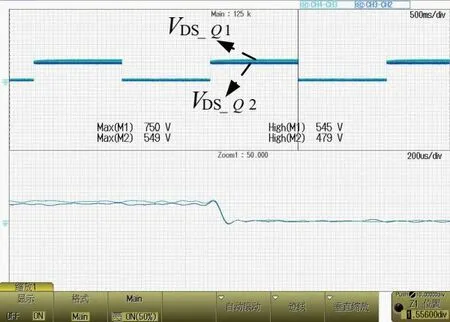

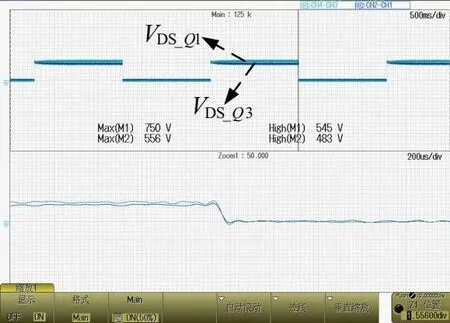

圖13為Q1(CH4-CH3)和Q2(CH3-CH2)關斷瞬間的VDS波形,圖14為Q1(CH4-CH3)和Q3(CH3-CH2)關斷瞬間VDS波形,通過這兩個圖可判斷3組MOSFET在關斷瞬間的VDS波形基本重合,即表明關斷瞬間均壓效果良好。

圖13 減法得到關斷瞬間Q1和Q2的VDS波形(條件1)

圖14 減法得到關斷瞬間Q1和Q3的VDS波形(條件1)

圖15為3組MOSFET均壓測試的VDS波形及開通瞬間展開圖。圖16為Q1(CH4-CH3)和Q2(CH3-CH2)開通瞬間的VDS波形,圖17為Q1(CH4-CH3)和Q3(CH3-CH2)開通瞬間的VDS波形,通過這兩個圖可判斷3組MOSFET在開通瞬間的VDS波形也基本重合。

圖15 均壓測試的VDS波形及開通瞬間展開圖(條件1)

圖16 減法得到開通瞬間Q1和Q2的VDS波形(條件1)

圖17 減法得到開通瞬間Q1和Q3的VDS波形(條件1)

對比以上幾組測試波形,可判斷改進后的減法均壓測試電路,無論是在穩態還是在開通、關斷瞬態,對級聯MOSFET的均壓特性影響均較小。開通、關斷瞬間的均壓效果與高壓開關特性基本一致,證明該減法均壓測試方法能夠真實有效評測級聯MOSFET均壓效果。

4 實驗結果與分析

評估測試線纜的寄生參數對圖11改進后減法均壓測試方法的影響,圖18在測試回路中串聯一個電感模擬線纜的寄生參數。通過測試開關瞬間的均壓效果來評估改進后減法均壓測試方法對線纜寄生參數的適應性。

圖18 評估測試電纜對改進后減法測試方法的影響

設置VDC電壓為1 500 V,負載電阻RL為6 kΩ,L按照測試線纜最大寄生電感量2.3 μH設置。圖19為3組MOSFET均壓測試的VDS波形及關斷瞬間展開波形圖。

圖19 均壓測試的VDS波形及關斷瞬間展開圖(條件2)

圖20為Q1(CH4-CH3)和Q2(CH3-CH2)關斷瞬間的VDS波形,圖21為Q1(CH4-CH3)和Q3(CH3-CH2)關斷瞬間的VDS波形,通過這兩個圖可判斷,增加電感后,3組MOSFET在關斷瞬間的VDS波形相比不考慮測試電纜的純電阻負載方式偏差增大,但仍在誤差容許范圍內。

圖20 減法得到關斷瞬間Q1和Q2的VDS波形(條件2)

圖22為3組MOSFET均壓測試的VDS波形及開通瞬間展開圖。圖23為Q1(CH4-CH3)和Q2(CH3-CH2)開通瞬間的VDS波形,圖24為Q1(CH4-CH3)和Q3(CH3-CH2)開通瞬間的VDS波形,通過這兩個圖可判斷3組MOSFET在開通瞬間的VDS波形基本重合。

圖21 減法得到關斷瞬間Q1和Q3的VDS波形(條件2)

圖22 均壓測試的VDS波形及開通瞬間展開圖(條件2)

通過上面的測試數據可知,改進后的減法測試方式即使在考慮測試線纜寄生參數的情況下,依然能夠很好地評估級聯MOSFET的均壓測試效果。

圖23 減法得到開通瞬間Q1和Q2的VDS波形(條件2)

圖24 減法得到開通瞬間Q1和Q3的VDS波形(條件2)

5 結束語

提出了一種減法均壓測試方法,解決了傳統均壓測試方式中,隔離高壓探頭寄生參數對級聯MOSFET均壓效果的影響。實驗驗證該測試方式能精確評估級聯MOSFET的均壓效果,且不受測試探頭及測試線纜寄生參數的影響。