節(jié)點地震儀電路設計中減小對授時模塊干擾的方法*

陳 潔 趙圣麟 關作金 黃艷妮 李 麗

1) 珠海市泰德企業(yè)有限公司,廣東珠海 519082

2) 中國地震局地球物理研究所,北京 100081

0 引言

地震觀測對時間服務準確度的要求一般在毫秒級。目前多數(shù)地震儀均采用GNSS 模塊為地震記錄信號提供時間服務。楊金梁等[1]研究了物探設備中GNSS 授時原理并對授時精度進行了分析,結果表明,GNSS 授時精度主要受衛(wèi)星軌道徑向精度、衛(wèi)星鐘差和偽距測量精度3 方面的影響。相對于雙頻GNSS 接收機,GPS 與Galileo 授時精度最高,實驗數(shù)據(jù)中總體小于5 ns,BDS 二代在衛(wèi)星軌道徑向和偽距精度比GPS 略差,但BDS 二代衛(wèi)星鐘差太大,導致授時精度在30 ns 左右,GLONASS 授時精度小于30 ns。單頻GNSS 接收機的授時精度會在雙頻接收機授時精度的基礎上降低50 ns 左右。不論單頻還是雙頻,基于衛(wèi)星導航系統(tǒng)的授時基本都能滿足地震監(jiān)測對授時準確度的要求。

衛(wèi)星定位導航系統(tǒng)中衛(wèi)星距地2 萬多km,位于地球表面的天線端所接收到的信號非常微弱,識別這類信號大概相當于分辨1 萬km 之外一只功率為25 W 的燈泡發(fā)出的亮光。劉宏華等[2]分析認為,衛(wèi)星定位導航系統(tǒng)的授時信號極易受到射頻干擾,因此壓制射頻干擾也就成為地震儀獲得高準確度授時的重要前提條件。

對衛(wèi)星定位導航系統(tǒng)授時信號產(chǎn)生干擾的射頻干擾源很多,可能來自接收系統(tǒng)外部的大環(huán)境,也可能來自接收系統(tǒng)本身。本文僅討論壓制來自儀器本身的射頻干擾的方法。

隨著井下地震觀測、便攜流動地震觀測的日益普及,地震儀快速走向集成化和小型化。印刷電路板(Printed Circuit Board,PCB)對授時模塊的電磁干擾會直接影響信號接收靈敏度,進而影響地震儀授時精度。汪漢新等 [3-9]的研究表明,優(yōu)化電路設計、用好電容、做好功能模塊布局是對抗干擾、消除電流感應的有效手段,因此也是地震儀降低授時模塊受到射頻干擾的最直接、最有效途徑。

1 授時干擾的主要來源和壓制方法

來自PCB 內(nèi)部的對授時模塊的射頻干擾,主要是因為鄰近電路之間的寄生耦合及內(nèi)部組件的場耦合,導致信號沿著傳輸路徑有串擾。例如,在地震數(shù)據(jù)器PCB 板上的電容器,一般都會產(chǎn)生等效電感和阻抗,電容都有自諧振頻率,在自諧振頻率下,電容器呈現(xiàn)容性。在高于自諧振頻率時,電容呈現(xiàn)感性,阻抗隨著頻率的增高而增大。

當高速數(shù)字信號線路、開關電路或大功率的控制電路等在極短的時間內(nèi)產(chǎn)生急速電壓電流,或是含有電感和電容的電路頻繁通斷時,射頻干擾就會比較明顯。因此,在進行井下地震儀器、一體化地震儀等緊湊型地震儀PCB 線路設計時,應更加關注如下干擾(圖1):

圖1 地震儀授時干擾源及解決方法示意圖Fig.1 Time service interference source of seismograph and its solution

(1)高頻器件的干擾。當電路中存在高頻時鐘處理器芯片時,或者系統(tǒng)總線的工作周期非常快時,高速電路PCB 板中會產(chǎn)生多倍于時鐘頻率的干擾噪聲,從而向外輻射,影響整體集成電路的其他電路模塊。例如工作頻率32.768 MHz 的地震儀系統(tǒng),由于MCU 內(nèi)置倍頻造成多次諧波,可能影響授時模塊在L1載波1575.42(±3) MHz 頻點的射頻信號接收。

(2)電源的噪聲干擾。高頻噪聲敏感的電路尤其容易受到來自電源的干擾。系統(tǒng)電源在給電路供能時,會把電源寄生的干擾噪聲附加到供電電路上。一些高速邏輯電路工作時的高速轉換,也會使電源線上產(chǎn)生高頻成分豐富的壓降。溫度變化時的直流干擾是產(chǎn)生電源噪聲另外一大原因。

(3)信號傳輸線之間的干擾。當各傳輸線路的特性阻抗不同或與負載阻抗不匹配時,所傳輸?shù)母哳l信號在臨界或終端部位會發(fā)生反射造成的畸變或震蕩。同時,各信號傳輸線的走向、寬度和線間的間距等直接影響高頻信號的傳輸。傳輸線的不合理設計不但會產(chǎn)生線間信號的疊加問題,還會導致信號的附加延時。

(4)地線的噪聲干擾。整體系統(tǒng)中各部分地線的不平衡,會導致地線之間的電位差和接地阻抗,形成環(huán)路電流,這些電磁干擾會引起電路的誤操作并造成傳導和輻射。

為了減少電路中產(chǎn)生的電磁干擾,在地震儀的PCB 板設計中會重點采用電磁兼容設計。對于易出現(xiàn)電磁干擾的部位也會刻意避免電磁干擾的產(chǎn)生。在地震儀PCB 線路的設計中,可以采用如下方式降低甚至避免射頻噪聲的干擾(圖1):

(1)采用最低頻率電路芯片,配置高精度穩(wěn)態(tài)電源。

(2)優(yōu)化電路元器件布局,將模擬信號部分、高速數(shù)字電路、噪聲源部分盡量合理地分開,將電源線盡可能與地線平行。

(3)縮短高速信號傳輸線的長度,將電路中的連接器均布置在PCB 板的同一側。

(4)在布地線時增加一層地線,或采用多地線網(wǎng)格,布設大量的平行地線。

2 壓制授時干擾的實驗及結果

為減少地震儀系統(tǒng)中授時模塊受到的電磁干擾,并保障系統(tǒng)高穩(wěn)定的授時功能,通過多次實驗和測試發(fā)現(xiàn)如下措施有助于提升地震儀授時模塊的抗干擾能力。

實驗中,我們采用的儀器設備主要是RIGOL 的頻譜分析儀,主要針對GNSS 的L1頻段附近的射頻信號進行測試和分析。

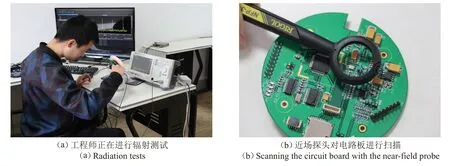

工程師使用儀器對電路板進行輻射信號測試(圖2a)。當近場探頭置于MCU 附近的有源TCVCXO晶振電路時,產(chǎn)生的射頻輻射比較突出(圖2b)。分析原因是晶振采用了32.768 MHz 的頻點,則其48 次諧波頻率是32.768 MHz×48=1572 MHz,剛好在GNSS的民用頻段1575.42 MHz 附近,很容易干擾到來自衛(wèi)星的微弱GNSS 信號,從而影響節(jié)點地震儀的收星性能。

圖2 輻射信號測試Fig.2 Radiation tests

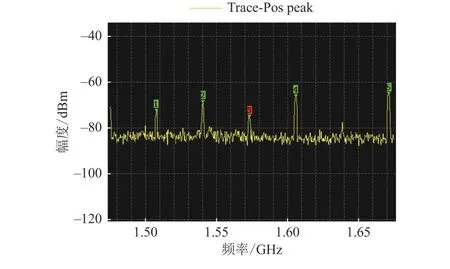

在L1載波1575.42(±3) MHz 頻點附近,存在峰值 點2 為1.54067 GHz,峰 值 點3 為1.5733 GHz,峰值點4 為1.6060 GHz 三個頻帶的干擾(圖3)。

圖3 針對授時模塊未采取本文所述抗擾技術前的幅頻曲線Fig.3 Amplitude-frequency curve for a seismograph without anti-disturbance techniques mentioned in this paper for the time-service module

為此,我們從以下幾個方面進行改進設計。

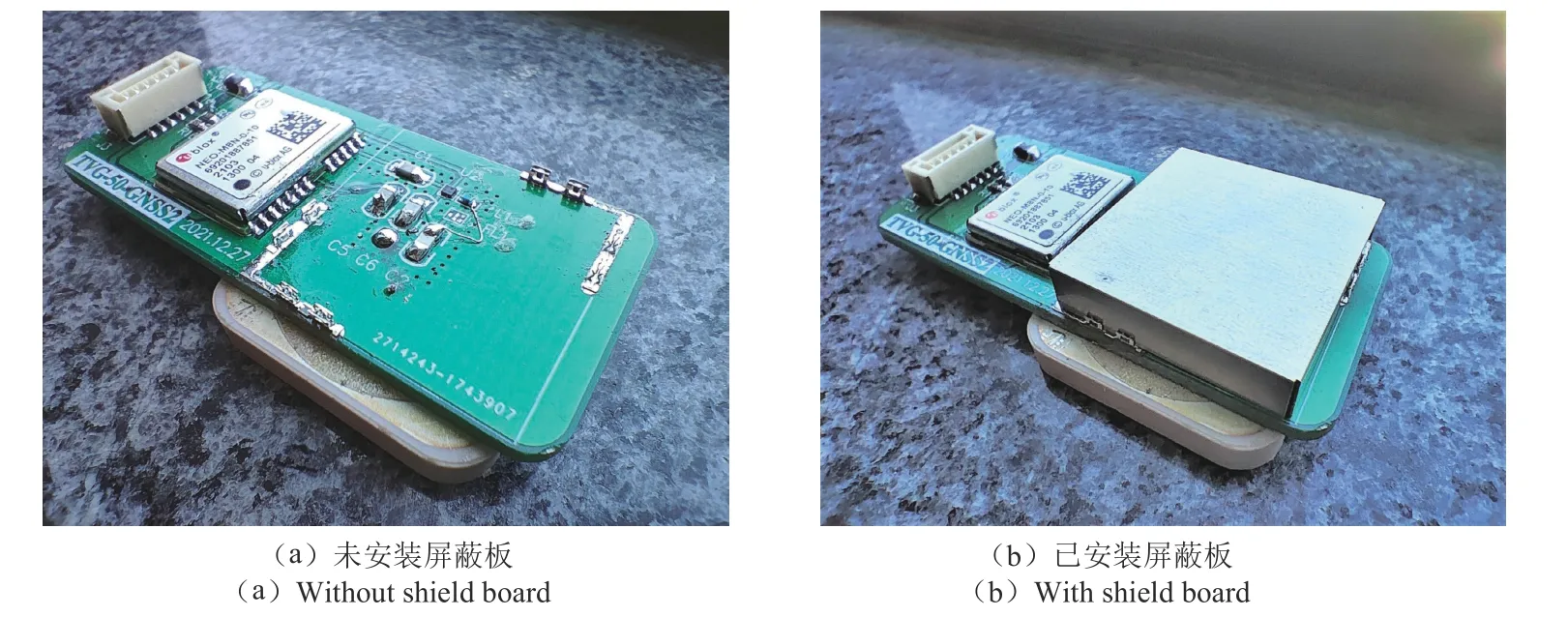

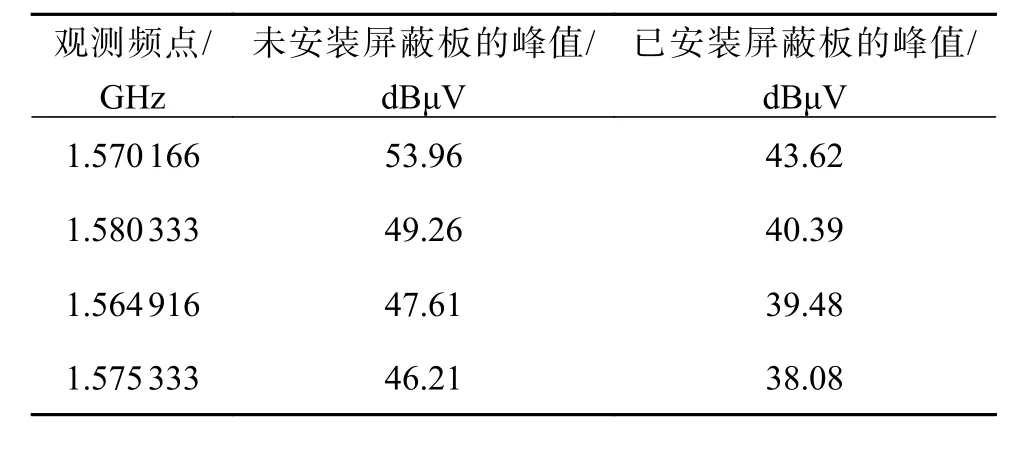

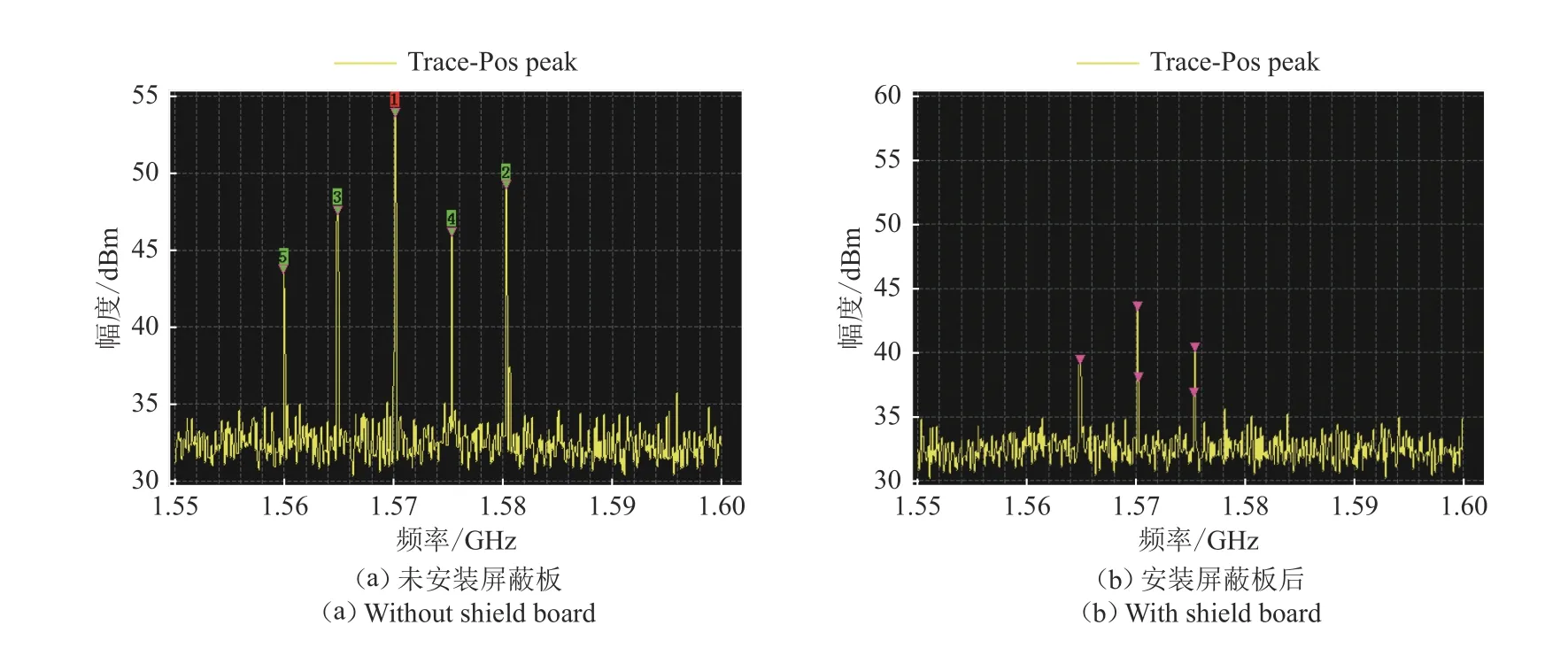

2.1 為射頻電路模塊增加屏蔽板

采用屏蔽隔離等物理手段是減少電磁干擾的重要措施之一。采用國標0Cr18Ni9 材質作為屏蔽板,進行屏蔽板安裝前后的對比測試(圖4)。由測試結果得知,已經(jīng)安裝屏蔽板的授時模塊比未安裝屏蔽板的授時模塊所受到的電磁干擾明顯減弱[5]。研究表明,在提高地震儀授時模塊抗干擾能力方面,增設不銹鋼屏蔽板是非常有效的方法。設計中,衛(wèi)星信號接收放大LNA 模塊部分,以及MCU 的有源TCVCXO晶振部分電路均采用屏蔽罩進行電磁信號屏蔽措施。

圖4 射頻電路安裝屏蔽板前(a) 后(b) Fig.4 RF circuit without (a) and with (b) shield board

2.2 將授時模塊遠離高頻元器件布局

與可能造成干擾的射頻信號源盡量遠離是降低授時干擾的有效方法。實驗和測試中,將授時模塊和授時天線獨立設計為一塊電路板,安裝時,盡可能遠離容易產(chǎn)生電磁輻射的包含晶振電路、高頻芯片、開關電源等模塊的主板[6]。圖5 中是2 種不同的布局方案。

圖5 模塊布局Fig.5 Module layout

2.3 規(guī)整布線、適度隔離

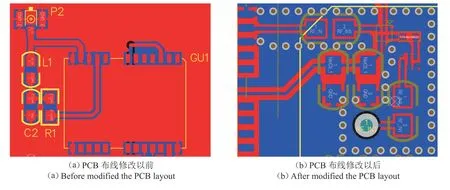

PCB 電路板在設計之初即應緊湊有序,盡量減少、縮短器件之間的引線和連接,電路設計之后的模擬和測試比對尤為重要(圖6)。實測顯示,數(shù)字信號電路和模擬信號電路分開、干擾源與時鐘發(fā)生器等敏感元件遠離、大功率或大電流I/O 驅動電路遠離信號電路是非常有效的降低電子線路本身對授時信號干擾的手段。每一層空余處都鋪上銅與地相連。完整的地平面確保信號層信號輻射有明確的返回路徑,減小線路的天線效應,并且通過盡可能多的過孔將地平面相連。

圖6 PCB 電路板布線Fig.6 PCB layout

2.4 改進效果

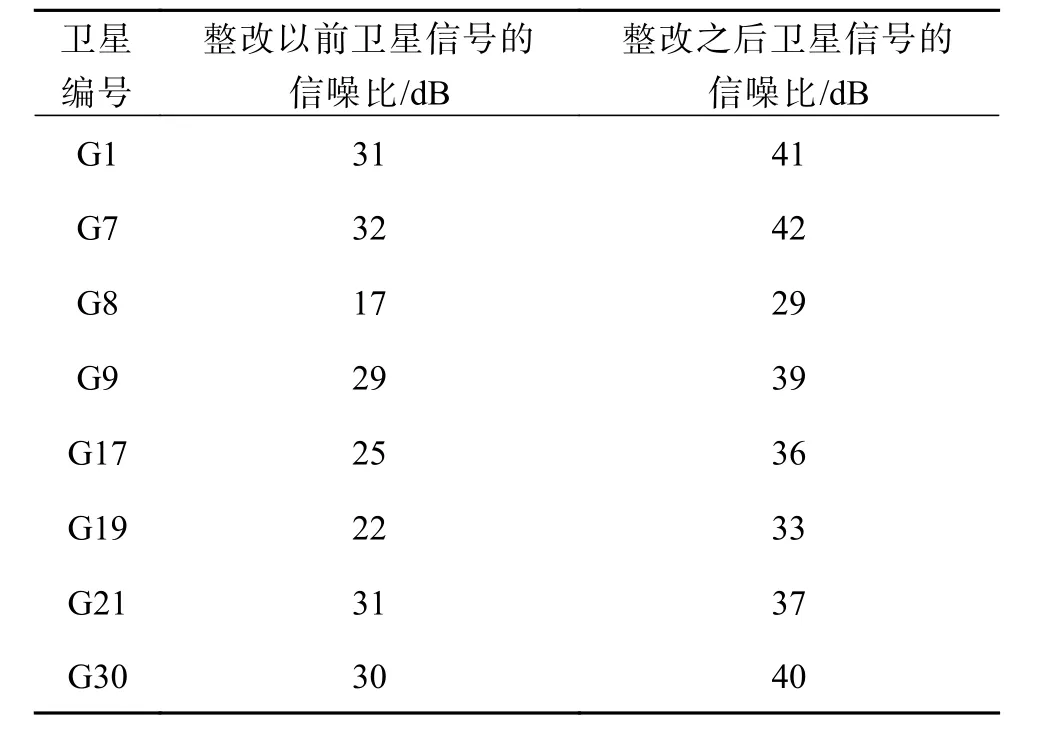

經(jīng)采用國標0Cr18Ni9 材質的屏蔽板、PCB 設計調整、模塊重新布局等實驗后,對比發(fā)現(xiàn),地震儀授時模塊受到的電磁干擾強度狀態(tài)發(fā)生變化(圖7),參考對比數(shù)據(jù)(表1)得知,電磁干擾明顯被壓制。其中,安裝了屏蔽罩后,同一位置同一頻點的輻射水平有了近10 dB 的改善。

表1 屏蔽罩安裝效果對比數(shù)據(jù)Table 1 Comparison data of shield board installation effect

圖7 射頻電路輻射水平Fig.7 The radiation level of RF circuit

另外,選取一些具有信號強度比較高的衛(wèi)星進行衛(wèi)星信號信噪比的對比(表2)。結果顯示合理修改PCB 布線、采用屏蔽罩、合理布局各模塊,能提高約6~10 dB 的信噪比,表明授時模塊受到的電磁干擾明顯減弱,收星能力大大增強。

表2 整改前后對比數(shù)據(jù)Table 2 Comparison data before and after rectification

為更好地擬合井下地震儀和一體化地震儀的 “緊湊” 電子環(huán)境,研究團隊進行了極限電路測試(圖8)。測試以一款節(jié)點式地震儀(TVG-50)為原型,該款地震儀為開展深部地球物理探查而設計,需滿足小體積、高靈敏、大動態(tài)、低功耗、抗惡劣環(huán)境等嚴苛的探查條件。設計的指標是寬頻帶(1/2/5/10/30 s~200 Hz)、24 位低噪聲采集、力平衡反饋、最快4 KHz采樣速率、最長1 個月時間鋰電池供電,因此高準確授時、高性能電容換能和大容量存儲是不可回避的技術底線。

圖8 授時模塊抗干擾改進后的野外測試及結果Fig.8 Field test and wave recording after modification with anti-disturbance techniques for the time-service module

值得一提的是,大量設備的野外對比和實際波形數(shù)據(jù)分析顯示,在緊湊型的地震儀設計中取得的授時模塊抗干擾技術具有可行性和有效性,量產(chǎn)地震儀的授時性能得到了平穩(wěn)、一致的提升,野外觀測效果見圖8c 。

3 結束語

在深井地震儀、一體化地震儀等緊湊度要求比較高的地震儀設計中,通過改善PCB 板電路設計、優(yōu)選適當元件、增設屏蔽板等方式,可以穩(wěn)定提高地震儀授時模塊的抗干擾能力,進而提高地震儀授時功能的可靠度。

致謝

感謝北京白家疃地球科學國家野外科學觀測研究站、中國地震局地球物理研究所地震科學數(shù)據(jù)中心對本文野外實驗和數(shù)據(jù)處理的幫助。