基于虛擬孔與雙軌預(yù)充電技術(shù)的電流型混淆邏輯電路設(shè)計(jì)

姚茂群,李聰輝,薛紫微,李海威

(1.杭州師范大學(xué) 信息科學(xué)與技術(shù)學(xué)院,浙江 杭州 311121;2.臺(tái)州科技職業(yè)學(xué)院 信息工程學(xué)院,浙江 臺(tái)州 318020)

0 引言

隨著半導(dǎo)體技術(shù)的不斷發(fā)展,集成電路(integrated circuit,IC)的設(shè)計(jì)也變得多樣且復(fù)雜。以密碼芯片為代表的加密硬件應(yīng)用廣泛,小到公交卡、銀行卡,大到通信基站以及軍用設(shè)施。正因?yàn)槊艽a芯片的重要性,與之相關(guān)的安全問題也逐漸增多,為竊取密碼芯片的設(shè)計(jì)結(jié)構(gòu)以及所處理的數(shù)據(jù),攻擊者常采用逆向攻擊、功耗攻擊等方式攻擊密碼芯片,帶來諸多安全問題,嚴(yán)重影響IC 產(chǎn)業(yè)的發(fā)展。

逆向攻擊[1-3],先對(duì)芯片采取解封裝、化學(xué)腐蝕等處理,再利用光學(xué)顯微鏡分析芯片的內(nèi)部結(jié)構(gòu)、電路版圖及層次等,最后提取門級(jí)網(wǎng)表,獲得芯片的設(shè)計(jì)方案。攻擊者常以此作為功耗攻擊的輔助手段,獲得電路的設(shè)計(jì)細(xì)節(jié),從而判斷電路的邏輯功能,提高功耗攻擊的效率。近年來,提出了一種通過電路偽裝抵抗逆向攻擊的方法,即通過隱藏電路版圖中的物理細(xì)節(jié),掩蓋電路的邏輯功能。如虛擬孔技術(shù)[4-5]、傳輸管閾值損失技術(shù)[6-7]等。

功耗攻擊[8-10]是密碼芯片遭遇的較常見且極具威脅性的攻擊方式。利用芯片運(yùn)行時(shí)所泄露的功耗信息,并對(duì)功耗與密碼算法進(jìn)行相關(guān)性分析,得到算法密鑰。目前,抗功耗攻擊的常用方法是使電路的功耗恒定,消除兩者的相關(guān)性關(guān)系。

電流型CMOS 電路具有功耗低、邏輯簡單等優(yōu)點(diǎn)[11-12],并且不同門電路之間具有相似的電路結(jié)構(gòu),非常有利于電路偽裝,具有抗逆向攻擊的優(yōu)勢(shì)。同時(shí),已有的抗攻擊電路研究大多集中在電壓型電路,隨著電流型CMOS 電路的不斷發(fā)展,設(shè)計(jì)抗逆向攻擊和抗功耗攻擊的電流型CMOS 電路具有必要性。

1 電路偽裝與功耗恒定

1.1 電路偽裝

電路偽裝的核心是偽裝邏輯門,即將幾種不同邏輯功能的門電路設(shè)計(jì)成相同的電路結(jié)構(gòu),具有“看”似相同的線路布局,從而讓攻擊者無法通過光學(xué)顯微鏡提取門級(jí)網(wǎng)表信息,進(jìn)而抵抗基于圖像提取的逆向攻擊。如圖1 所示[13],標(biāo)準(zhǔn)NAND 門電路與標(biāo)準(zhǔn)NOR 門電路版圖的區(qū)別清晰可辨。而偽裝的NAND 與NOR 門電路,在版圖上無法被準(zhǔn)確區(qū)分,起混淆邏輯作用,增加了攻擊者分析電路邏輯功能的難度,從而達(dá)到防御逆向攻擊的目的。

偽裝邏輯門設(shè)計(jì),主要利用了虛擬孔技術(shù),即版圖中的接觸孔可能是真實(shí)連接的,也可能是虛擬連接的,令攻擊者無法得知其準(zhǔn)確配置。通過將真實(shí)連接與虛擬連接的接觸孔相互混合,就可用相同的電路結(jié)構(gòu)設(shè)計(jì)出不同功能的偽裝門電路,即接觸孔的配置決定了該偽裝門的邏輯功能。

1.2 功耗恒定

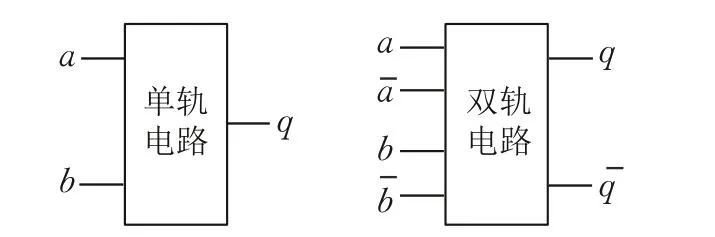

功耗恒定是一種較為常見的抵抗功耗攻擊的方法。實(shí)現(xiàn)功耗恒定的常用設(shè)計(jì)方法是雙軌預(yù)充電技術(shù)(dual rail pre-charge,DRP)[14-15],即將電路的運(yùn)行周期分為預(yù)充電和求值2 個(gè)階段,且1 個(gè)雙軌電路由2 個(gè)單軌電路組合而成,有2 個(gè)輸出端,如圖2 所示。當(dāng)1 對(duì)輸入信號(hào)到達(dá)時(shí),若電路處于預(yù)充電階段,則2 個(gè)輸出信號(hào)均為低電平0。若處于求值階段,則2 個(gè)輸出信號(hào)為正常的互補(bǔ)運(yùn)算值。因此,當(dāng)電路從預(yù)充電階段進(jìn)入求值階段時(shí),無論輸入信號(hào)為何值,2 個(gè)輸出信號(hào)中有且僅有1 個(gè)發(fā)生從低電平到高電平(0→1)的跳變。當(dāng)電路從求值階段進(jìn)入預(yù)充電階段時(shí),2 個(gè)輸出信號(hào)中也有且僅有1 個(gè)發(fā)生從高電平到低電平(1→0)的跳變,即輸出信號(hào)的跳變頻率恒定,此為功耗恒定的理論基礎(chǔ)。

圖2 單軌電路與雙軌電路結(jié)構(gòu)示意Fig.2 Structure of single rail circuit and double rail circuit

2 基于虛擬孔的電流型邏輯電路

2.1 電路設(shè)計(jì)

電流型CMOS 電路的不同門電路具有相似的電路結(jié)構(gòu),非常適合偽裝邏輯門設(shè)計(jì)。如圖3 所示[11],電流型CMOS 與非門、或非門以及非門的電路結(jié)構(gòu)非常相似,只需改變MOS 管的寬長比就可實(shí)現(xiàn)不同的邏輯功能。

圖3 電流型CMOS 門電路[11]Fig.3 Current-type CMOS gate[11]

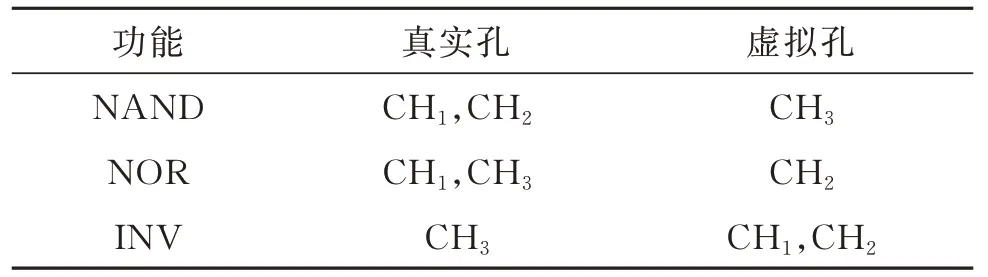

利用虛擬孔技術(shù),即通過真實(shí)孔與虛擬孔相混合的方式配置版圖接觸孔,實(shí)現(xiàn)用一種電路結(jié)構(gòu)完成與非、或非以及非門3 種邏輯功能,構(gòu)成布爾邏輯完備集。提出了基于虛擬孔的電流型邏輯(dummy contacts current-mode logic,DCCML),其電路結(jié)構(gòu)如圖4 所示。圓圈處為接觸孔所在位置,真實(shí)孔與虛擬孔的配置如表1 所示。當(dāng)CH1,CH2為真實(shí)孔,CH3為虛擬孔時(shí),實(shí)現(xiàn)NAND 功能;當(dāng)CH1,CH3為真實(shí)孔,CH2為虛擬孔時(shí),實(shí)現(xiàn)NOR 功能;當(dāng)CH3為真實(shí)孔,CH1,CH2為虛擬孔時(shí),實(shí)現(xiàn)INV 功能。這種電路設(shè)計(jì)方法,使得攻擊者無法得到該電路接觸孔的具體配置,無法分辨電路的邏輯功能,起混淆邏輯作用,增大分析難度。

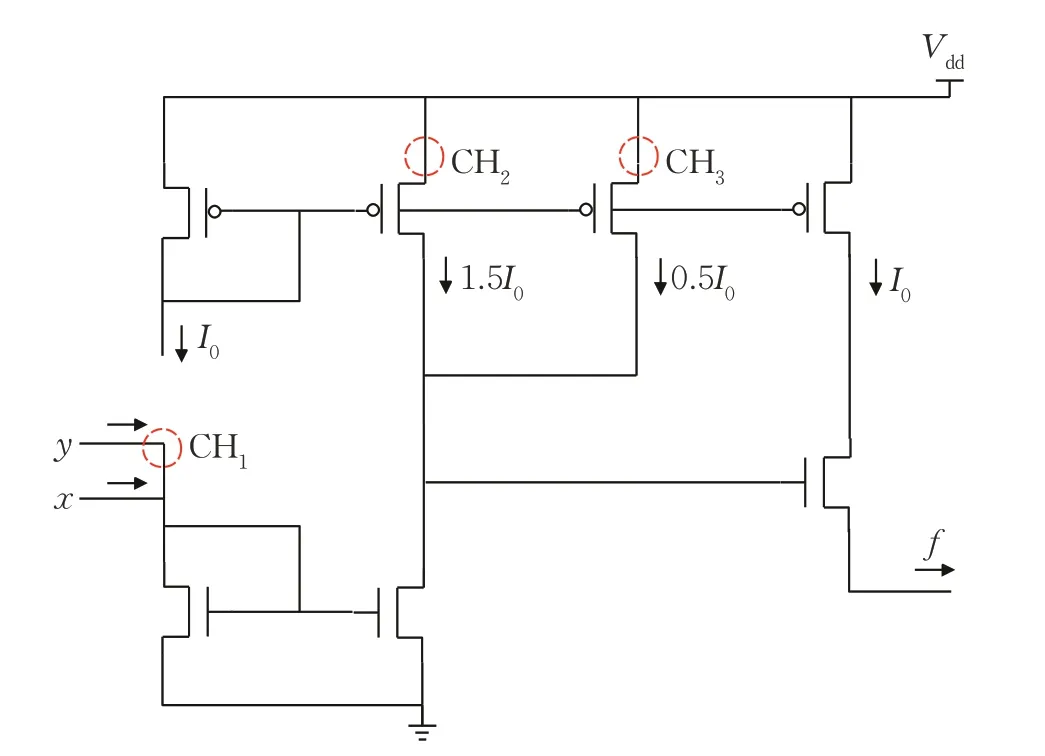

表1 接觸孔配置Table 1 Contact hole configuration

圖4 DCCML 電路Fig.4 DCCML circuit

2.2 邏輯功能實(shí)驗(yàn)

對(duì)所設(shè)計(jì)的DCCML 電路,用Hspice 軟件,0.18 μm 工藝參數(shù)進(jìn)行模擬,0 μA 代表邏輯值0,10 μA 代表邏輯值1,其仿真波形如圖5 所示,結(jié)果表明,該電路結(jié)構(gòu)邏輯功能正確。因此,只需對(duì)接觸孔進(jìn)行不同配置,就可利用相同的電路結(jié)構(gòu)執(zhí)行不同的邏輯功能,從而抵抗逆向攻擊。

圖5 DCCML 電路輸出波形Fig.5 Output waveform of DCCML circuit

3 雙軌預(yù)充電電流型混淆邏輯(DCMOL)電路設(shè)計(jì)

將DCCML 電路與雙軌預(yù)充電技術(shù)相結(jié)合,設(shè)計(jì)了一種既可抵抗逆向攻擊,也可抵抗功耗攻擊的電路,提出了雙軌預(yù)充電電流型混淆邏輯(DRP current-mode obfuscation logic,DCMOL)電路,其單軌電路如圖6 所示。與圖4 相比,增加了1 個(gè)PMOS 管P1和1 個(gè)NMOS 管N1,并在該處放置時(shí)鐘信號(hào),其目的是使電路根據(jù)時(shí)鐘信號(hào)的取值進(jìn)入預(yù)充電階段或求值階段。當(dāng)時(shí)鐘信號(hào)CLKA 為低電平時(shí),進(jìn)入預(yù)充電階段,P1管導(dǎo)通,N1管截止,電路輸出與地相連,從而輸出低電平0。當(dāng)時(shí)鐘信號(hào)CLKA 為高電平時(shí),電路從預(yù)充電階段進(jìn)入求值階段,N1管導(dǎo)通,P1管截止,之后根據(jù)接觸孔的不同配置,在求值階段分別運(yùn)行NAND、NOR 或INV 邏輯。接觸孔的配置如表1 所示。

圖6 DCMOL 單軌電路Fig.6 DCMOL single-rail circuit

將2 個(gè)完全相同的DCMOL 單軌電路進(jìn)行組合,構(gòu)成DCMOL 結(jié)構(gòu),如圖7 所示。輸入信號(hào)(x,y)與(a,b)之間構(gòu)成表2 所示的對(duì)應(yīng)取值關(guān)系,即當(dāng)(x,y)的取值為(0,0)時(shí),(a,b)的取值應(yīng)為(1,1),其對(duì)應(yīng)關(guān)系也可由a=b=----------x+y 運(yùn)算得到。此設(shè)計(jì)使得求值階段DCMOL 結(jié)構(gòu)的2 個(gè)輸出信號(hào)是互補(bǔ)的,從而令信號(hào)翻轉(zhuǎn)率恒定,實(shí)現(xiàn)功耗恒定。

表2 2 組輸入信號(hào)的對(duì)應(yīng)取值關(guān)系Table 2 Corresponding value of two groups of input signal

表3 同類型邏輯結(jié)構(gòu)實(shí)現(xiàn)的或非門功耗恒定性能對(duì)比Table 3 Comparison of constant power consumption performance of NOR gates implemented by the same type of logic structure

圖7 DCMOL 結(jié)構(gòu)Fig.7 DCMOL structure

4 實(shí)驗(yàn)結(jié)果與分析

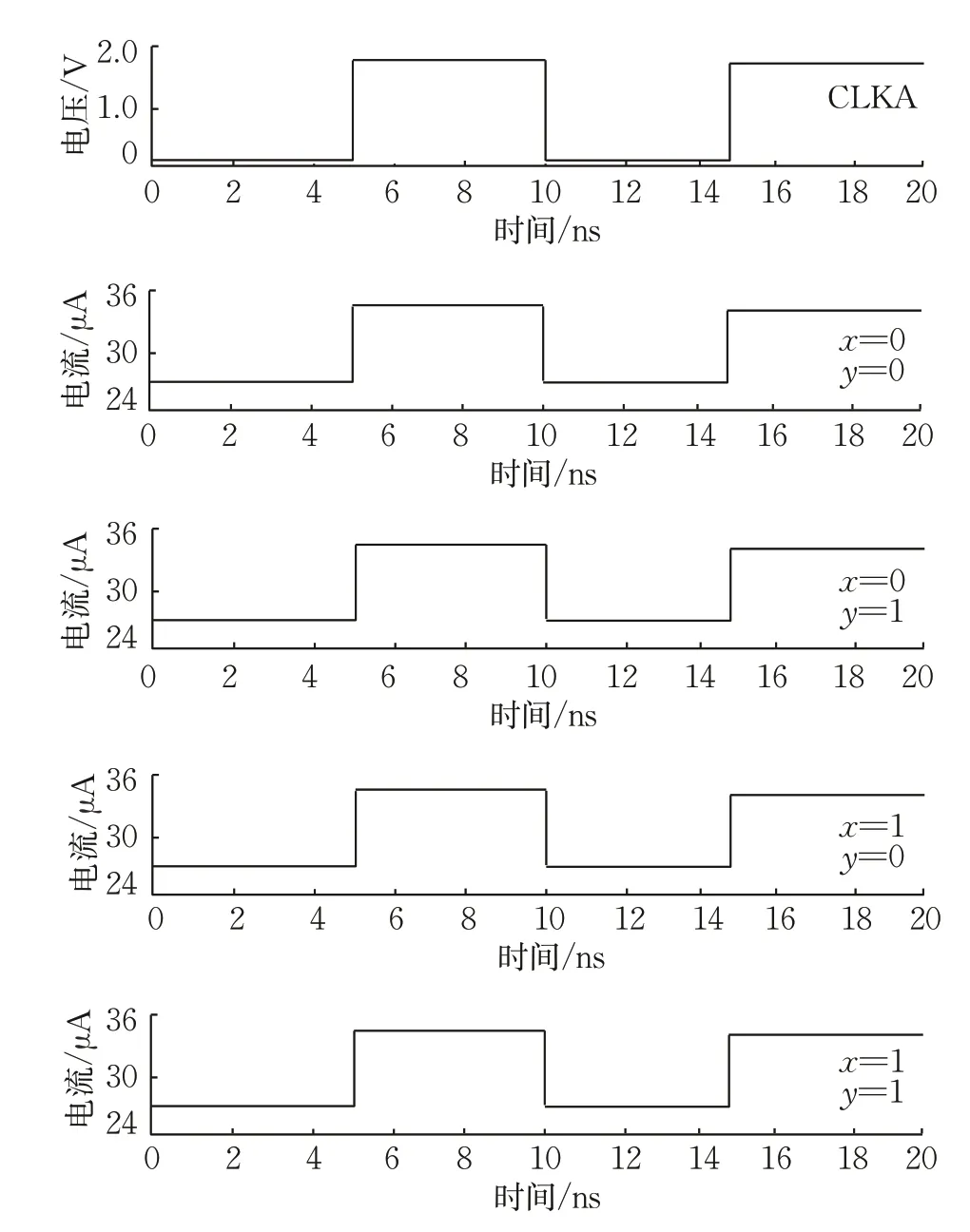

將基于DCMOL 結(jié)構(gòu)得到的與非門、或非門以及非門,利用Hspice 軟件、0.18 μm 工藝參數(shù)進(jìn)行實(shí)驗(yàn),用Vdd端的電流數(shù)據(jù)評(píng)估計(jì)算功耗的變化。利用接觸孔的不同配置實(shí)現(xiàn)3 種邏輯的門電路,實(shí)驗(yàn)結(jié)果如圖8 所示。其中,在0~5 和10~15 ns 時(shí),電路為預(yù)充電階段,在5~10 和15~20 ns 時(shí),電路為求值階段,共運(yùn)行2 個(gè)周期。由圖8 可知,3 個(gè)門電路的電源端波形一致,即攻擊者無法通過功耗分辨門電路的邏輯功能。并且,無論輸入信號(hào)如何取值,電流曲線(功耗變化)近似相同,即功耗與數(shù)據(jù)之間的相關(guān)性在一定程度上被消除了。

圖8 DCMOL 結(jié)構(gòu)電源端電流波形Fig.8 The current waveform of the power supply terminal of the DCMOL structure

為驗(yàn)證邏輯電路功耗的恒定性以及電路運(yùn)算數(shù)據(jù)與功耗之間的相關(guān)性程度,通常采用標(biāo)準(zhǔn)化能量偏差(normalized energy deviation,NED)[16]進(jìn)行評(píng)估。其定義為:

其中,E 為邏輯電路在一個(gè)運(yùn)算周期內(nèi)所產(chǎn)生的功耗值的集合,NED 的取值范圍為[0,1],值越小其功耗恒定性和抗功耗攻擊的性能越好。

為使測(cè)試結(jié)果更接近實(shí)際工作情況,考慮電壓波動(dòng)以及溫度變化對(duì)電路性能的影響,設(shè)置5 種實(shí)驗(yàn)環(huán)境[5]:(1)TYP(typical),工作電壓與標(biāo)準(zhǔn)電壓相同,為1.8 V,溫度為25 ℃;(2)BCF(best case fast),工作電壓比標(biāo)準(zhǔn)電壓高10%,溫度為-40 ℃;(3)WCS(worst case slow),工作電壓比標(biāo)準(zhǔn)電壓低10%,溫度為125 ℃;(4)TL(typical leakage),標(biāo)準(zhǔn)電壓,溫度為125 ℃;(5)ML(maximal leakage),工作電壓比標(biāo)準(zhǔn)電壓高10%,溫度為125 ℃。

5 結(jié)論

通過虛擬孔技術(shù)設(shè)計(jì)的DCCML 電路可在同一電路結(jié)構(gòu)下執(zhí)行與非、或非以及非門3 種邏輯功能,攻擊者在未獲得接觸孔配置的情況下無法分辨電路的邏輯功能,從而起混淆邏輯的作用,可有效防御逆向攻擊。在此基礎(chǔ)上設(shè)計(jì)了DCMOL 結(jié)構(gòu),在5 種實(shí)驗(yàn)環(huán)境下,NED 均低于0.37%,表現(xiàn)出較好的功耗恒定性。經(jīng)實(shí)驗(yàn)驗(yàn)證,DCMOL 結(jié)構(gòu)能有效抵抗逆向與功耗聯(lián)合攻擊。