基于FPGA 和ARM 內核的無線SoC 設計

魏繼清

(電子科技大學 電子科學與工程學院,四川成都,611731)

0 引言

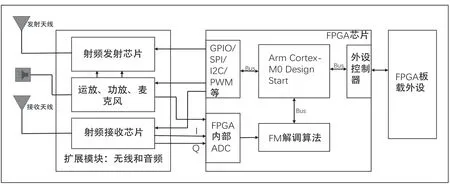

無線SoC 已成為物聯網產業發展的基礎,在現代信息社會中占有越來越重要的地位。但由于課程體系等多方面的原因,同時熟悉無線通信和SoC 設計的人才極為稀缺。本文基于ARM Cortex-M0 處理器在FPGA 上構建具備無線通信基帶信號處理的片上系統,配合控制外圍擴展電路實現FM 通信信號的調制解調等處理。在此基礎上增加適當的功能以滿足特定的物聯網應用,使系統具有實用性、可演示性和創新性,同時兼顧了系統靈活性、可移植性、通用性的要求[1]。該系統的總體設計框圖如圖1 所示。

圖1 無線SoC 系統框圖

1 無線SoC 系統

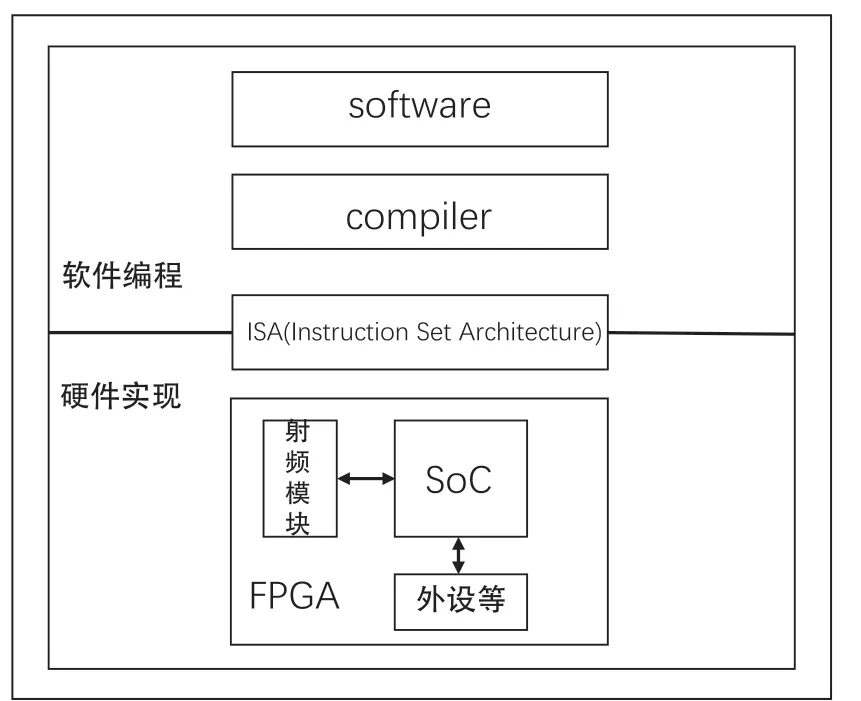

由圖1 可知,將ARM Cortex-M0 內核移植到FPGA上并在FPGA 上構建好硬件系統后,再與射頻擴展模塊、FPGA 板載外設模塊相連接即可構成無線SoC 系統的硬件部分,還需軟件和硬件協同,即可構成完成的無線SoC,二者之間通過指令集架構搭建起橋梁,如圖2 所示。

圖2 軟硬件開發層次

整個系統的開發流程為:

(1)將ARM Cortex-M0 軟核移植到FPGA 芯片上;

(2)使用Verilog 硬件描述語言搭建SoC 系統,包括搭建外設驅動、編寫基帶信號處理IP、連接射頻擴展模塊與外設模塊等;

(3)在集成開發環境keil 中編寫軟件代碼,生成十六進制機器碼;

(4)將機器碼下載至FPGA 中的ARM 內核中,進行仿真;

(5)燒錄到FPGA 中并調試。

其中的軟件控制流程為:該系統上電復位以后,初始化所有外設并打開中斷,然后通過SPI 模塊與射頻接收芯片通信,來選擇接收的頻點,接著將接收到的FM 模擬信號送入AD 模塊轉換為數字信號,在基帶信號處理IP 中進行FM解調,將解調后得到的數字信號經DA 轉換后送入音頻輸出電路播放;……