基于FPGA的DDS信號發生器設計

董殿國,侯文

(中北大學 信息與通信工程學院,山西太原,030051)

0 引言

隨著現代電子技術的飛速發展,直接數字頻率合成DDS技術逐漸被廣泛使用,從其技術理論上看,具有靈活性高、變頻速度快、變頻簡單等優點。從實際效果來看,變頻時分辨率高,相位噪聲低,電路集成度高、頻率穩定等優點。該技術已經逐漸被應用到現代雷達、導航、遙感、現代儀器儀表等關鍵領域。

使用DDS技術產生任意頻率波形的方案主要有三種。第一種是直接使用高性能專用DDS集成電路芯片,比如AD9833,此種方案的優點是產生的波形頻率準確,變頻時分辨率高,直接使用通訊協議控制輸入。缺點是,可以產生的波形類型受限,只有特定的幾種,且內部配置靈活性很低。第二種是使用單片機實現DDS技術,此種方案在低頻時配置較為簡單,易于實現,在中高頻時配置容易受到其他模塊影響,嚴重影響波形頻率精度。第三種是基于現場可編程門陣列FPGA來實現,此種方案靈活性較高,配置簡單,易于實現,且變頻范圍廣,分辨率高,唯一缺點就是,浪費FPGA內部未使用資源,造價高昂[1]。

1 DDS基本原理和核心設計

■1.1 DDS基本原理

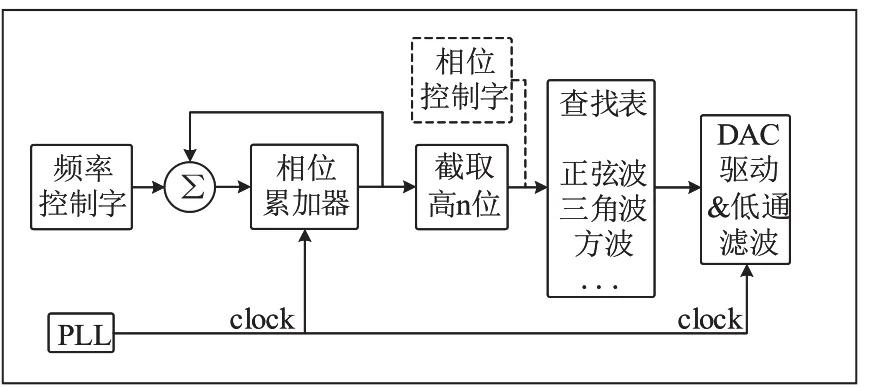

DDS技術原理框圖如圖1所示,主要有以下關鍵幾部分組成,N位相位累加器、頻率控制字、相位控制字、ROM查找表和時鐘源等。

圖1 DDS結構原理圖

相位累加器在高頻時鐘下以頻率控制字的字長K做累加。累加后的相位累加器值通過高位截取后變為相位控制字,相位控制字即為查找表的地址。在查找表中即可找到對應波形的多位數字輸出值。這就是DDS基本工作原理。若要輸出波形,將輸出的多位二進制數字輸出通過D/A轉換輸出對應的模擬電壓信號,再通過一個低通濾波器輸出平滑的曲線[2]。

■ 1.2 DDS核心設計

若要實現更高的頻率分辨率和精度,共有兩種方式,第一,將查找表中的波形數據取的分辨率更高,取樣點的數據更多,這就意味著增加等倍的存儲空間;第二,增加相位累加器的位數。事實上,典型的DDS系統會使用非常“長”位數的相位累加器,比如28位、32位甚至36位,來實現高精度和高分辨率的信號輸出頻率。在FPGA內部所使用的硬件資源來看,只是多使用幾個寄存器,但是對其內部資源來講,影響微乎其微。但是從其實際意義上看,可以大大提高其頻率的精度和分辨率[3]。

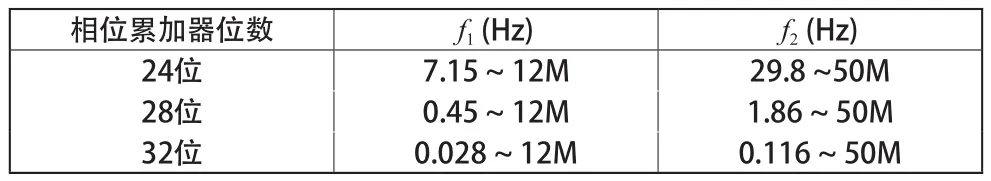

表1中,f1為外部時鐘輸入經過倍頻后的輸出頻率為120MHz,f2為外部時鐘輸入經過PLL倍頻后的輸出頻率為500MHz,波形可調的最低頻率即為頻率的分辨率。

表1 不同情況下頻率可調節范圍和分辨率

如表1所示,相位累加器位數更高,其對應的頻率分辨率越高,系統主頻經過倍頻后的頻率越高,輸出波形的上限頻率越高。

需要注意的是,查找表地址為8位,比如當f1=120MHz時候,在不同累加器位數下,其可調的波形分辨率不同,但是120M/28=468 75kHz是一個臨界值,當輸出頻率小于等于468 75kHz時候,輸出的波形特征則可以完全還原查找表中的波形數據點;當輸出的波形頻率大于468 75kHz時候,頻率越高,輸出的波形無法還原查找表中的波形數據點,還原度越來越低,波形特征越來越不明顯。同樣的對于f2=500MHz時候,500M/28≈1 95MHz也是可以保持原查找表中波形數據點的最大頻率[4]。

2 系統硬件設計

■2.1 硬件整體方案

函數信號發生器的硬件系統主要包括MCU控制電路,FPGA構成的DDS發生器、DAC轉換和低通濾波電路,及一些用于輸入輸出的器件等。

按鍵輸入和LCD輸出顯示主要由MCU負責控制,MCU然后將輸入的信號運算處理后發送給FPGA,FPGA根據輸入的各種參數在ROM表中尋址,同時輸出對應控制的波形、頻率和幅度的數字信號,最后經過DA轉換為對應的模擬電壓信號,在經過一個低通濾波器使得模擬電壓信號變得平滑。

■ 2.2 硬件模塊電路

系統的硬件電路主要分為兩個部分,一是系統主控電路,二是DDS信號發生器電路。

系統主控電路包括以STM32F103C8T6為主控的最小系統板、四路用戶按鍵輸入、OLED顯示屏輸出(SPI)、UART通信連接上位機、硬件SPI連接FPGA負責信號數據傳輸,如圖2所示。

圖2 系統主控電路

DDS信號發生器電路,其中的FPGA模塊的核心芯片為Lattice LCMXO2-4000HC-4MG132,其模塊上內置8路輸出LED指示燈、4路按鍵輸入、4路撥碼輸入和兩位數碼管輸出燈資源。DAC芯片采用3PEAK的高速10位DAC芯片3PD5651E,采樣速率125MSPS,CMOS數模轉換器。本系統中采用12MHz的外部晶振經過PLL倍頻為120MHz小于DAC芯片的最大采樣速率,符合使用要求。

3 系統軟件設計

■3.1 MCU程序流程設計

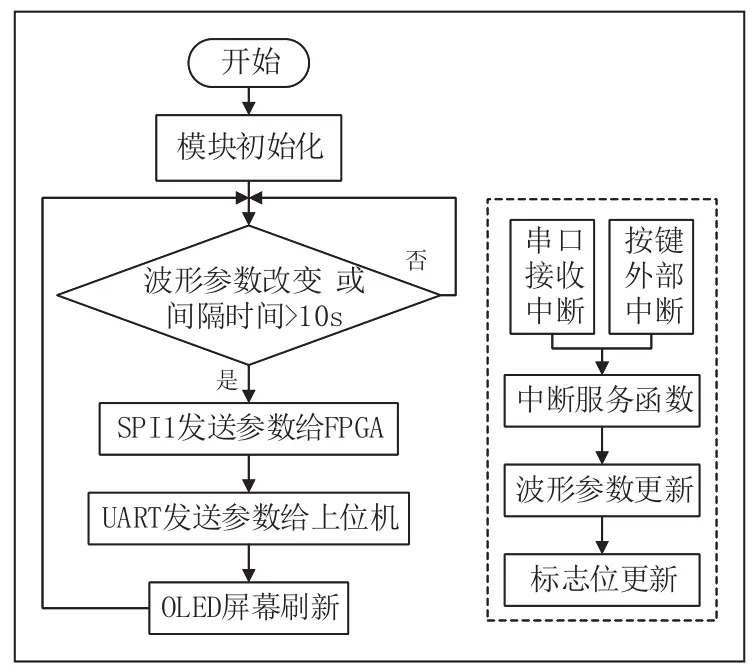

MCU主控制器主要負責系統中各個子任務的任務調度,系統的程序流程如圖3所示,系統上電后先對各個模塊進行初始化,包括串口初始化、OLED顯示屏對應SPI1外設初始化、FPGA的SPI2外設初始化、按鍵和LED輸入輸出初始化等。

圖3 MCU程序設計流程

程序中共有兩個自定義的中斷源,串口接收中斷和按鍵的外部中斷,按鍵的外部中斷用于改變波形的相關參數對應的各個全局變量;而串口接收中斷用于接收來自上位機中的信息,一類是波形參數對應的全局變量同步和參數顯示,另一類是接收自定義波形數據表,并且通過SPI硬件通信接口實時存入FPGA的ROM模塊中。此處有一個關鍵問題,上位機中波形參數的改變與顯示,硬件上波形參數的改變和顯示器的顯示、程序內部波形參數對應的全局變量,以及波形的實際輸出參數,在程序的運行過程中,需要時刻保證這四個模塊中波形參數數據的同步。即先判定數據的輸入輸出屬性,在每一個輸入模塊中添加波形參數更新標志位,實時更新程序中的全局變量,然后再根據參數對應的全局變量,隨即更新參數更新來源模塊之外的參數顯示模塊即可以實現四個模塊的實時同步。

在MCU主程序的主函數中,主任務即為循環判斷波形參數的全局變量是否改變,若改變則對串口傳輸上位機顯示、SPI2對應的OLED顯示屏顯示、SPI1對應的FPGA三個模塊做刷新處理;若未改變,則在間隔時間大于10s時候做刷新處理來降低容錯率。

■3.2 FPGA模塊設計

在整個系統中,FPGA模塊主要負責DDS核心數字變頻技術的實現。主要包括,PLL模塊、SPI通訊接收模塊、數據轉換模塊、DDS累加器模塊、ROM查找表模塊、幅度變換模塊等。總共例化了四個波形數據的ROM,其mif文件通過MATLAB軟件編寫,然后調用IP讀取。但是由于FPGA內部ROM資源限制,只能采用相位截斷方法取高n為作為查詢地址使用。

FPGA的DDS系統模塊設計,主要由SPI通訊接收模塊負責接收MCU傳輸的波形參數,包括波形類型、波形頻率和波形幅度等。然后由數據轉換模塊負責將對應的波形類型,頻率、相位、幅度轉換為相應的頻率控制字和相位控制字,最后將控制字直接輸入DDS累加器模塊中,相位累加器在120MHz的時鐘信號下產生采樣地址,通過波形類型選擇選擇對應的ROM查找表模塊。在ROM模塊中存儲有正弦波、三角波、方波等常見波形的10位數字信號量,根據波形類型查找對應的10位數字信號值并輸出到幅度變換模塊。幅度變換模塊同時根據輸入的幅度設定值來輸出對應的10為數字信號量。

FPGA不同于MCU的串行運行機制,FPGA內部是通過組合邏輯和時序邏輯所構成的并行運行機制的電路模塊。所以在很多需要串行運行的模塊中,就需要添加各種標志位或者狀態機來實現。其中,SPI通信接收模塊、數據轉換模塊、幅度變換模塊都有關鍵的完成標志位,方便開啟下一級模塊使用。

■3.3 上位機軟件設計

上位機軟件使用NI公司的Labview軟件開發,Labview以其使用簡單、圖形化的編程方式、功能模塊封裝度高、對各類硬件采集卡和常見的標準接口適配性高等優點而收到廣大工程師和相關從業者使用。通訊方式使用串行通信UART串口連接,波特率115200,停止位1位,無奇偶校驗位。為了提高調節各類參數和數據同步的響應時間,通訊協議使用自定義方式,第一位功能碼,代表此時調節的參數類型,第二位到第九位為對應的參數值,使用ASCII字符傳輸,第十位為CRC校驗位,校驗數據傳輸。最后一位為結束字符,用于判斷串口傳輸是否完成。

上位機軟件主要分為兩個模塊構成,一是串口的發送和接收模塊,主要在系統的串口控件處發送和接收相關數據;二是數據處理模塊,主要將對應的信號參數數據實時轉換到對應的控件顯示上,或者將對應的控件顯示數據編碼準備發送。

由于在實際測試實驗中所需的實驗波形多種多樣,且FPGA中數據存儲資源有限,所以就需要在上位機軟件中集成可以實時傳輸自定義波形數據的功能,這就是上位機軟件中另一個主要功能,由于Labview軟件可以直接與MATLAB腳本做混合程序設計,所以可以先通過在MATLAB中生成所需要波形的mif數據文件,直接在Labview上位機中導入生成所需的波形數據,完成自定義波形數據導入功能。

4 結果分析

■ 4.1 基本功能實現

信號發生器的幅度和頻率等相關參數可以實現板載的手動調節,同樣也可以連接計算機在上位機的視圖中調節使用。需要注意的是,上位機調節和板載調節并不是簡單孤立的,雙方在不同參數的調節過程中是同步的。

■ 4.2 性能分析

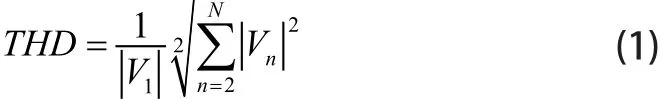

以信號發生器輸出正弦波為例,輸出不同頻率的正弦波來分析其諧波失真(THD)。在此次測量實驗中,使用泰克MDO32頻譜分析儀(模擬通道帶寬1GHz、采樣率2 5GS/s)來測量信號發生器輸出正弦波時,基波之外的高次諧波分量,來計算其諧波失真[5]:

在實驗測量中,無法計算所有的高次諧波分量,只計算了8次諧波分量,所以在(1)式中N=8。實驗測試結果如圖4所示,橫坐標為頻率測試范圍,從1Hz到10MHz。正弦波的THD值在局部上有所波動,但是在整體上趨于平穩。即該信號發生器的總諧波失真≤-10dB。

線性度是描述三角波的一個重要參數。在參數性能測試實驗中,本文使用NI公司的PXI-6115多功能IO采集卡(最大采樣率10MS/s)采集三角波在不同頻率下的波形數據樣點,并計算三角波在不同頻率下的線性度。

在三角波的線性度性能測試實驗中,標定了三角波的對稱性為50%,幅值為3Vpp,頻率從1Hz~1MHz范圍,采集其樣點數據,并做數據分析,計算其線性度。從增長趨勢上來看,信號的頻率越高,其線性度越差,但是從頻率的整體范圍上來看,其線性度一直保持在1%以下。符合系統預期的三角波線性度要求。

■ 4.3 性能總結

信號發生器的最高頻率以正弦波輸出的最高頻率為12MHz;DAC芯片的采樣率為125Msps,但是FPGA的內部主頻經過PLL倍頻后為120MHz,所以該信號發生器的采樣率為120MSa/s;FPGA的數字信號量輸出為10bits,且DAC芯片也為10bits,則信號發生器的垂直分辨率為10bits,系統內置常見的波形,正弦波、三角波、方波等,但是可以根據需要,重新生成任意波形數據樣點保存后并輸出。

5 結束語

本文基于DDS技術,使用MCU和FPGA聯合設計的信號發生器,經過實驗各種性能測試,結果表明,該信號發生器精度高,穩定可靠,噪聲小,可以在各種實驗室和工業場合使用。但是,也存在波形幅度較小和頻率較高時,波形失真明顯,需要進一步改進。